# 11<sup>th</sup> INTERNATIONAL SYMPOSIUM on POWER ELECTRONICS - Ee 2001

XI Međunarodni simpozijum Energetska elektronika – Ee 2001 NOVI SAD, YUGOSLAVIA, OCT. 31 – NOV. 2, 2001

# A Novel 10kW 2-U Three-Phase Unity Power Factor Rectifier Module

#### Johann Miniböck

m-pec

Power Electronics Consultant

Purgstall 5

A-3752 Walkenstein

AUSTRIA

miniboeck@t-online.at

#### Johann W. Kolar

Swiss Federal Institute of Technology (ETH) Zurich Power Electronic Systems Laboratory ETH-Zentrum/ETL/H22 CH-8092 Zurich/SWITZERLAND Phone: +41-1-632-2834 kolar@lem.ee.ethz.ch

Abstract: In this paper the current stress on the power components a direct three-phase boost-type unity power factor rectifier is analyzed in order to provide a basis for a system design under restriction of the height to 2-U. The conduction losses of the power semiconductors are calculated using analytical approximations of the average and rms values of the component currents; the switching losses are taken from previous experimental investigations. Based on this data an overview of the estimated power losses is given for the rectifier system for 10.5kW/800VDC output and 320V/400V/480V/530V (rms, line-to-line) mains voltage and the corresponding efficiency figures are calculated. Finally, topics of the continuation of the research are identified as, e.g., the realization of a prototype in order to verify the theoretical results experimentally also for unbalanced mains voltage conditions and with non-ideal components such as nonlinear input inductors employing iron powder cores.

# 1. INTRODUCTION

Modern high-power telecom power supply modules are typically designed for a rated output power of  $P_{O,max} = 48 \text{V} \cdot 200 \text{A} = 10 \text{kW}$  and show a two-stage topology, where a three-phase high power factor rectifier does supply an output-side DC/DC converter.

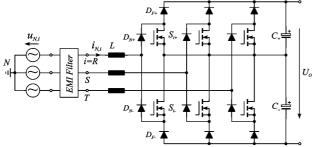

**Fig.1**: Basic structure of the power circuit of the three-phase six-switch three-level boost-type unity power factor rectifier as proposed in [1].

The rectifier system shown in **Fig.1** can be considered as a first step in the development of the well known VIENNA Rectifier [2]. The six-switch topology

can be thought to be derived from the VIENNA Rectifier topology by replacing the four-quadrant switch per phase by two individual switches and series connected diodes. This does result in increased gate drive effort and reduced switch utilization but, as a more detailed analysis shows, the efficiency and the power factor of the system depicted in Fig.1 is very close to the high performance of the VIENNA Rectifier.

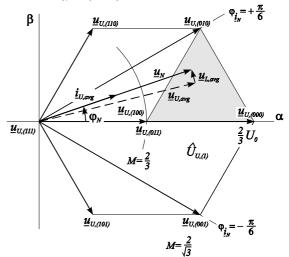

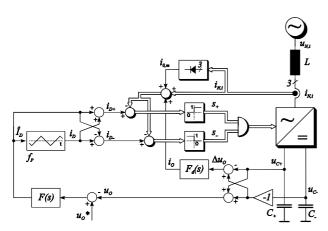

The space vectors of the input phase voltages  $u_U$  [3] of the three-level rectifier are shown in **Fig.2**. The system shows for a given input voltage a required output voltage level of  $U_O \ge \sqrt{3} \cdot \hat{U}_N$  ( $\hat{U}_N$  denotes the peak value of the input phase voltage) which corresponds to the modulation limit  $M_{max} = ^2/\sqrt{3}$  (cf. (2)). However, one does not have to employ a space vector modulation technique for the input current control. An average current mode control in combination with a triangular-shaped carrier signal and a mains voltage pre-control or, according to [4], a multiplier-free approach (cf. **Fig.3**) does allow to achieve comparable performance. The rectifier, although utilizing six switches, does employ only three gating signals, i.e.  $s_{i+} = s_{i-} = s_i$ , (i=R, S, T).

**Fig.2:** Rectifier input voltage space vectors available for input current control (cf. Fig. 2 in [3]).

**Fig.3:** Block diagram of the output voltage and multiplier-free input current control (cf. Fig.I.6(c) in [4]).

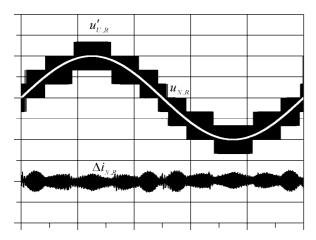

According to **Fig.4** the rectifier shows a nearly constant peak to peak value of the ripple of the input phase currents during a mains fundamental period due to the high number of switching states and/or input voltage space vectors available for current control.

**Fig.4:** Time behavior of a mains phase voltage  $u_{N,R}$ , of the equivalent rectifier input phase voltage  $u'_{U,R}$  (cf. Fig.2 in [5]) and of the ripple component  $\Delta i_{N,R}$  of the mains phase current  $i_{N,R}$  (simulation results).

In the following in **section 2** the average and rms current stresses on the power components of the rectifier system are calculated in analytical form. **Section 3** shows the dimensioning of the rectifier system for an input line-to-line voltage range of  $U_{N,ij}=320...530 \mathrm{Vrms}$  and an output power level of  $P_O=10.5\mathrm{kW}$  as required for supplying a 10kW output DC/DC converter module with an estimated efficiency of  $\eta_{DC/DC}\approx95\%$ . Finally, a photo of a laboratory model is shown in **section 4** and topics to be investigated in the continuation of the research are compiled.

# 2. STRESSES ON THE COMPONENTS

In the following the average and the rms values of the current stresses on the power semiconductor components are calculated as required for the calculation of the conduction losses. Simple analytical approximations are derived which can be used beyond the scope of this paper for the dimensioning of the power components of the rectifier. We assume:

- a purely sinusoidal phase current shape;

- ohmic fundamental mains behavior;

- no (neglectable) mains frequency voltage drop across the boost inductors required for the sinusoidal shaping of the input current;

- constant switching frequency;

- linear behavior of the boost inductors (inductance not dependent on the input current level.

For characterizing the modulation we define a modulation index

$$M = \frac{\hat{U}_U}{\frac{1}{2}U_O} \approx \frac{\hat{U}_N}{\frac{1}{2}U_O} \tag{1}$$

which according to Fig.2 shows a maximum value of

$$M_{\text{max}} = \frac{2}{\sqrt{3}}.$$

(2)

For a first estimation of the core losses of an input inductor an iron powder core and a modulation index M = 1 are assumed. According to [5] we then have for the normalized rms value of the ripple current

$$\Delta I_{N,rms,n} = \frac{\Delta I_{N,rms}}{\Delta i} = 0.075. \tag{3}$$

For a pulse frequency of  $f_P = 1/T_P = 50 \text{kHz}$ , an inductance value of  $L = 225 \mu\text{H}$ , and an output voltage of  $U_O = 800 \text{V}$  this results in

$$\Delta i = \frac{U_o T_p}{8L} = 8.88A\tag{4}$$

and/or in an rms value of current ripple of

$$\Delta I_{N,rms} = 0.075 \cdot 8.88 = 667 \,\text{mA} \,.$$

(5)

For  $L = 225\mu H$  this results in an rms value of the ripple of the flux linkage of

$$\Delta \Psi_{rms} = L \cdot \Delta I_{N,ii,rms} = 150 \mu Vs \tag{6}$$

which is required for a core loss calculation according to [10].

The input inductor is realized in helical wound technology ([11], Schott corporation [12], type number: 33299). The related flux density  $\Delta B_{rms}$  for a number of turns of N=48 and an E-Type core (A=2.28cm<sup>2</sup>) results as

$$\Delta B_{rms} = \frac{\Delta \Psi_{rms}}{NA} = 13.7 \text{mT} = 137 \text{Gauss}.$$

(7)

As a more detailed analysis shows, for the conventional rectifier the inductor ripple current harmonics do occur dominantly at the pulse frequency  $f_1 = f_P$  and at twice the pulse frequency  $f_2 = 2f_P$  in about equal shares [5]. It is interesting that for assuming a linear dependency on the frequency and a quadratic dependency of the core losses on the flux density this does reduce the core losses due to the fact, that for the loss calculation one has to take the squares of half of the total value  $\Delta B_1 = \Delta B_2 = \Delta B/2$ , i.e.:

$$P \sim f_1 \Delta B_1^2 + f_2 \Delta B_2^2 = \frac{3}{4} f_P \Delta B^2$$

(8)

with  $f_{Fe} = f_P = 50 \text{kHz}$ ,  $V_{Fe} = 27.5 \text{cm}^3$  and (7) the iron power loss of one input choke results in approximately

$$P_{Fe} \sim \frac{3}{4} \cdot 9.07 \cdot 10^{-10} \cdot f_{Fe[Hz]}^{1.26} \cdot B_{rms[Gauss]}^{2.11} \cdot V_{Fe[cm^3]}$$

= 503mW

which can easily be tolerated even if the core is not arranged in a forced air-cooled environment.

## 2.1 Current Stresses on the Power Components

The ripple of the inductor current is not considered for the analytical calculation of the average and rms current stresses [6] of the power components.

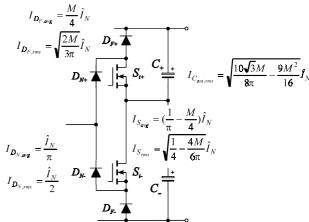

#### **Mains Diodes**

For the average and the rms current stress on the mains diodes  $D_N$  we have

$$I_{D_{N,avg}} = \frac{\hat{I}_N}{\pi} \tag{10}$$

$$I_{D_{N,rms}} = \frac{\hat{I}_N}{2}. \tag{11}$$

#### Free-wheeling Diodes

The average and the rms current stress on the free-wheeling diodes  $D_F$  is

$$I_{D_{F,avg}} = \frac{M}{4}\hat{I}_N \tag{12}$$

$$I_{D_{F,ms}} = \sqrt{\frac{2M}{3\pi}} \hat{I}_N. \tag{13}$$

## **Power Transistors**

The average and the rms current stress on the power transistors  $S_{i+}$  and  $S_{i-}$  is

$$I_{S_{avg}} = \left(\frac{1}{\pi} - \frac{M}{4}\right)\hat{I}_N \tag{14}$$

$$I_{S_{rms}} = \sqrt{\frac{1}{4} - \frac{4M}{6\pi}} \hat{I}_{N} . \tag{15}$$

#### **Output Capacitor**

The rms current stress on the output capacitor is calculated using

$$I_{C_{out,rms}} = \sqrt{\frac{10\sqrt{3}M}{8\pi} - \frac{9M^2}{16}} \hat{I}_N . \tag{16}$$

The results of the analytical calculations are compiled in **Fig.5**.

#### 2.2 Third Harmonic Injection

A zero sequence voltage component, i.e. a third harmonic at the pulse-width modulator input of each phase is employed in order to extend the modulation range  $M \in (0...1)$ , as given for purely sinusoidal modulation, to  $M = M_1 \in (0...2/\sqrt{3})$ .

**Fig.5**: Circuit structure of a bridge leg of the rectifier and current stresses on the power components according to (10) – (16).

Advantageously, this furthermore results in a reduction of the ripple of the input inductor current and in a reduction of the amplitude of the third harmonic of the center point current. The optimum ratio of the amplitude of the third harmonic component to the amplitude of the pulse-width modulator input generating the rectifier input voltage fundamental differs according to the optimization to be performed; e.g. for maximum modulation range we have a ratio of  $M_3/M_1 = \frac{1}{6}$ , for a minimization of the input current ripple rms value  $M_3/M_1 \approx \frac{1}{4}$  and for the elimination of the third harmonic of the center point current  $M_3 / M_1 = \frac{7}{27}$ . The current stress values of the rectifier have been calculated based on purely sinusoidal modulation. As a more detailed analysis shows these current values, however, do hold with sufficient accuracy also in case a third harmonic is injected for extending the modulation range.

# 3. DIMENSIONING, EFFICIENCY

For the dimensioning of the rectifier system the following specifications are defined:

- line-to-line input voltage range  $U_{N,ij} = 320...530 V_{rms}$

- output voltage  $U_O = 800 \text{V}$

- output power of the DC/DC converter supplied by the rectifier stage  $P_{O,DC/DC} = 10$ kW, which results in an input power of the rectifier of  $P_I = 10.85$ kW assuming an efficiency the DC/DC converter of  $\eta_{DC/DC} \approx 95\%$  and a rectifier efficiency of  $\eta_R \approx 97\%$ .

- pulse frequency  $f_P = 50 \text{kHz}$ .

The stresses on the power components and the resulting power losses are listed in **Tab.1**. The characteristic figures compiled in Tab.1 are based on the analytical expressions derived in section 2 and on experimental switching loss data according to [7] and [8]. The efficiency is for an input line-to-line voltage of, e.g.  $U_{N,ij} = 480 \text{V}$  in the range of  $\eta = 97.7\%$  for hard switching.

In case a soft turn-on technique [9] would be employed (which would not cause an increase of the transient turn-off overvoltage, [9]) the efficiency could be improved to  $\eta_S = 98.2\%$ .

| Input power                                           | -              |       |       | 10850 |       | W |

|-------------------------------------------------------|----------------|-------|-------|-------|-------|---|

| Input voltage                                         | $U_{N,l-l}=$   | 320   | 400   | 480   | 530   | V |

| Input current                                         | $I_{N,rms} =$  | 19.58 |       | 13.05 | 11.82 | A |

| Output voltage                                        | $U_O =$        | 800   | 800   | 800   | 800   | V |

| Modulation index                                      | M =            | 0.65  | 0.82  | 0.98  | 1.08  |   |

| Switch current                                        | $I_{S,rms}=$   | 9.24  | 6.14  | 3.79  | 2.39  | A |

| $R_{DS,on} = 0.12\Omega @ 125^{\circ}C$               | $I_{S,avg} =$  | 4.29  | 2.53  | 1.35  | 0.80  | A |

| Conduction loss                                       | $P_{S,C}=$     | 10.24 | 4.52  | 1.72  | 0.68  | W |

| Turn-on $(k_{on}=28.5\mu J/A)$                        | $P_{S,on} =$   | 12.56 | 10.05 | 8.37  | 7.58  | W |

| Turn-off ( $k_{off}$ =8.2 $\mu$ J/A)                  | $P_{S,off} =$  | 3.61  | 2.89  | 2.41  | 2.18  | W |

| 6x Switch total losses                                |                | 158.5 | 104.7 | 75.0  | 62.7  | W |

| Free-wheeling diode current                           | $I_{DF,rms}=$  | 10.31 | 9.22  | 8.42  | 8.01  | Α |

| $U_{DF0} = 0.95 \text{V}, r_{DF} = 24 \text{m}\Omega$ | $I_{DF,avg} =$ | 4.52  | 4.52  | 4.52  | 4.52  | A |

| 6x Free-wheeling diode losses                         | $P_{DF}$ =     | 41.1  | 38.0  | 36.0  | 35.0  | W |

| Mains diode current                                   | $I_{DN,rms} =$ | 13.84 | 11.07 | 9.23  | 8.36  | Α |

| $U_{DN0} = 0.85 \text{V}, r_{DN} = 10 \text{m}\Omega$ | $I_{DN,avg} =$ |       | 7.05  | 5.87  | 5.32  | Α |

| 6x Mains diode losses                                 | $P_{DN}=$      | 56.4  | 43.3  | 35.1  | 31.3  | W |

| Total power semiconductor                             |                | 256.0 | 186.0 | 146.0 | 129.0 | W |

| losses                                                |                |       |       |       |       |   |

| Input choke ( $R_L = 19.5 \text{m}\Omega$ ,           | $P_L$ =        | 28.4  | 20.3  | 16.0  | 14.2  | W |

| $P_{FE} = 2W$ , worst case)                           |                |       |       |       |       |   |

| Output capacitor current                              | $I_{CO,rms} =$ | 12.7  | 9.6   | 6.8   | 4.9   | Α |

| 12x Output capacitor                                  | $P_{CO} =$     | 16.1  | 9.2   | 4.6   | 2.4   | W |

| $330\mu F/450V (R_{ESR}=0.1\Omega)$                   |                |       |       |       |       |   |

| Auxiliary power                                       | $P_{aux} =$    | 30    | 30    | 30    | 30    | W |

| (housekeeping, fans)                                  |                |       |       |       |       |   |

| Snubbers, PCB, var.                                   | $P_{add} =$    | 50    | 50    | 50    | 50    | W |

| distributed losses                                    |                |       |       |       |       |   |

| Total power losses                                    | P =            | 380.5 | 295.6 | 246.6 | 225.6 | W |

| Efficiency                                            | $\eta =$       | 96.5  | 97.3  | 97.7  | 97.9  | % |

| Efficiency with turn-on                               | $\eta_s =$     | 97.2  | 97.8  | 98.2  | 98.3  | % |

| snubber ( $k_{on}$ =0 $\mu$ J/A)                      |                |       |       |       |       |   |

|                                                       |                |       |       |       |       |   |

**Tab.1**: Losses of a 10.85kW/50kHz three-phase rectifier according to Fig.1. The improvement of the overall efficiency in case a turn-on snubber would be employed would be in the range of 0.4 ... 0.7%.

In **Table 2** the semiconductor components employed for the calculation of the efficiency are compiled.

| Part  | Туре                   |

|-------|------------------------|

| S     | Infineon SPW47N60C2    |

| $D_F$ | Int. Rect. HFA25PB60   |

| $D_N$ | ST TYN1040 (Thyristor) |

**Tab.2:** List of power semiconductor components which have been selected as basis for the calculation of the efficiency of the rectifier (cf. Tab.1). Devices  $D_N$  in Fig.1 realized by thyristors which are employed besides rectification for the bridging of the output capacitor precharge resistors after start-up in order to avoid mechanical contacts, i.e. a relay.

#### 4. CONCLUSIONS

As this paper shows the proposed three-phase sixswitch three-level rectifier system is an interesting alternative to the well known VIENNA Rectifier topology. Accordingly, this rectifier concept as well as the VIENNA Rectifier will be further investigated at the ETH Zurich in collaboration with m-pec where the main topics will be:

- practical realization of a rectifier system fitting into an enclosure of 2-U height (cf. **Fig.6**),

- experimental investigation of the power factor, the total harmonic distortion of the phase currents, the system efficiency and of the losses of the power components for different input voltage conditions,

- determination of the power density,

• investigation of the influence of a mains voltage unbalance, of a non-linearity of the boost inductor magnetic cores and of the system behavior in discontinuous inductor current mode as occurring at light load condition.

**Fig.6**: Photo of the prototype of the 10kW 2-U rectifier system. In front: Input choke in helical wound technology [12], right: 2 x 80mm high airflow fans, in the middle on top: control board realized in surface mount technology, in the back: output capacitors 6 x  $330\mu\text{F}/450\text{V}$ , in the left background: auxiliary power supply. Dimensions (without housekeeping, with fans): 230mm x 160mm x 88mm (2-U).

#### 5. REFERENCES

- [1] Zhao, Y., Li, Y., and Lipo, T.A.: Force Commutated Three-Level Boost Type Rectifier. Record of the 28th IEEE Industry Applications Society Annual Meeting, Toronto, Canada, Oct. 2-8, Vol. II, pp. 771-777 (1993).

- [2] Kolar, J. W., and Zach, F. C.: A Novel Three-Phase Utility Interface Minimizing Line Current Harmonics of High-Power Telecommunications Rectifier Modules. Proceedings of the 16<sup>th</sup> IEEE International Telecommunications Energy Conference, Vancouver, Canada, Oct. 30-Nov. 3, pp. 367-374 (1994).

- [3] Kolar, J.W., Drofenik, U., Miniböck, J., and Ertl, H.: A New Concept for Minimizing High-Frequency Common-Mode EMI of Three-Phase PWM Rectifier Systems Keeping High Utilization of the Output Voltage. Proceedings of the 15th IEEE Applied Power Electronics Conference, New Orleans, Feb. 6-10, 2000.

- [4] Miniböck, J., Stögerer, F., and Kolar, J.W.: A Novel Concept for Mains Voltage Proportional Input Current Shaping of a VIENNA Rectifier Eliminating Controller Multipliers. Part I: Basic Theoretical Considerations and Experimental Verification. Proceedings of the 16th IEEE Applied Power Electronics Conference, Anaheim, March 4-8, 2001.

- [5] Kolar, J. W., Stögerer, F., and Nishida, Y.: Evaluation of a Delta-Connection of Three Single-Phase Unity Power Factor Rectifier Systems (Δ-Rectifier) in Comparison to a Direct Three-Phase Rectifier Realization. Part I – Modulation Schemes and Input Current Ripple. Proceedings of the 7<sup>th</sup> European Power Quality Conference, Nuremberg, Germany, June 19-21, pp. 101-108 (2001).

- [6] Kolar, J.W., Ertl, H., and Zach, F. C.: Design and Experimental Investigation of a Three-Phase High Power Density High Efficiency Unity Power Factor PWM (VIENNA) Rectifier Employing a Novel Power Semiconductor Module. Proceedings of the 11<sup>th</sup> IEEE Applied Power Electronics Conference, San Jose, USA, March 3-7, Vol. 2, pp. 514-523 (1996).

- [7] Miniböck, J., Stögerer, F., Kolar, J.W.: Experimental Analysis of the Application of Latest SiC Diode and CoolMOS Power Transistor Technology in a 10kW Three-Phase PWM (VIENNA) Rectifier. Proceedings of the 43<sup>rd</sup>

- International Power Electronics Conference, Nuremberg, Germany, June 19-21, pp. 121-125 (2001).

- [8] Miniböck, J., Stögerer, F., and Kolar, J.W.: Comparative Theoretical and Experimental Evaluation of Bridge Leg Topologies of a Three-Phase Three-Level Unity Power Factor Rectifier. Proceedings of the IEEE Power Electronics Specialists Conference, Vancouver, Canada, June 17-21, Vol. 3, pp. 1641-1646 (2001).

- [9] Mantov, G., and Wallace, K.: Diode Recovery Current Suppression Circuit. Proceedings of the 22<sup>nd</sup> International Telecommunications Energy Conference, Phoenix (AZ), USA, Sept. 10-14, pp. 125-129 (2000).

- [10] **Micrometals:** Iron Powder Cores, Power Conversion & Line Filter Applications. Catalog 4/Issue H, 1995.

- [11]**Shonts, D.:** Improved PFC Boost Choke using a Quasi-Planar Winding Configuration. Proceeding of the 14<sup>th</sup> IEEE Applied Power Electronics Conference, Dallas, Texas, USA, March 14-18, (1999).

- [12]**Schott Corporation:** *HWT Output Inductors 193 Series.* Product Catalog 1998 or www.schottcorp.com.