# Control-Loop Modeling of Multiple-Output Feedback of Forward Converters

Yie-Tone Chen, Dan Y. Chen, Senior Member, IEEE, and Yan-Pei Wu

Abstract—A small-signal model is developed for the forward converter with multioutput feedback. From the model developed, feedback compensation schemes are proposed to stabilize the circuit. The closed-loop circuit performances, such as line regulation, cross regulation, and load regulation are expressed analytically in terms of multiple-loop gains of the system.

#### I. INTRODUCTION

THE forward converter is a commonly used power conversion circuit for commercial power supply applications. The circuit is relatively simple and is capable of providing multiple isolated outputs. In this circuit, the output voltage regulation is normally achieved with two different approaches. In one approach, the main output is regulated by a feedback control, and the auxiliary outputs are controlled by a postregulator such as a linear regulator or a magamp. In the other approach, all of the output voltages are summed and perhaps weighted differently from the feedback signal to control the transistor duty cycle to achieve regulation. The latter is economical and very often provides adequade regulation, it is consequently a popular approach for a low-cost power supply.

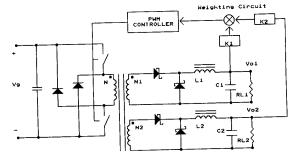

Fig. 1 shows the circuit diagram of a two-output forward converter circuit that employs multiple-output voltages as feedback signal. As popular as it is, the circuit has never been adequately modeled. The focus of this paper is to model the control-loop behavior of this circuit using the conventional small-signal modeling technique [1], [2]. The model provides design-oriented information for stabilizing the control loop and trading off converter performance.

In this paper, Section II deals with the small-signal models of the circuit and the experimental verification of the model. Section III deals with feedback compensation design using the model developed in Section II. Discussion for the case when one output is in discontinuous mode is given in Section IV. Section V concludes the paper.

# II. SMALL-SIGNAL MODEL AND EXPERIMENTAL VERIFICATION

The small-signal model of a buck-derived converter configuration is well documented [3]. Table I summarizes the key control transfer functions, in which  $G_v$  is the input-to-output transfer function,  $\hat{V}_0/\hat{V}_g$ .  $G_d$  is the duty cycle-to-output voltage

Manuscript received March 4, 1992; revised February 16, 1993. Y.-T. Chen and Y.-P. Wu are with Taiwan University, Taipei, Taiwan,

D. Y. Chen is with the Department of Electrical Engineering, Virginia Polytechnic Institute and State University, Blacksburg, VA 24061. IEEE Log Number 9209309.

Fig. 1. The circuit diagram of a two-output forward converter employing two-voltage feedback

TABLE I

CONTROL TRANSFER FUNCTIONS OF A

CONTINUOUS MODE BUCK -DERIVED CONVERTER

$$\begin{split} G_v & \triangleq \frac{\hat{v}_0}{\hat{v}_g} = D \frac{1 + SR_cC}{S^2LC + S[(R_c + R_l)C + L/R_L] + 1} \\ G_d & \triangleq \frac{\hat{v}_0}{\hat{d}} = V_g \frac{1 + SR_cC}{S^2LC + S[(R_c + R_l)C + L/R_L] + 1} \\ Z_0 & \triangleq \frac{\hat{v}_0}{\hat{i}_0} = R_l \frac{(1 + SL/R_l)(1 + SR_cC)}{S^2LC + S[(R_c + R_l)C + L/R_L] + 1} \\ F_m & \triangleq \frac{\hat{d}}{\hat{v}_0} = \frac{1}{V_C} \end{split}$$

$V_P\colon$  The peak voltage of PWM sawtooth waveform  $R_l\colon$  Parasitic resistance of inductor.  $R_c\colon$  The ESR of capacitor,  $D\colon$  duty cycle.

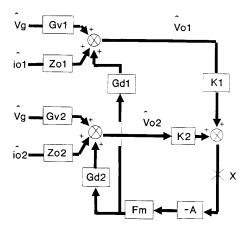

gain,  $\hat{V}_0/\hat{d}$ .  $Z_0$  is the output impedance,  $\hat{V}_0/\hat{I}_0$ , and  $F_m$  is the error voltage-to-duty cycle gain of the duty cycle modulator. This information will be used as the starting point for modeling of the multiple-output feedback forward converters. Fig. 2 shows the control block diagram of Fig. 1. The definitions and the transfer functions used in the diagram are summarized in Table II. This information is derived from the use of Table I and the investigation of the control block diagram shown in Fig. 2. Using the information obtained, the effect of multioutput feedback will be discussed.

#### A. Loop Gain

There are several loop-gain functions involved in this modeling effort,  $T, T_1, T_2, T_{01}$ , and  $T_{02}$ . T is the overall closed-loop gain (which can be measured at point X in Fig. 2). It can be proven that

$$T = AF_m(K_1G_{d1} + K_2G_{d2}) (1)$$

Fig. 2. The control-block diagram of Fig. 1.

# TABLE II THE TRANSFER FUNCTIONS OF CONTROL BLOCK DIAGRAM OF A TWO-OUTPUT FORWARD CONVERTER

$$\begin{split} G_{v1} & \stackrel{\stackrel{\frown}{=}}{\stackrel{\circ}{v_{01}}} = n1 \cdot D \frac{1 + SR_{c1}C_{1}}{S^{2}L_{1}C_{1} + S[(R_{c1} + R_{l1})C_{1} + L_{1}/R_{L1}] + 1} \\ n1 & \stackrel{\frown}{=} N1/N \\ G_{v2} & \stackrel{\stackrel{\frown}{=}}{\stackrel{\circ}{v_{02}}} = n2 \cdot D \frac{1 + SR_{c2}C_{2}}{S^{2}L_{2}C_{2} + S[(R_{c2} + R_{l2})C_{2} + L_{2}/R_{L2}] + 1} \\ n2 & \stackrel{\frown}{=} N2/N \\ G_{d1} & \stackrel{\frown}{=} \frac{\hat{v}_{01}}{\hat{d}} = n1 \cdot V_{g} \frac{1 + SR_{c1}C_{1}}{S^{2}L_{1}C_{1} + S[(R_{c1} + R_{l1})C_{1} + L_{1}/R_{L1}] + 1} \\ G_{d2} & \stackrel{\frown}{=} \frac{\hat{v}_{02}}{\hat{d}} = n_{2} \cdot V_{g} \frac{1 + SR_{c2}C_{2}}{S^{2}L_{2}C_{2} + S[(R_{c2} + R_{l2})C_{2} + L_{2}/R_{L2}] + 1} \\ Z_{01} & \stackrel{\frown}{=} \frac{\hat{v}_{01}}{\hat{i}_{01}} = R_{l1} \frac{(1 + SL_{1}/R_{l1})(1 + SR_{c1}C_{1})}{S^{2}L_{1}C_{1} + S[(R_{c1} + R_{l1})C_{1} + L_{1}/R_{L1}] + 1} \\ Z_{02} & \stackrel{\frown}{=} \frac{\hat{v}_{02}}{\hat{i}_{02}} = R_{l2} \frac{(1 + SL^{2}/R_{l2})(1 + SR_{c2}C_{2})}{S^{2}L_{2}C_{2} + S[(R_{c2} + R_{l2})C_{2} + L_{2}/R_{L2}] + 1} \end{split}$$

where  $K_1$  and  $K_2$  are weighing factors of each loop as shown in Fig. 2.  $T_1$  and  $T_2$  are defined as

$$T_1 \equiv AF_m K_1 G d_1$$

and

$$T_2 \equiv AF_m K_2 G d_2$$

and  $T_{01}$  and  $T_{02}$  are the respective open-loop gains:

$$T_{01} \equiv F_m K_1 G d_1$$

and

$$T_{02} \equiv F_m K_2 G d_2$$

.

It can be seen from (1) and the foregoing definitions that

$$T = T_1 + T_2 = A(T_{01} + T_{02}).$$

Loop gain T affects converter performance such as line regulation (or audiosusceptibility) output impedance and cross

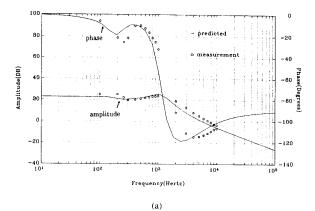

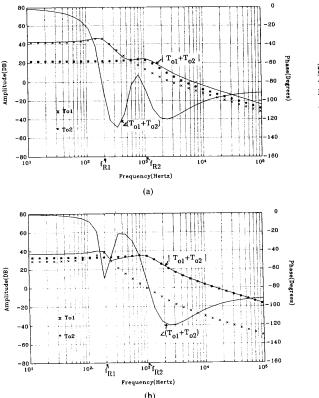

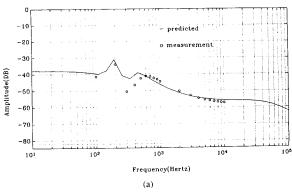

Fig. 3. (a) The Bode plot of open-loop gain  $T_{01}+T_{02}$ . (b) The Bode plot of closed-loop gain T (where  $f_s=50$  KHz,  $C_1=400\,\mu\text{F}, L_1=50$  H,  $R_{c1}=0.14\,\Omega, R_{l1}=0.07\,\Omega, R_{L1}=6\,\Omega, K_1=1.176, V_{01}=12$  V and  $C_2=4000\,\mu\text{F}, L_2=150\,\mu\text{H}, R_{C2}=0.02\,\Omega, R_{l2}=0.13\,\Omega, R_{L2}=2\,\Omega, K_2=0.75, V_{02}=5V$ ).

regulation. These issues are addressed in the following paragraphs. The overall open loop gain  $(T_{01} + T_{02})$  affects the feedback compensation design, discussed in Section III.

Fig. 3 shows that the predicted and the measured loop gains agree very well.

#### B. Line Regulation

It can be proven that the closed-loop line regulations,  $G_{V1,CL}$  and  $G_{V2,CL}$  are related to loop parameters by the following equations:

$$(G_{V1})_{CL} \equiv \frac{\hat{V}_{01}}{\hat{V}_q} \Big|_{\text{closed loop}} = \frac{G_{V1}}{1 + T_1 + T_2}$$

(2)

and

$$(G_{V2})_{CL} \equiv \frac{\hat{V}_{02}}{\hat{V}_g}\Big|_{\text{closed loop}} = \frac{G_{V2}}{1 + T_1 + T_2}.$$

(3)

As it can be seen from (2) and (3), both loop gains  $T_1$  and  $T_2$  contribute to the closed-loop line regulation performance. Therefore, increasing the gain of one feedback path improves the line regulation of both output voltages. The larger the

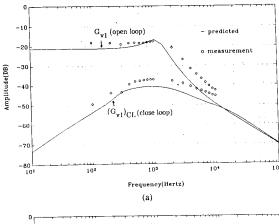

Fig. 4. (a) The Bode plot of  $G_{V1}$  and  $(G_{V1})_{\rm CL}$  (continuous mode). (b) The Bode plot of  $G_{V2}$  and  $(G_{V2})_{\rm CL}$  (continuous mode). (The conditions are the same as Fig. 3.)

overall loop gain T, the better the line regulation performance. Fig. 4 shows the predicted and the measured results of the open-loop and closed-loop  $G_v$ 's. The model agrees well with the measurement results.

#### C. Output Impedance

Output impedance is an indication of the load regulation performance. It can be proven that the closed-loop output impedance  $(Z_{01})_{CL}$  is related to loop parameters by the following equations:

$$(Z_{01})_{CL} \equiv \frac{\hat{V}_{01}}{\hat{i}_{01}} \bigg|_{\text{closed loop}} = \frac{Z_{01}(1+T_2)}{1+T_1+T_2}$$

(4)

and

$$(Z_{02})_{CL} \equiv \frac{\hat{V}_{02}}{\hat{i}_{02}} \bigg|_{\text{closed loop}} = \frac{Z_{02}(1+T_1)}{1+T_1+T_2}.$$

(5)

The physical significances of (4) and (5) are discussed shortly. The discussion is divided into two cases, depending on the relative magnitude of  $T_1$  and  $T_2$ .

Case A: One Gain Function Dominates over the Other: Assuming  $T_1$  dominates, i.e.,  $|T_1| \gg |T_2| \gg 1$ . then (4) and

(5) become, respectively, (6) and (7):

$$(Z_{01})_{CL} = |T_2/T_1|Z_{01} = |K_2Gd_2/K_1Gd_1|Z_{01}$$

(6)

and

$$(Z_{02})_{CL} = Z_{02}. (7)$$

Two conclusions are drawn from (6) and (7):

- 1) Compensation design plays no direct role in load regulation since error amplifier gain A is not involved in the above two equations. Increasing the gain of the error amplifier does not improve load regulation.

- 2) The load regulation of the dominant output is improved by the factor of  $T_{\rm dominant}/T_{\rm nondominant}$  ratio. The load regulation of the much less dominant output is not improved by the use of multioutput feedback.

Case B: Neither Gain Function Dominates, but  $|T_1| \gg 1$ , and  $|T_2| \gg 1$ :

$$(Z_{01})_{CL} = \frac{Z_{01}}{1 + \left| \frac{T_1}{T_2} \right|} = \frac{Z_{01}}{1 + \left| \frac{K_1 G d_1}{K_2 G d_2} \right|}$$

and

$$(Z_{02})_{CL} = \frac{Z_{02}}{1 + \left| \frac{T_2}{T_1} \right|} = \frac{Z_{02}}{1 + \left| \frac{K_2 G d_2}{K_1 G d_1} \right|}.$$

Two conclusions are drawn from the above two equations.

- 1) The load regulation of both output are improved by the use of feedback. However increasing one of the loop gain, e.g.,  $T_1$ , actually degrades the load regulation of the other output, e.g.,  $V_{02}$ . This is true regardless of the overall loop gain T. In other words, the load regulation of both outputs cannot be simultaneously improved even if overall loop T is increased. If  $|T_1| = |T_2|$ , then the output impedance of both outputs is only half reduced by the use of feedback.

- 2) Compensation design plays no direct role in load regulation performance as long as the inequalities are satisfied:  $|T_1| \gg 1, |T_2| \gg 1$ . This conclusion is similar to conclusion 1 drawn in Case A.

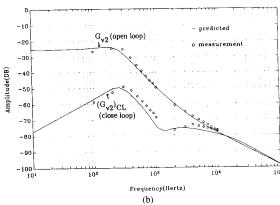

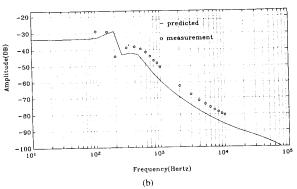

Fig. 5 shows the predicted and the measured results for output impedances. Both agree very well.

#### D. Cross Regulation

Cross-regulation performance is represented by cross-output impedance  $Z_{12}$  and  $Z_{21}$  as defined in the following:

$$Z_{12} \equiv \frac{\hat{V}_{01}}{\hat{i}_{02}} \bigg|_{\text{closed loop}} = \frac{-AF_m K_2 G d_1}{1 + T_1 + T_2} Z_{02}$$

(8)

and

$$Z_{21} \equiv \frac{\hat{V}_{02}}{\hat{i}_{02}} \bigg|_{\text{closed loop}} = \frac{-AF_m K_1 G d_2}{1 + T_1 + T_2} Z_{01}.$$

(9)

The physical significances of (8) and (9) are discussed below. Discussion is again divided into two cases, according to the relative magnitude of  $|T_1|$  and  $|T_2|$ .

Fig. 5. (a) The Bode plot of  $Z_{01}$  and  $(Z_{01})_{\rm CL}$  (continuous mode). (b) The Bode plot of  $Z_{02}$  and  $(Z_{02})_{\rm CL}$  (continuous mode). (The conditions are the same as Fig. 3.)

Fig. 6. (a) The Bode plot of  $Z_{21}$  (continuous mode). (b) The Bode plot of  $Z_{12}$  (continuous mode). (The conditions are the same as Fig. 3.)

Case A. One of the Two Gain Dominates over the Other: Assuming  $|T_1| \gg |T_2| \gg 1$ , then from (8) and (9):

$$Z_{12} = \left(\frac{K_2}{K_1}\right) Z_{02},$$

and

$$Z_{21} = \left(\frac{Gd_2}{Gd_1}\right) Z_{01}.$$

The two conclusions drawn for Case A of the previous section "Output Impedance" are applicable to this case.

Case B: Neither Gain Functions Dominates, but  $|T_1| \gg 1$  and  $|T_2| \gg 1$ :

$$Z_{12} = \left(\frac{Gd_1}{(K_1/K_2)Gd_1 + Gd_2}\right) Z_{02},$$

and

$$Z_{21} = \left(\frac{Gd_2}{Gd_1 + (K_2/K_1)Gd_2}\right)Z_{01}.$$

The two conclusions drawn for Case B of previous section are applicable to this case. Fig. 6 shows the predicted and measurement results. Models agree well with the measurement results.

#### III. CIRCUIT STABILITY AND FEEDBACK COMPENSATION

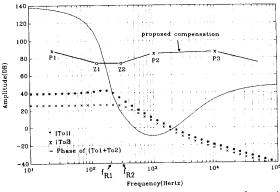

To stabilize the converter circuit, the feedback compensation transfer function, A, must be designed according to the open-loop gain transfer function,  $T_{01}+T_{02}$ . Depending on the relative frequencies and the relative magnitude of  $T_{01}$  and  $T_{02}$ , the open-loop gain function behaves differently. The behavior can be classified into two types to be discussed as follows. Compensation for each type is also suggested.

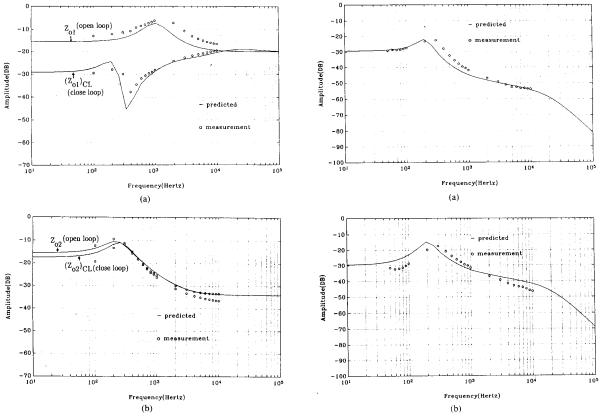

Type I: Widespread resonance frequencies: Within Type I, there are two subtypes, depending on the relative magnitude of  $T_1$  and  $T_2$ .

Type I(A): Noncrossover type. For this subtype, the magnitude of one of the open-loop function  $(T_{01}, \text{ and } T_{02})$  is less than the other for all frequencies. For the convenience of discussion, it is assumed that  $|T_{01}| > |T_{02}|$  for all frequencies. Fig. 7 shwos the Bode plots for such subtype. It can be seen that the phase plot of  $T_{01} + T_{02}$  has two dips. For the case shown in Fig. 7(a), the phase dip at  $f = f_{R2}$  depends on the relative magnitude of  $T_{01}$  and  $T_{02}$  at  $f = f_{R2}$ . The smaller the ratio  $|T_{01}|/|T_{02}|$ , the larger the dip, but the maximum is  $-90^{\circ}$ . The maximum dip at  $f = f_{R1}$  is  $-180^{\circ}$ . For the case shown in Fig. 7(b), the maximum phase dip at either resonance frequency is  $-180^{\circ}$ . Appendix provides proof of the above statements.

(b) Fig. 7. The Bode plot of  $|T_{01}+T_{02}|$  for the noncrossover type.

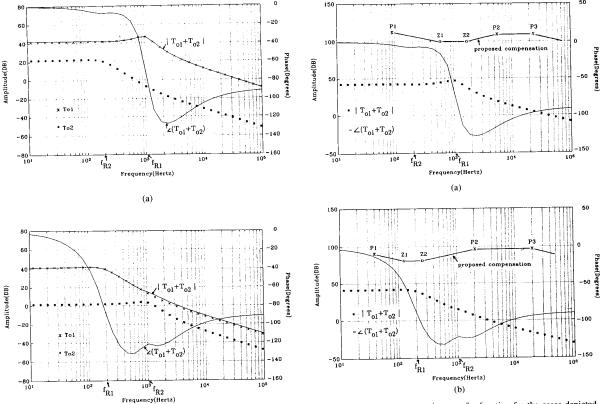

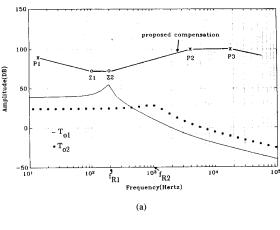

Fig. 8. The proper compensation transfer function for the cases depicted in Fig. 7.

Compensation for Type I(A): Fig. 8 shows the proper compensation transfer function for the cases depicted in Fig. 7. In both cases, the two compensation zeros  $Z_1$  and  $Z_2$  should be placed near the resonance frequency of  $T_{01}$ , the larger of the two loop gain functions, to insure stability. Pole  $P_2$  should be placed near the larger capacitor ESR zero of the two gain functions.

Type I(B): Crossover type. For this subtype, the magnitude plot cross over each other, particularly near one of the resonant frequency. Fig. 9 shows the plots of this subtype, where the phase dip occurs near  $f_{R1}$  and  $f_{R2}$  and both dip could reach maximum of  $-180^{\circ}$ .

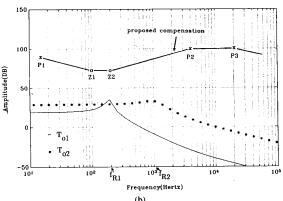

Compensation for Type I(B): Fig. 10 shows a proper compensation pole-zero placement for this subtype. The two zeros should be placed near the lower resonance frequency of the two. Fig. 11(a) shows an example of improper compensation in which the zeros are placed near the higher resonance frequency. Fig. 11(b) indicates a potential instability.

It can be seen from this discussion that decreasing one of the feedback gain may actually destabilize the circuit operation. Take Fig. 7(a), a noncrossover Type I circuit, as an example. The proper compensation is shown in Fig. 8(a). However, if  $K_1$  is decreased while every other parameter is kept constant, then the case of Fig. 7(a) (noncrossover type) becomes the case of Fig. 9(a) (crossover type). A larger phase dip at  $f_{R2}$  results in a potential unstable situation if the compensation

zeros are still placed near  $f_{R1}$  as shown in Fig. 8(a). This phenomenon, however, does not happen in the case of Fig. 7(b). Therefore, when gains  $K_1$  or  $K_2$  are adjusted, the placement of compensation zeros may need a corresponding change.

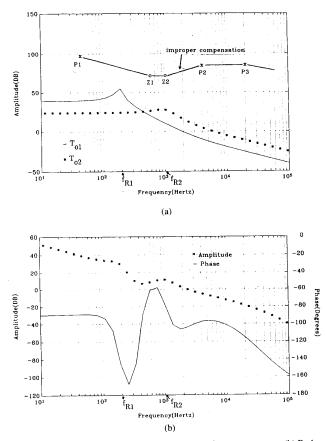

Type II: Close-Together Resonance Frequencies: For this type,  $f_{R1}\cong f_{R2}$ . Fig. 12 shows the Bode plot of such type. The magnitude of  $T_{01}+T_{02}$  is approximately the upper envelop of the two functions  $T_{01}$  and  $T_{02}$ , and the phase angle has only a single dip near the resonant frequency. The maximum phase dip is  $-180^{\circ}$ .

Compensation for Type II: Placement of the compensation zeros is shown in Fig. 12, similar to a conventional converter using single-output feedback voltage mode control.

### IV. DISCONTINUOUS MODE OF OPERATION

The multiple-output feedback circuit shown in Fig. 1 is normally designed to avoid discontinuous mode of operation. As long as one of the outputs becomes discontinuous mode under light-load conditions, the regulation of both outputs are degraded. Use of large filter inductor or dummy load or couple choke [4] should increase the load range in which the circuit operates in the continuous mode. However, in case discontinuous mode occurs, it is desirable to estimate the control performance of the circuit. This section presents the equations for such usage.

Fig. 9. The Bode plot of  $|T_{01} + T_{02}|$  for the crossover type.

The basic control transfers function for a discontinuousmode buck-derived converter has been reported [5], [6] and are summarized in Table III. Using the results of Tables I and III, the control performance of the discontinuous multiple-output feedback circuit can be derived. The results will be discussed in the following subsections. A word about the symbols used in the following section is appropriate at this point. The subscript D refers to discontinuous mode and subscript numeral refers to the output number. For example,  $G_{d1D}$  refers to the open-loop control-to-output transfer function of output 1 when it is operated in the discontinuous mode. The transfer functions should then be obtained from the discontinuous mode transfer functions shown in Table III. The subscript CLD refers to closed-loop condition, and the apostrophy "'" refers to the transfer function when one output is in the discontinuous mode. For example,  $(G'_{V1})_{CLD}$  refers to closedloop performance of  $G_{V1}$  under the discontinuous condition. The discussion will be limited to only one of the outputs is operated in the discontinuous mode since this case is the most commonly encountered. To avoid repetition, equations shown below are only for the condition that output 1 is in the discontinuous mode and output 2 is in the continuous mode. The equations can be easily modified if the reverse is true.

#### A. Line Regulation

The closed-loop line regulation performance  $(G'_{V1})_{CLD}$  and

Fig. 10. The proper compensation transfer function for the cases depicted

$(G_{V2}^{\prime})_{\mathrm{CLD}}$  can be expressed by (10) and (11).

$$(G'_{V1})_{\text{CLD}} = \frac{(1+T_2)G_{V1D} - \frac{K_2}{K_1}T_{1D}G_{V2}}{1+T_{1D}+T_2}$$

$$(G'_{V2})_{\text{CLD}} = \frac{(1+T_{1D})G_{V2} - \frac{K_1}{K_2}T_2G_{V1D}}{1+T_{1D}+T_2}$$

$$(11)$$

$$(G'_{V2})_{\text{CLD}} = \frac{(1 + T_{1D})G_{V2} - \frac{K_1}{K_2}T_2G_{V1D}}{1 + T_{1D} + T_2} \tag{11}$$

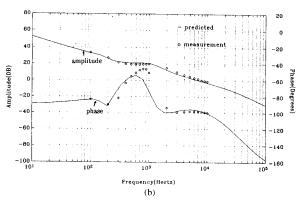

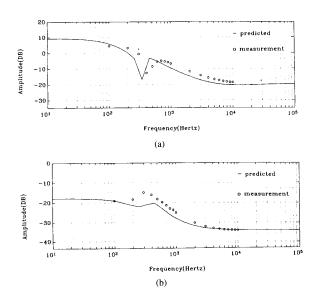

where  $G_{V1D}$  can be obtained from Table III and  $T_{1D}$  is  $AF_mK_1G_{d1D}$  and  $G_{d1D}$  can be obtained from Table III. Fig. 13 shows the close agreement between the measured and the predicted results for this performance. The results shown is for the case when output 1 is in the discontinuous mode and output 2 is in the continuous mode. If the condition reverses (i.e., output 1 is in the continuous mode and output 2 is in the discontinuous mode), then the closed-loop performance can be obtained by replacing  $T_2

ightarrow T_{2D}, T_{1D}

ightarrow T_1, G_{V1D}

ightarrow G_{V1}$ and  $G_{V2} \rightarrow G_{V2D}$  in (10) and (11).

#### B. Output Impedance

The closed-loop performance  $(Z'_{01})_{CLD}$  and  $(Z'_{02})_{CLD}$  can be expressed by (12) and (13).

$$((Z'_{01})_{CLD} = \frac{Z_{01D}(1+T_2)}{1+T_{1D}+T_2}$$

(12)

Fig. 11. (a) Example of improper compensation for crossover type. (b) Bode plot of loop gain T for the case depicted in (a). Loop gain shows a potential

Fig. 12. The Bode plot of the type of close-together resonance frequencies.

$$(Z'_{02})_{\text{CLD}} = \frac{Z_{02}(1+T_{1D})}{1+T_{1D}+T_2}.$$

(13)

If the conditions reverses (i.e., output 1 is in the continuous mode and output 2 is in the discontinuous mode), then the closed-loop performance can be obtained by replacing  $T_2

ightharpoonup$  $T_{2D}, T_{1D} \rightarrow T_1, Z_{01D} \rightarrow Z_{01}$  and  $Z_{02} \rightarrow Z_{02D}$  in (12) and (13). Fig. 14 shows close agreement between the measured

Fig. 13. (a) The Bode plot of  $(G_V)_{\rm CLD}$  (discontinuous mode). (b) The Bode plot of  $(G_{V\,2})_{\rm CLD}$  (discontinuous mode) (where  $f_8=50$  KHz,  $C_1=400~\mu{\rm F}, L_1=50$  \muHR\_c1=0.14 \Omega, R\_{l1}=0.07 \Omega, R\_{L1}=21 \Omega, \ldots \text{(3.1)}  $K_1 = 1.176, C_2 = 4000 \,\mu\text{F}, L_2 = 150 \,\mu\text{H}, R_{C2} = 0.02 \,\Omega, R_{l2} = 0.13 \,\Omega.$  $R_{L2} = 2 \Omega, K_2 = 0.705.$

and the predicted results for the performance of the output impedance.

## C. Cross Regulation

Cross regulation performance  $Z'_{12D}$  and  $Z'_{21D}$  can be expressed by (14) and (15).

$$Z'_{12D} = \frac{-AF_m K_2 G_{d1D}}{1 + T_{1D} + T_2} Z_{02}$$

$$Z'_{21D} = \frac{-AF_m K_1 G_{d2}}{1 + T_{1D} + T_2} Z_{01D}.$$

(14)

$$Z'_{21D} = \frac{-AF_m K_1 G_{d2}}{1 + T_{1D} + T_2} Z_{01D}.$$

(15)

If the conditions reverses (i.e., output 1 is in the continuous mode and output 2 is in the discontinuous mode), then the closed-loop performance can be obtained by replacing  $T_2 \rightarrow$  $T_{2D}, T_{1D} \rightarrow T_1, G_{d1D} \rightarrow G_{d1}, G_{d2} \rightarrow G_{d2D}, Z_{01D} \rightarrow Z_{01}$  and  $Z_{02} \rightarrow Z_{02D}$  in (14) and (15). Fig. 15 shows close agreement between the measured and the predicted performance for the cross regulation.

#### V. CONCLUSION

A small-signal model of a two-output feedback forward converter is presented. The model provides the users valuable design-oriented information. Several conclusions are drawn from this modeling effort:

TABLE III

CONTROL TRANSFER FUNCTIONS OF A DISCONTINUOUS MODE BUCK -DERIVED CONVERTER

$$\begin{split} G_{vD} &= \frac{\hat{v}_0}{\hat{v}_g} = n1 \cdot M \frac{1 + S/w_{z1}}{1 + a_1 S + a_2 S^2} \\ G_{dD} &= \frac{\hat{v}_0}{\hat{d}} = H_d \frac{1 + S/w_{z1}}{1 + a_1 S + a_2 S^2} \\ Z_{0D} &= \frac{\hat{v}_0}{\hat{i}_0} = R_L \frac{(1 - M)(1 + S/w_{z1})(1 + S/w_{z2})}{(2 - M)(1 + a_1 S + a_2 S^2)} \end{split}$$

where

$$\begin{split} M &= \frac{2}{1 + \sqrt{1 + \frac{8Lf_s}{R_L D^2}}} \\ H_d &= \frac{2V_0 r}{D(r + R_L + R_l)} \\ a_1 &= \frac{L}{r + R_L + R_l} + C[R_c + R_L / / (r + R_l)] \\ a_2 &= \frac{LC(R_c + R_L)}{r + R_L + R_l} \end{split} \qquad w_{z1} = \frac{1}{R_c C} \\ w_{z2} &= \frac{R_l + R_L (1 - M)}{L} \\ r &= R_L (1 - M) \\ w_p &= \frac{2 - M}{R_L (C(1 - M))} \end{split}$$

Fig. 14. (a) The Bode plot of  $(Z_{01})_{\rm CLD}$  (discontinuous mode). (b) The Bode plot of  $(Z_{02})_{\rm CLD}$  (discontinuous mode). (The conditions are the same as Fig. 13.)

- 1) Increasing the overall loop gain improves the converterline regulation but not necessarily the load regulation and the cross regulation.

- 2) Load regulation for the two outputs cannot be improved simultaneously. One is always improved at the expense of the other even with a enlarged loop gain. The foregoing statements also apply to the cross-regulation performance, so there is no point to risk circuit instability by increasing loop gain T if the line regulation is already adequate.

- 3) Decreasing one of the loop gain  $(T_{01} \text{ or } T_{02})$  without corresponding change in compensation may lead to circuit instability. This conclusion is counterintuitive.

- 4) If the resonant frequencies of the two output filters are

Fig. 15. (a) The Bode plot of  $Z_{21}$  (discontinuous mode). (b) The Bode plot of  $Z_{12}$  (discontinuous mode). (The conditions are the same as Fig. 13.)

closed to each other, the compensation scheme is similar to a conventional single-output feedback circuit. The two compensation zeros are placed at the resonance frequency. If the two resonance frequencies are widely separated, the compensation zeros should be placed near the lower resonance frequency for the crossover type. For the noncrossover type, the zeros should be placed near the resonance frequency of the larger  $T_0$ 's.

5) When at least one output choke operates in discontinuous mode, at least one of the line regulation performance becomes very poor regardless of the magnitude of the loop gain T.

The foregoing conclusions apply to a forward converter circuit with two-output feedback. The model can be extended to circuits with more than two outputs. The conclusions drawn above apply to cases with more than two outputs.

APPENDIX: PHASE ANGLE OF THE OPEN-LOOP GAIN  $T_0$

Assume  $T_{01} = |T_{01}| \langle \phi_1, \text{ and the maximum value of }$  $\phi_1 \simeq -180^\circ, T_{02} = |T_{02}| \langle \phi_2, \text{ and the maximum value of } \phi_2 \simeq -180^\circ, T_0 = T_{01} + T_{02}, \text{ by the method of vector}$ analysis:

- I. Noncrossover type:

- 1)  $f_{R1} > f_{R2}$

- (a) at  $f \simeq f_{R2}$

The phase of  $T_0$  changes with the magnitude of  $T_{01}$  and  $T_{02}$ , and the maximum value is approximately  $-90^{\circ}$ .

(b) at

$$f \simeq f_{R}$$

:

The phase of  $T_0$  changes with the magnitude of  $T_{01}$  and  $T_{02}$ , and the maximum value is approximately  $-180^{\circ}$ .

- 2)  $f_{R1} < f_{R2}$

- (a) at  $f \simeq f_{R1}$

The phase of  $T_0$  changes with the magnitude of  $T_{01}$  and  $T_{02}$ , and the maximum value is approximately  $-180^{\circ}$ .

(b) at

$$f \simeq f_{R2}$$

The conclusions are the same as (a).

II. Crossover type: The derivation of crossover type is the same as that of noncrossover type.

#### REFERENCES

- [1] R. D. Middlebrook and S. Ćuk, "A general unified approach to modeling switching converter power stages," in *Proc. IEEE Power Electronics Specialists Conf.*, 1976, pp. 18–34.

[2] F. C. Leeet al., "Modeling and analysis of power processing systems (mapps)," Final Rep. vol. I. NASA contract NAS3-21-51, Dec. 1980.

[3] R. B. Ridley, B. H. Cho, and F. C. Lee, "Analysis and interpretation of

- loop gains of multiloop-controlled switching regulators," IEEE Trans. Power Electron., pp. 489-498, Oct. 1988.

- H. Matsuo, "Comparison of multiple-output dc-dc converters using cross regulation," in Proc. IEEE Power Electronics Specialists Conf., 1979,

- v. Vorperian, "Simplified analysis of PWM converters using the model of the PWM switch: Parts I and II," IEEE Trans. Aerosp. Electron. Syst., vol. 26, pp. 490-505, Mar. 1990.

- [6] D. M. Sable, R. B. Ridley, and B. H. Cho, "Comparison of performance of single-loop and current-injection-control for PWM converters which operate in both continuous and discontinuous modes of operation," in Proc. IEEE Power Electronics Spec. Conf., 1990, pp. 74-79.

Yie-Tone Chen was born in Taiwan, R.O.C. in 1965. He received the B.S. and M.S. degrees in electrical engineering from the National Taiwan University, Taipei, Taiwan. He is now working toward the Ph.D. degree in electrical engineering at National Taiwan University.

His research interests include the modeling and control of converters and the circuit design of highperformance switching regulators.

Dan Y. Chen (S'72-M'75-M'79-SM'83) received the B.S. degree from National Chiao-Tung University, Taiwan, and the Ph.D. degree from Duke University, Durham, NC, both in electrical engineering, in 1969 and 1975, respectively.

From 1975 to 1979 he was employed as a member of the research staff at the General Electrical Research and Development Center, Schenectady, NY. Since 1979 he has been on the faculty of the Department of Electrical Engineering, Virginia Polytechnic Institute and State University, Blacks-

burg, VA, where he is presently a Professor. His research activities include work in power semiconductor circuits, circuit-device interactions, device characterization, magnetic devices for power electronic applications, and product applications such as brushless motor robotic drive, electronic ballast, appliance power supply, electric car drive, etc. He has published one book and more than 50 papers and has been awarded six U.S. patents in the field of power electronics.

Dr. Chen served as Chairman of the Power Semiconductor Committee of the IEEE Industry Applications Society from 1984 to 1986.

Yan Pei Wu was born in Tainan, Taiwan, R.O.C. in 1932. He received the B.S. degree in electrical engineering from National Taiwan University, the M.S. degree in electronic engineering from National Chiao-Tung University, Shin-Chu, Taiwan, and the Ph.D. degree in electrical engineering from the University of Washington, Seattle, in 1955, 1960, and 1973, respectively.

From 1957 to 1961, he was an Engineer with the Telecommunication Organization, Taiwan. In 1962, he joined the faculty of the Department of Electrical

Engineering, National Taiwan University, where he is now a Professor. Dr. Wu is a member of the Institute of Electrical Engineers of China