# 6 SAM88RCRI INSTRUCTION SET

### OVERVIEW

The SAM88RCRI instruction set is designed to support the large register file. It includes a full complement of 8-bit arithmetic and logic operations. There are 41 instructions. No special I/O instructions are necessary because I/O control and data registers are mapped directly into the register file. Flexible instructions for bit addressing, rotate, and shift operations complete the powerful data manipulation capabilities of the SAM88RCRI instruction set.

### **REGISTER ADDRESSING**

To access an individual register, an 8-bit address in the range 0-255 or the 4-bit address of a working register is specified. Paired registers can be used to construct 13-bit program memory or data memory addresses. For detailed information about register addressing, please refer to Chapter 2, "Address Spaces".

### ADDRESSING MODES

There are six addressing modes: Register (R), Indirect Register (IR), Indexed (X), Direct (DA), Relative (RA), and Immediate (IM). For detailed descriptions of these addressing modes, please refer to Chapter 3, "Addressing Modes".

|                     | l able 6-1 | . Instruction Group Summary             |

|---------------------|------------|-----------------------------------------|

| Mnemonic            | Operands   | Instruction                             |

| Load Instructions   |            |                                         |

| CLR                 | dst        | Clear                                   |

| LD                  | dst,src    | Load                                    |

| LDC                 | dst,src    | Load program memory                     |

| LDE                 | dst,src    | Load external data memory               |

| LDCD                | dst,src    | Load program memory and decrement       |

| LDED                | dst,src    | Load external data memory and decrement |

| LDCI                | dst,src    | Load program memory and increment       |

| LDEI                | dst,src    | Load external data memory and increment |

| POP                 | dst        | Pop from stack                          |

| PUSH                | SrC        | Push to stack                           |

| Arithmetic Instruct | ions       |                                         |

| ADC                 | dst,src    | Add with carry                          |

| ADD                 | dst,src    | Add                                     |

| СР                  | dst,src    | Compare                                 |

| DEC                 | dst        | Decrement                               |

| INC                 | dst        | Increment                               |

| SBC                 | dst,src    | Subtract with carry                     |

| SUB                 | dst,src    | Subtract                                |

| Logic Instructions  |            |                                         |

| AND                 | dst,src    | Logical AND                             |

| СОМ                 | dst        | Complement                              |

| OR                  | dst,src    | Logical OR                              |

|                     |            |                                         |

Logical exclusive OR

### Table 6-1. Instruction Group Summary

XOR

dst,src

| Mnemonic            | Operands   | Instruction                     |  |

|---------------------|------------|---------------------------------|--|

| Program Control In  | structions |                                 |  |

| CALL                | dst        | Call procedure                  |  |

| IRET                |            | Interrupt return                |  |

| JP                  | cc,dst     | Jump on condition code          |  |

| JP                  | dst        | Jump unconditional              |  |

| JR                  | cc,dst     | Jump relative on condition code |  |

| RET                 |            | Return                          |  |

| Bit Manipulation In | structions |                                 |  |

| ТСМ                 | dst,src    | Test complement under mask      |  |

| ТМ                  | dst,src    | Test under mask                 |  |

| Rotate and Shift In | structions |                                 |  |

| RL                  | dst        | Rotate left                     |  |

| RLC                 | dst        | Rotate left through carry       |  |

| RR                  | dst        | Rotate right                    |  |

| RRC                 | dst        | Rotate right through carry      |  |

| SRA                 | dst        | Shift right arithmetic          |  |

| CPU Control Instru  | ctions     |                                 |  |

| CCF                 |            | Complement carry flag           |  |

| DI                  |            | Disable interrupts              |  |

| EI                  |            | Enable interrupts               |  |

| IDLE                |            | Enter Idle mode                 |  |

| NOP                 |            | No operation                    |  |

| RCF                 |            | Reset carry flag                |  |

| SCF                 |            | Set carry flag                  |  |

| STOP                |            | Enter stop mode                 |  |

Table 6-1. Instruction Group Summary (Continued)

### FLAGS REGISTER (FLAGS)

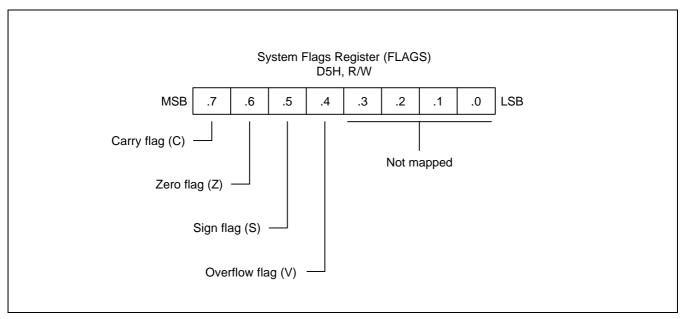

The flags register FLAGS contains eight bits that describe the current status of CPU operations. Four of these bits, FLAGS.4–FLAGS.7, can be tested and used with conditional jump instructions;

FLAGS register can be set or reset by instructions as long as its outcome does not affect the flags, such as, Load instruction. Logical and Arithmetic instructions such as, AND, OR, XOR, ADD, and SUB can affect the Flags register. For example, the AND instruction updates the Zero, Sign and Overflow flags based on the outcome of the AND instruction. If the AND instruction uses the Flags register as the destination, then simultaneously, two write will occur to the Flags register producing an unpredictable result.

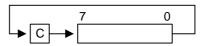

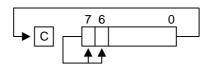

Figure 6-1. System Flags Register (FLAGS)

### FLAG DESCRIPTIONS

### 33Overflow Flag (FLAGS.4, V)

The V flag is set to "1" when the result of a two's-complement operation is greater than + 127 or less than - 128. It is also cleared to "0" following logic operations.

### Sign Flag (FLAGS.5, S)

Following arithmetic, logic, rotate, or shift operations, the sign bit identifies the state of the MSB of the result. A logic zero indicates a positive number and a logic one indicates a negative number.

### Zero Flag (FLAGS.6, Z)

For arithmetic and logic operations, the Z flag is set to "1" if the result of the operation is zero. For operations that test register bits, and for shift and rotate operations, the Z flag is set to "1" if the result is logic zero.

### Carry Flag (FLAGS.7, C)

The C flag is set to "1" if the result from an arithmetic operation generates a carry-out from or a borrow to the bit 7 position (MSB). After rotate and shift operations, it contains the last value shifted out of the specified register. Program instructions can set, clear, or complement the carry flag.

### **INSTRUCTION SET NOTATION**

| Flag | Description                           |

|------|---------------------------------------|

| С    | Carry flag                            |

| Z    | Zero flag                             |

| S    | Sign flag                             |

| V    | Overflow flag                         |

| 0    | Cleared to logic zero                 |

| 1    | Set to logic one                      |

| *    | Set or cleared according to operation |

| _    | Value is unaffected                   |

| х    | Value is undefined                    |

### Table 6-2. Flag Notation Conventions

### Table 6-3. Instruction Set Symbols

| Symbol | Description                                  |

|--------|----------------------------------------------|

| dst    | Destination operand                          |

| src    | Source operand                               |

| @      | Indirect register address prefix             |

| PC     | Program counter                              |

| FLAGS  | Flags register (D5H)                         |

| #      | Immediate operand or register address prefix |

| н      | Hexadecimal number suffix                    |

| D      | Decimal number suffix                        |

| В      | Binary number suffix                         |

| орс    | Opcode                                       |

| Notation | Description                                              | Actual Operand Range                                                                                                     |

|----------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| сс       | Condition code                                           | See list of condition codes in Table 6-6.                                                                                |

| r        | Working register only                                    | Rn (n = 0–15)                                                                                                            |

| rr       | Working register pair                                    | RRp (p = 0, 2, 4,, 14)                                                                                                   |

| R        | Register or working register                             | reg or Rn (reg = 0–255, n = 0–15)                                                                                        |

| RR       | Register pair or working register pair                   | reg or RRp (reg = 0–254, even number only, where $p = 0, 2,, 14$ )                                                       |

| lr       | Indirect working register only                           | @Rn (n = 0-15)                                                                                                           |

| IR       | Indirect register or indirect working register           | @Rn or @reg (reg = 0–255, n = 0–15)                                                                                      |

| Irr      | Indirect working register pair only                      | @RRp (p = 0, 2,, 14)                                                                                                     |

| IRR      | Indirect register pair or indirect working register pair | @RRp or @reg (reg = 0–254, even only, where $p = 0, 2,, 14$ )                                                            |

| х        | Indexed addressing mode                                  | #reg[Rn] (reg = 0–255, n = 0–15)                                                                                         |

| XS       | Indexed (short offset) addressing mode                   | #addr[RRp] (addr = range – 128 to + 127, where p = 0, 2,, 14)                                                            |

| XL       | Indexed (long offset) addressing mode                    | #addr [RRp] (addr = range 0–8191, where p = 0, 2,, 14)                                                                   |

| DA       | Direct addressing mode                                   | addr (addr = range 0-8191)                                                                                               |

| RA       | Relative addressing mode                                 | addr (addr = number in the range + 127 to - 128 that<br>is an offset relative to the address of the next<br>instruction) |

| IM       | Immediate addressing mode                                | #data (data = 0-255)                                                                                                     |

**Table 6-4. Instruction Notation Conventions**

|   | OPCODE MAP |            |             |                 |                 |              |               |              |                     |  |  |

|---|------------|------------|-------------|-----------------|-----------------|--------------|---------------|--------------|---------------------|--|--|

|   |            |            |             | LOWEF           | R NIBBLE (H     | IEX)         |               |              |                     |  |  |

|   | _          | 0          | 1           | 2               | 3               | 4            | 5             | 6            | 7                   |  |  |

| U | 0          | DEC<br>R1  | DEC<br>IR1  | ADD<br>r1,r2    | ADD<br>r1,lr2   | ADD<br>R2,R1 | ADD<br>IR2,R1 | ADD<br>R1,IM |                     |  |  |

| Р | 1          | RLC<br>R1  | RLC<br>IR1  | ADC<br>r1,r2    | ADC<br>r1,lr2   | ADC<br>R2,R1 | ADC<br>IR2,R1 | ADC<br>R1,IM |                     |  |  |

| Р | 2          | INC<br>R1  | INC<br>IR1  | SUB<br>r1,r2    | SUB<br>r1,Ir2   | SUB<br>R2,R1 | SUB<br>IR2,R1 | SUB<br>R1,IM |                     |  |  |

| Е | 3          | JP<br>IRR1 |             | SBC<br>r1,r2    | SBC<br>r1,lr2   | SBC<br>R2,R1 | SBC<br>IR2,R1 | SBC<br>R1,IM |                     |  |  |

| R | 4          |            |             | OR<br>r1,r2     | OR<br>r1,lr2    | OR<br>R2,R1  | OR<br>IR2,R1  | OR<br>R1,IM  |                     |  |  |

|   | 5          | POP<br>R1  | POP<br>IR1  | AND<br>r1,r2    | AND<br>r1,lr2   | AND<br>R2,R1 | AND<br>IR2,R1 | AND<br>R1,IM |                     |  |  |

| N | 6          | COM<br>R1  | COM<br>IR1  | TCM<br>r1,r2    | TCM<br>r1,Ir2   | TCM<br>R2,R1 | TCM<br>IR2,R1 | TCM<br>R1,IM |                     |  |  |

| I | 7          | PUSH<br>R2 | PUSH<br>IR2 | TM<br>r1,r2     | TM<br>r1,lr2    | TM<br>R2,R1  | TM<br>IR2,R1  | TM<br>R1,IM  |                     |  |  |

| В | 8          |            |             |                 |                 |              |               |              | LD<br>r1, x, r2     |  |  |

| В | 9          | RL<br>R1   | RL<br>IR1   |                 |                 |              |               |              | LD<br>r2, x, r1     |  |  |

| L | A          |            |             | CP<br>r1,r2     | CP<br>r1,lr2    | CP<br>R2,R1  | CP<br>IR2,R1  | CP<br>R1,IM  | LDC<br>r1, Irr2, xL |  |  |

| Е | В          | CLR<br>R1  | CLR<br>IR1  | XOR<br>r1,r2    | XOR<br>r1,lr2   | XOR<br>R2,R1 | XOR<br>IR2,R1 | XOR<br>R1,IM | LDC<br>r2, Irr2, xL |  |  |

|   | С          | RRC<br>R1  | RRC<br>IR1  |                 | LDC<br>r1,Irr2  |              |               |              | LD<br>r1, lr2       |  |  |

| н | D          | SRA<br>R1  | SRA<br>IR1  |                 | LDC<br>r2,Irr1  |              |               | LD<br>IR1,IM | LD<br>Ir1, r2       |  |  |

| Е | E          | RR<br>R1   | RR<br>IR1   | LDCD<br>r1,Irr2 | LDCI<br>r1,Irr2 | LD<br>R2,R1  | LD<br>R2,IR1  | LD<br>R1,IM  | LDC<br>r1, Irr2, xs |  |  |

| х | F          |            |             |                 |                 | CALL<br>IRR1 | LD<br>IR2,R1  | CALL<br>DA1  | LDC<br>r2, Irr1, xs |  |  |

### Table 6-5. Opcode Quick Reference

|   | OPCODE MAP |              |              |       |              |              |              |              |      |  |  |

|---|------------|--------------|--------------|-------|--------------|--------------|--------------|--------------|------|--|--|

|   |            |              |              | LOWER | R NIBBLE (H  | IEX)         |              |              |      |  |  |

|   | -          | 8            | 9            | А     | В            | С            | D            | Е            | F    |  |  |

| U | 0          | LD<br>r1,R2  | LD<br>r2,R1  |       | JR<br>cc,RA  | LD<br>r1,IM  | JP<br>cc,DA  | INC<br>r1    |      |  |  |

| Р | 1          | $\downarrow$ | $\downarrow$ |       | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ |      |  |  |

| Р | 2          |              |              |       |              |              |              |              |      |  |  |

| E | 3          |              |              |       |              |              |              |              |      |  |  |

| R | 4          |              |              |       |              |              |              |              |      |  |  |

|   | 5          |              |              |       |              |              |              |              |      |  |  |

| N | 6          |              |              |       |              |              |              |              | IDLE |  |  |

| I | 7          | $\downarrow$ | $\downarrow$ |       | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | STOP |  |  |

| В | 8          |              |              |       |              |              |              |              | DI   |  |  |

| В | 9          |              |              |       |              |              |              |              | EI   |  |  |

| L | A          |              |              |       |              |              |              |              | RET  |  |  |

| E | В          |              |              |       |              |              |              |              | IRET |  |  |

|   | С          |              |              |       | _            |              |              |              | RCF  |  |  |

| н | D          | Ļ            | $\downarrow$ |       | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | SCF  |  |  |

| E | E          |              |              |       |              |              |              |              | CCF  |  |  |

| X | F          | LD<br>r1,R2  | LD<br>r2,R1  |       | JR<br>cc,RA  | LD<br>r1,IM  | JP<br>cc,DA  | INC<br>r1    | NOP  |  |  |

### **CONDITION CODES**

The opcode of a conditional jump always contains a 4-bit field called the condition code (cc). This specifies under which conditions it is to execute the jump. For example, a conditional jump with the condition code for "equal" after a compare operation only jumps if the two operands are equal. Condition codes are listed in Table 6-6.

The carry (C), zero (Z), sign (S), and overflow (V) flags are used to control the operation of conditional jump instructions.

| Binary              | Mnemonic | Description                    | Flags Set             |

|---------------------|----------|--------------------------------|-----------------------|

| 0000                | F        | Always false                   | -                     |

| 1000                | Т        | Always true                    | -                     |

| 0111 <sup>(1)</sup> | С        | Carry                          | C = 1                 |

| 1111 <sup>(1)</sup> | NC       | No carry                       | C = 0                 |

| 0110 <sup>(1)</sup> | Z        | Zero                           | Z = 1                 |

| 1110 <sup>(1)</sup> | NZ       | Not zero                       | Z = 0                 |

| 1101                | PL       | Plus                           | S = 0                 |

| 0101                | MI       | Minus                          | S = 1                 |

| 0100                | OV       | Overflow                       | V = 1                 |

| 1100                | NOV      | No overflow                    | V = 0                 |

| 0110 <sup>(1)</sup> | EQ       | Equal                          | Z = 1                 |

| 1110 <sup>(1)</sup> | NE       | Not equal                      | Z = 0                 |

| 1001                | GE       | Greater than or equal          | (S XOR V) = 0         |

| 0001                | LT       | Less than                      | (S XOR V) = 1         |

| 1010                | GT       | Greater than                   | (Z OR (S XOR V)) = 0  |

| 0010                | LE       | Less than or equal             | (Z OR (S XOR V)) = 1  |

| 1111 <sup>(1)</sup> | UGE      | Unsigned greater than or equal | C = 0                 |

| 0111 <sup>(1)</sup> | ULT      | Unsigned less than             | C = 1                 |

| 1011                | UGT      | Unsigned greater than          | (C = 0 AND Z = 0) = 1 |

| 0011                | ULE      | Unsigned less than or equal    | (C OR Z) = 1          |

### Table 6-6. Condition Codes

### NOTES:

It indicates condition codes that are related to two different mnemonics but which test the same flag.

For example, Z and EQ are both true if the zero flag (Z) is set, but after an ADD instruction, Z would probably be used; after a CP instruction, however, EQ would probably be used.

2. For operations involving unsigned numbers, the special condition codes UGE, ULT, UGT, and ULE must be used.

### INSTRUCTION DESCRIPTIONS

This section contains detailed information and programming examples for each instruction in the SAM87Ri instruction set. Information is arranged in a consistent format for improved readability and for fast referencing. The following information is included in each instruction description:

- Instruction name (mnemonic)

- Full instruction name

- Source/destination format of the instruction operand

- Shorthand notation of the instruction's operation

- Textual description of the instruction's effect

- Specific flag settings affected by the instruction

- Detailed description of the instruction's format, execution time, and addressing mode(s)

- Programming example(s) explaining how to use the instruction

### **ADC** — Add with Carry

ADC dst,src

**Operation:** dst  $\leftarrow$  dst + src + c

The source operand, along with the setting of the carry flag, is added to the destination operand and the sum is stored in the destination. The contents of the source are unaffected. Two's-complement addition is performed. In multiple precision arithmetic, this instruction permits the carry from the addition of low-order operands to be carried into the addition of high-order operands.

Flags: C: Set if there is a carry from the most significant bit of the result; cleared otherwise.

- Z: Set if the result is "0"; cleared otherwise.

- **S:** Set if the result is negative; cleared otherwise.

- V: Set if arithmetic overflow occurs, that is, if both operands are of the same sign and the result is of the opposite sign; cleared otherwise.

### Format:

|     |           |     | Bytes | Cycles | Opcode<br>(Hex) | Addr<br><u>dst</u> | Mode<br><u>src</u> |

|-----|-----------|-----|-------|--------|-----------------|--------------------|--------------------|

| орс | dst   src |     | 2     | 4      | 12              | r                  | r                  |

|     |           |     |       | 6      | 13              | r                  | lr                 |

| орс | src       | dst | 3     | 6      | 14              | R                  | R                  |

|     |           |     |       | 6      | 15              | R                  | IR                 |

| орс | dst       | SIC | 3     | 6      | 16              | R                  | IM                 |

**Examples:** Given: R1 = 10H, R2 = 03H, C flag = "1", register 01H = 20H, register 02H = 03H, and register 03H = 0AH:

| ADC | R1,R2      | > | R1 = 14H, R2 = 03H                     |

|-----|------------|---|----------------------------------------|

| ADC | R1,@R2 —   | > | R1 = 1BH, R2 = 03H                     |

| ADC | 01H,02H —  | > | Register 01H = 24H, register 02H = 03H |

| ADC | 01H,@02H — | > | Register 01H = 2BH, register 02H = 03H |

| ADC | 01H,#11H — | > | Register 01H = 32H                     |

In the first example, destination register R1 contains the value 10H, the carry flag is set to "1", and the source working register R2 contains the value 03H. The statement "ADC R1,R2" adds 03H and the carry flag value ("1") to the destination value 10H, leaving 14H in register R1.

# ADD-Add

ADD dst,src

**Operation:** dst  $\leftarrow$  dst + src

The source operand is added to the destination operand and the sum is stored in the destination. The contents of the source are unaffected. Two's-complement addition is performed.

Flags: C: Set if there is a carry from the most significant bit of the result; cleared otherwise.

- Z: Set if the result is "0"; cleared otherwise.

- **S:** Set if the result is negative; cleared otherwise.

V: Set if arithmetic overflow occurred, that is, if both operands are of the same sign and the result is of the opposite sign; cleared otherwise.

### Format:

|     |           |     | Bytes | s Cycles | Opcode<br>(Hex) | Addr<br><u>dst</u> | Mode<br><u>src</u> |

|-----|-----------|-----|-------|----------|-----------------|--------------------|--------------------|

| орс | dst   src |     | 2     | 4        | 02              | r                  | r                  |

|     |           |     |       | 6        | 03              | r                  | lr                 |

| орс | src       | dst | 3     | 6        | 04              | R                  | R                  |

|     |           |     |       | 6        | 05              | R                  | IR                 |

| орс | dst       | SrC | 3     | 6        | 06              | R                  | IM                 |

Examples: (

Given: R1 = 12H, R2 = 03H, register 01H = 21H, register 02H = 03H, register 03H = 0AH:

| ADD | R1,R2    | $\rightarrow$ | R1 = 15H, R2 = 03H                     |

|-----|----------|---------------|----------------------------------------|

| ADD | R1,@R2   | $\rightarrow$ | R1 = 1CH, R2 = 03H                     |

| ADD | 01H,02H  | $\rightarrow$ | Register 01H = 24H, register 02H = 03H |

| ADD | 01H,@02H | $\rightarrow$ | Register 01H = 2BH, register 02H = 03H |

| ADD | 01H,#25H | $\rightarrow$ | Register 01H = $46H$                   |

In the first example, destination working register R1 contains 12H and the source working register R2 contains 03H. The statement "ADD R1,R2" adds 03H to 12H, leaving the value 15H in register R1.

# AND - Logical AND

AND dst,src

**Operation:** dst  $\leftarrow$  dst AND src

The source operand is logically ANDed with the destination operand. The result is stored in the destination. The AND operation results in a "1" bit being stored whenever the corresponding bits in the two operands are both logic ones; otherwise a "0" bit value is stored. The contents of the source are unaffected.

- Flags: C: Unaffected.

- **Z:** Set if the result is "0"; cleared otherwise.

- S: Set if the result bit 7 is set; cleared otherwise.

- V: Always cleared to "0".

### Format:

| _ |     |           |     | Bytes | s Cycles | Opcode<br>(Hex) | Addr<br><u>dst</u> | Mode<br><u>src</u> |

|---|-----|-----------|-----|-------|----------|-----------------|--------------------|--------------------|

|   | орс | dst   src |     | 2     | 4        | 52              | r                  | r                  |

|   |     |           |     |       | 6        | 53              | r                  | lr                 |

|   | орс | SrC       | dst | 3     | 6        | 54              | R                  | R                  |

|   |     |           |     |       | 6        | 55              | R                  | IR                 |

|   | орс | dst       | src | 3     | 6        | 56              | R                  | IM                 |

**Examples:** Given: R1 = 12H, R2 = 03H, register 01H = 21H, register 02H = 03H, register 03H = 0AH:

| AND | R1,R2    | $\rightarrow$ | R1 = 02H, R2 = 03H                     |

|-----|----------|---------------|----------------------------------------|

| AND | R1,@R2   | $\rightarrow$ | R1 = 02H, R2 = 03H                     |

| AND | 01H,02H  | $\rightarrow$ | Register 01H = 01H, register 02H = 03H |

| AND | 01H,@02H | $\rightarrow$ | Register 01H = 00H, register 02H = 03H |

| AND | 01H,#25H | $\rightarrow$ | Register 01H = 21H                     |

In the first example, destination working register R1 contains the value 12H and the source working register R2 contains 03H. The statement "AND R1,R2" logically ANDs the source operand 03H with the destination operand value 12H, leaving the value 02H in register R1.

# CALL — Call Procedure

| CALL | dst |

|------|-----|

|------|-----|

| Operation: | SP<br>@SP | $\leftarrow$ | SP – 1<br>PCL |

|------------|-----------|--------------|---------------|

|            | SP        | $\leftarrow$ | SP –1         |

|            | @SP       | $\leftarrow$ | PCH           |

|            | PC        | $\leftarrow$ | dst           |

The current contents of the program counter are pushed onto the top of the stack. The program counter value used is the address of the first instruction following the CALL instruction. The specified destination address is then loaded into the program counter and points to the first instruction of a procedure. At the end of the procedure the return instruction (RET) can be used to return to the original program flow. RET pops the top of the stack back into the program counter.

Flags: No flags are affected.

### Format:

|   |     |     | Bytes | Cycles | Opcode<br>(Hex) | Addr Mode<br><u>dst</u> |

|---|-----|-----|-------|--------|-----------------|-------------------------|

|   | орс | dst | 3     | 14     | F6              | DA                      |

| ĺ | орс | dst | 2     | 12     | F4              | IRR                     |

**Examples:** Given: R0 = 15H, R1 = 21H, PC = 1A47H, and SP = 0B2H:

| CALL | 1521H | $\rightarrow$ | SP = 0B0H<br>(Memory locations $00H = 1AH$ , $01H = 4AH$ , where $4AH$ is the address that follows the instruction.) |

|------|-------|---------------|----------------------------------------------------------------------------------------------------------------------|

| CALL | @RR0  | $\rightarrow$ | SP = 0B0H (00H = 1AH, 01H = 49H)                                                                                     |

In the first example, if the program counter value is 1A47H and the stack pointer contains the value 0B2H, the statement "CALL 1521H" pushes the current PC value onto the top of the stack. The stack pointer now points to memory location 00H. The PC is then loaded with the value 1521H, the address of the first instruction in the program sequence to be executed.

If the contents of the program counter and stack pointer are the same as in the first example, the statement "CALL @RR0" produces the same result except that the 49H is stored in stack location 01H (because the two-byte instruction format was used). The PC is then loaded with the value 1521H, the address of the first instruction in the program sequence to be executed.

# **CCF** — Complement Carry Flag

CCF

- Operation: C ← NOT C The carry flag (C) is complemented. If C = "1", the value of the carry flag is changed to logic zero; if C = "0", the value of the carry flag is changed to logic one.

- Flags: C: Complemented. No other flags are affected.

### Format:

|     | Bytes | Cycles | Opcode<br>(Hex) |

|-----|-------|--------|-----------------|

| орс | 1     | 4      | EF              |

### **Example:** Given: The carry flag = "0":

CCF

If the carry flag = "0", the CCF instruction complements it in the FLAGS register (0D5H), changing its value from logic zero to logic one.

dst

# CLR-Clear

CLR

**Operation:** dst  $\leftarrow$  "0"

The destination location is cleared to "0".

Flags: No flags are affected.

### Format:

|     |     | Bytes | S Cycles | Opcode<br>(Hex) | Addr Mode<br><u>dst</u> |

|-----|-----|-------|----------|-----------------|-------------------------|

| орс | dst | 2     | 4        | B0              | R                       |

|     |     |       | 4        | B1              | IR                      |

**Examples:** Given: Register 00H = 4FH, register 01H = 02H, and register 02H = 5EH:

| CLR | 00H  | $\rightarrow$ | Register $00H = 00H$                   |

|-----|------|---------------|----------------------------------------|

| CLR | @01H | $\rightarrow$ | Register 01H = 02H, register 02H = 00H |

In Register (R) addressing mode, the statement "CLR 00H" clears the destination register 00H value to 00H. In the second example, the statement "CLR @01H" uses Indirect Register (IR) addressing mode to clear the 02H register value to 00H.

# **COM** – Complement

COM dst

**Operation:** dst  $\leftarrow$  NOT dst

The contents of the destination location are complemented (one's complement); all "1s" are changed to "0s", and vice-versa.

- Flags: C: Unaffected.

- Z: Set if the result is "0"; cleared otherwise.

- S: Set if the result bit 7 is set; cleared otherwise.

- V: Always reset to "0".

### Format:

|     |     | Bytes | Cycles | Opcode<br>(Hex) | Addr Mode<br><u>dst</u> |

|-----|-----|-------|--------|-----------------|-------------------------|

| орс | dst | 2     | 4      | 60              | R                       |

|     |     |       | 4      | 61              | IR                      |

| <b>Examples:</b> Given: R1 = 07H and register 07H = 0F1H: |

|-----------------------------------------------------------|

|-----------------------------------------------------------|

| COM | R1  | $\rightarrow$ | R1 = 0F8H                    |

|-----|-----|---------------|------------------------------|

| СОМ | @R1 | $\rightarrow$ | R1 = 07H, register 07H = 0EH |

In the first example, destination working register R1 contains the value 07H (00000111B). The statement "COM R1" complements all the bits in R1: all logic ones are changed to logic zeros, and vice-versa, leaving the value 0F8H (11111000B).

In the second example, Indirect Register (IR) addressing mode is used to complement the value of destination register 07H (11110001B), leaving the new value 0EH (00001110B).

# ${\bf CP}-{\bf Compare}$

| СР | dst,src |

|----|---------|

|    | u31,310 |

### Operation: dst - src

The source operand is compared to (subtracted from) the destination operand, and the appropriate flags are set accordingly. The contents of both operands are unaffected by the comparison.

- **Flags:** C: Set if a "borrow" occurred (src > dst); cleared otherwise.

- Z: Set if the result is "0"; cleared otherwise.

- **S:** Set if the result is negative; cleared otherwise.

V: Set if arithmetic overflow occurred, that is, if the operands were of opposite signs and the sign of the result is of the same as the sign of the source operand; cleared otherwise.

### Format:

|     |           |     | Byte | s Cycles | Opcode<br>(Hex) | Addr<br><u>dst</u> | Mode<br><u>src</u> |

|-----|-----------|-----|------|----------|-----------------|--------------------|--------------------|

| орс | dst   src |     | 2    | 4        | A2              | r                  | r                  |

|     |           |     |      | 6        | A3              | r                  | lr                 |

| орс | SrC       | dst | 3    | 6        | A4              | R                  | R                  |

|     |           |     |      | 6        | A5              | R                  | IR                 |

| орс | dst       | SIC | 3    | 6        | A6              | R                  | IM                 |

Examples:

1. Given: R1 = 02H and R2 = 03H:

$\mathsf{CP} \qquad \mathsf{R1,R2} \ \rightarrow \ \mathsf{Set} \ \mathsf{the} \ \mathsf{C} \ \mathsf{and} \ \mathsf{S} \ \mathsf{flags}$

Destination working register R1 contains the value 02H and source register R2 contains the value 03H. The statement "CP R1,R2" subtracts the R2 value (source/subtrahend) from the R1 value (destination/minuend). Because a "borrow" occurs and the difference is negative, C and S are "1".

2. Given: R1 = 05H and R2 = 0AH:

|      | CP  | R1,R2    |

|------|-----|----------|

|      | JP  | UGE,SKIP |

|      | INC | R1       |

| SKIP | LD  | R3,R1    |

In this example, destination working register R1 contains the value 05H which is less than the contents of the source working register R2 (0AH). The statement "CP R1,R2" generates C = "1" and the JP instruction does not jump to the SKIP location. After the statement "LD R3,R1" executes, the value 06H remains in working register R3.

# DEC — Decrement

dst

DEC

**Operation:** dst  $\leftarrow$  dst -1

The contents of the destination operand are decremented by one.

### Flags: C: Unaffected.

- **Z:** Set if the result is "0"; cleared otherwise.

- S: Set if result is negative; cleared otherwise.

- V: Set if arithmetic overflow occurred, that is, dst value is 128 (80H) and result value is + 127 (7FH); cleared otherwise.

### Format:

|   |     |     | Bytes | Cycles | Opcode<br>(Hex) | Addr Mode<br><u>dst</u> |

|---|-----|-----|-------|--------|-----------------|-------------------------|

|   | орс | dst | 2     | 4      | 00              | R                       |

| - |     |     |       | 4      | 01              | IR                      |

| Examples: | Given: | R1 | = | 03H and register $03H = 10H$ : |  |

|-----------|--------|----|---|--------------------------------|--|

|-----------|--------|----|---|--------------------------------|--|

| DEC | R1  | $\rightarrow$ | R1 = 02H           |

|-----|-----|---------------|--------------------|

| DEC | @R1 | $\rightarrow$ | Register 03H = 0FH |

In the first example, if working register R1 contains the value 03H, the statement "DEC R1" decrements the hexadecimal value by one, leaving the value 02H. In the second example, the statement "DEC @R1" decrements the value 10H contained in the destination register 03H by one, leaving the value 0FH.

## **DI** — Disable Interrupts

DI

**Operation:** SYM (2)  $\leftarrow$  0

Bit zero of the system mode register, SYM.2, is cleared to "0", globally disabling all interrupt processing. Interrupt requests will continue to set their respective interrupt pending bits, but the CPU will not service them while interrupt processing is disabled.

Flags: No flags are affected.

### Format:

|     | Bytes | Cycles | Opcode<br>(Hex) |

|-----|-------|--------|-----------------|

| орс | 1     | 4      | 8F              |

**Example:** Given: SYM = 04H:

DI

If the value of the SYM register is 04H, the statement "DI" leaves the new value 00H in the register and clears SYM.2 to "0", disabling interrupt processing.

# EI — Enable Interrupts

EI

**Operation:** SYM (2)  $\leftarrow$  1

An EI instruction sets bit 2 of the system mode register, SYM.2 to "1". This allows interrupts to be serviced as they occur. If an interrupt's pending bit was set while interrupt processing was disabled (by executing a DI instruction), it will be serviced when you execute the EI instruction.

Flags: No flags are affected.

### Format:

|     | Bytes | Cycles | Opcode<br>(Hex) |

|-----|-------|--------|-----------------|

| орс | 1     | 4      | 9F              |

**Example:** Given: SYM = 00H:

ΕI

If the SYM register contains the value 00H, that is, if interrupts are currently disabled, the statement "EI" sets the SYM register to 04H, enabling all interrupts. (SYM.2 is the enable bit for global interrupt processing.)

# IDLE - Idle Operation

### IDLE

### **Operation:**

The IDLE instruction stops the CPU clock while allowing system clock oscillation to continue. Idle mode can be released by an interrupt request (IRQ) or an external reset operation.

Flags: No flags are affected.

### Format:

|     | Bytes | Cycles | Opcode |            |            |

|-----|-------|--------|--------|------------|------------|

|     |       |        | (Hex)  | <u>dst</u> | <u>src</u> |

| орс | 1     | 4      | 6F     | -          | _          |

**Example:** The instruction

IDLE NOP NOP NOP

stops the CPU clock but not the system clock.

dst

# INC -- Increment

INC

**Operation:** dst  $\leftarrow$  dst + 1

The contents of the destination operand are incremented by one.

### Flags: C: Unaffected.

- **Z:** Set if the result is "0"; cleared otherwise.

- S: Set if the result is negative; cleared otherwise.

- V: Set if arithmetic overflow occurred, that is dst value is + 127 (7FH) and result is 128 (80H); cleared otherwise.

### Format:

|   |           |     | Byte | es Cycle | es Opcode<br>(Hex) | Addr Mode<br><u>dst</u> |

|---|-----------|-----|------|----------|--------------------|-------------------------|

|   | dst   opc |     | 1    | 4        | rE                 | r                       |

| - |           |     |      |          | r=0 to F           |                         |

| F |           |     |      |          |                    |                         |

|   | орс       | dst | 2    | 4        | 20                 | R                       |

|   |           |     |      | 4        | 21                 | IR                      |

**Examples:** Given: R0 = 1BH, register 00H = 0CH, and register 1BH = 0FH:

| INC | R0  | $\rightarrow$ | R0 = 1CH                       |

|-----|-----|---------------|--------------------------------|

| INC | 00H | $\rightarrow$ | Register $00H = 0DH$           |

| INC | @R0 | $\rightarrow$ | R0 = 1BH, register $01H = 10H$ |

In the first example, if destination working register R0 contains the value 1BH, the statement "INC R0" leaves the value 1CH in that same register.

The next example shows the effect an INC instruction has on register 00H, assuming that it contains the value 0CH.

In the third example, INC is used in Indirect Register (IR) addressing mode to increment the value of register 1BH from 0FH to 10H.

# IRET — Interrupt Return

IRET IRET

**Operation:** FLAGS  $\leftarrow$  @SP

$\begin{array}{rrrr} \mathsf{SP} \ \leftarrow \ \mathsf{SP} \ + \ 1 \\ \mathsf{PC} \ \leftarrow \ @\mathsf{SP} \\ \mathsf{SP} \ \leftarrow \ \mathsf{SP} \ + \ 2 \\ \mathsf{SYM}(2) \ \leftarrow \ 1 \end{array}$

This instruction is used at the end of an interrupt service routine. It restores the flag register and the program counter. It also re-enables global interrupts.

Flags: All flags are restored to their original settings (that is, the settings before the interrupt occurred).

### Format:

| IRET<br>(Normal) | Bytes | Cycles | Opcode<br>(Hex) |

|------------------|-------|--------|-----------------|

| орс              | 1     | 10     | BF              |

|                  |       | 12     |                 |

# JP — Jump

| JP | cc.dst | (Conditional) |

|----|--------|---------------|

| JF | cc,usi | (Conulional)  |

### JP dst (Unconditional)

**Operation:** If cc is true, PC  $\leftarrow$  dst

The conditional JUMP instruction transfers program control to the destination address if the condition specified by the condition code (cc) is true; otherwise, the instruction following the JP instruction is executed. The unconditional JP simply replaces the contents of the PC with the contents of the specified register pair. Control then passes to the statement addressed by the PC.

Flags: No flags are affected.

### Format: <sup>(1)</sup>

| (2)      |     | Bytes | Cycles | Opcode<br>(Hex) | Addr Mode<br><u>dst</u> |

|----------|-----|-------|--------|-----------------|-------------------------|

| cc   opc | dst | 3     | 8      | ccD             | DA                      |

|          |     |       |        | cc = 0 to F     |                         |

| орс      | dst | 2     | 8      | 30              | IRR                     |

### NOTES:

- 1. The 3-byte format is used for a conditional jump and the 2-byte format for an unconditional jump.

- 2. In the first byte of the three-byte instruction format (conditional jump), the condition code and the op code are both four bits.

| Examples: | Given: | The carry flag (C) = "1 | ", register 00 = | 01H, and register 01 | = 20H: |

|-----------|--------|-------------------------|------------------|----------------------|--------|

|-----------|--------|-------------------------|------------------|----------------------|--------|

| JP | C,LABEL_W | $\rightarrow$ | $LABEL_W = 1000H, PC = 1000H$ |

|----|-----------|---------------|-------------------------------|

| JP | @00H      | $\rightarrow$ | PC = 0120H                    |

The first example shows a conditional JP. Assuming that the carry flag is set to "1", the statement "JP C,LABEL\_W" replaces the contents of the PC with the value 1000H and transfers control to that location. Had the carry flag not been set, control would then have passed to the statement immediately following the JP instruction.

The second example shows an unconditional JP. The statement "JP @00" replaces the contents of the PC with the contents of the register pair 00H and 01H, leaving the value 0120H.

# JR — Jump Relative

JR cc,dst

**Operation:** If cc is true, PC  $\leftarrow$  PC + dst

If the condition specified by the condition code (cc) is true, the relative address is added to the program counter and control passes to the statement whose address is now in the program counter; otherwise, the instruction following the JR instruction is executed (See list of condition codes).

The range of the relative address is + 127, - 128, and the original value of the program counter is taken to be the address of the first instruction byte following the JR statement.

Flags: No flags are affected.

### Format:

|   | (note)   |     | _ | Bytes | Cycles | Opcode<br>(Hex) | Addr Mode<br><u>dst</u> |

|---|----------|-----|---|-------|--------|-----------------|-------------------------|

|   | cc   opc | dst |   | 2     | 6      | ccB             | RA                      |

| - |          |     | _ |       |        | cc = 0 to F     |                         |

- **NOTE**: In the first byte of the two-byte instruction format, the condition code and the op code are each four bits.

- **Example:** Given: The carry flag = "1" and LABEL\_X = 1FF7H:

JR C,LABEL\_X  $\rightarrow$  PC = 1FF7H

If the carry flag is set (that is, if the condition code is true), the statement "JR C,LABEL\_X" will pass control to the statement whose address is now in the PC. Otherwise, the program instruction following the JR would be executed.

# LD - Load

LD

**Operation:** dst  $\leftarrow$  src

The contents of the source are loaded into the destination. The source's contents are unaffected.

Flags: No flags are affected.

dst,src

Format:

|           |           |     | Bytes | Cycles | Opcode<br>(Hex) | Addr<br><u>dst</u> | Mode<br><u>src</u> |

|-----------|-----------|-----|-------|--------|-----------------|--------------------|--------------------|

| dst   opc | src       |     | 2     | 4      | rC              | r                  | IM                 |

|           | -         |     |       | 4      | r8              | r                  | R                  |

| src   opc | dst       |     | 2     | 4      | r9              | R                  | r                  |

|           | -         |     |       |        | r = 0 to F      |                    |                    |

| орс       | dst   src |     | 2     | 4      | C7              | r                  | lr                 |

|           |           |     | 1     | 4      | D7              | lr                 | r                  |

| орс       | src       | dst | 3     | 6      | E4              | R                  | R                  |

|           | 1         |     | 1     | 6      | E5              | R                  | IR                 |

| орс       | dst       | src | 3     | 6      | E6              | R                  | IM                 |

|           |           |     | 1     | 6      | D6              | IR                 | IM                 |

| орс       | src       | dst | 3     | 6      | F5              | IR                 | R                  |

| орс       | dst   src | х   | 3     | 6      | 87              | r                  | x [r]              |

| орс       | src   dst | х   | 3     | 6      | 97              | x [r]              | r                  |

# LD - Load

LD

(Continued)

```

Examples: Given: R0 = 01H, R1 = 0AH, register 00H = 01H, register 01H = 20H, register 02H = 02H, LOOP = 30H, and register 3AH = 0FFH:

```

| LD | R0,#10H      | $\rightarrow$ | R0 = 10H                                                  |

|----|--------------|---------------|-----------------------------------------------------------|

| LD | R0,01H       | $\rightarrow$ | R0 = 20H, register $01H = 20H$                            |

| LD | 01H,R0       | $\rightarrow$ | Register 01H = 01H, R0 = 01H                              |

| LD | R1,@R0       | $\rightarrow$ | R1 = 20H, R0 = 01H                                        |

| LD | @R0,R1       | $\rightarrow$ | R0 = 01H, R1 = 0AH, register 01H = 0AH                    |

| LD | 00H,01H      | $\rightarrow$ | Register 00H = 20H, register 01H = 20H                    |

| LD | 02H,@00H     | $\rightarrow$ | Register 02H = $20H$ , register $00H = 01H$               |

| LD | 00H,#0AH     | $\rightarrow$ | Register $00H = 0AH$                                      |

| LD | @00H,#10H    | $\rightarrow$ | Register 00H = 01H, register 01H = $10H$                  |

| LD | @00H,02H     | $\rightarrow$ | Register 00H = 01H, register 01H = 02, register 02H = 02H |

| LD | R0,#LOOP[R1] | $\rightarrow$ | R0 = 0FFH, R1 = 0AH                                       |

| LD | #LOOP[R0],R1 | $\rightarrow$ | Register 31H = 0AH, R0 = 01H, R1 = 0AH                    |

# LDC/LDE — Load Memory

LDC/LDE dst,src

**Operation:** dst  $\leftarrow$  src

This instruction loads a byte from program or data memory into a working register or vice-versa. The source values are unaffected. LDC refers to program memory and LDE to data memory. The assembler makes "Irr" or "rr" values an even number for program memory and odd an odd number for data memory.

Flags: No flags are affected.

### Format:

|     |     |            |                 |                 | Bytes | Cycles | Opcode<br>(Hex) | Addr<br><u>dst</u> | Mode<br><u>src</u> |

|-----|-----|------------|-----------------|-----------------|-------|--------|-----------------|--------------------|--------------------|

| 1.  | орс | dst   src  |                 |                 | 2     | 10     | C3              | r                  | Irr                |

| 2.  | орс | src   dst  |                 |                 | 2     | 10     | D3              | Irr                | r                  |

| 3.  | орс | dst   src  | XS              | ]               | 3     | 12     | E7              | r                  | XS [rr]            |

| 4.  | орс | src   dst  | XS              | ]               | 3     | 12     | F7              | XS [rr]            | r                  |

| 5.  | орс | dst   src  | XLL             | XL <sub>H</sub> | 4     | 14     | A7              | r                  | XL [rr]            |

| 6.  | орс | src   dst  | XLL             | XL <sub>H</sub> | 4     | 14     | B7              | XL [rr]            | r                  |

| 7.  | орс | dst   0000 | DAL             | DA <sub>H</sub> | 4     | 14     | A7              | r                  | DA                 |

| 8.  | орс | src   0000 | DAL             | DA <sub>H</sub> | 4     | 14     | B7              | DA                 | r                  |

| 9.  | орс | dst   0001 | $DA_L$          | DA <sub>H</sub> | 4     | 14     | A7              | r                  | DA                 |

| 10. | орс | src   0001 | DA <sub>L</sub> | DA <sub>H</sub> | 4     | 14     | B7              | DA                 | r                  |

### NOTES:

- 1. The source (src) or working register pair [rr] for formats 5 and 6 cannot use register pair 0–1.

- 2. For formats 3 and 4, the destination address "XS [rr]" and the source address "XS [rr]" are each one byte.

- 3. For formats 5 and 6, the destination address "XL [rr]" and the source address "XL [rr]" are each two bytes.

- 4. The DA and r source values for formats 7 and 8 are used to address program memory; the second set of values, used in formats 9 and 10, are used to address data memory.

# LDC/LDE — Load Memory

LDC/LDE (Continued)

**Examples:** Given: R0 = 11H, R1 = 34H, R2 = 01H, R3 = 04H, R4 = 00H, R5 = 60H; Program memory locations 0061 = AAH, 0103H = 4FH, 0104H = 1A, 0105H = 6DH, and 1104H = 88H. External data memory locations 0061H = BBH, 0103H = 5FH, 0104H = 2AH, 0105H = 7DH, and 1104H = 98H:

| LDC        | R0,@RR2        | ;      | $R0 \leftarrow$ contents of program memory location 0104H<br>R0 = 1AH, R2 = 01H, R3 = 04H                                           |

|------------|----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| LDE        | R0,@RR2        | ;      | $R0 \leftarrow$ contents of external data memory location 0104H<br>R0 = 2AH, R2 = 01H, R3 = 04H                                     |

| LDC (note) | @RR2,R0        | ;;;    | 11H (contents of R0) is loaded into program memory location 0104H (RR2), working registers R0, R2, R3 $\rightarrow$ no change       |

| LDE        | @RR2,R0        | ;;;    | 11H (contents of R0) is loaded into external data memory location 0104H (RR2), working registers R0, R2, R3 $\rightarrow$ no change |

| LDC        | R0,#01H[RR4]   | ;;;    | $R0 \leftarrow$ contents of program memory location 0061H<br>(01H + RR4),<br>R0 = AAH, R2 = 00H, R3 = 60H                           |

| LDE        | R0,#01H[RR4]   | ;;     | $R0 \leftarrow$ contents of external data memory location 0061H (01H + RR4), R0 = BBH, R4 = 00H, R5 = 60H                           |

| LDC (note) | #01H[RR4],R0   | ;<br>; | 11H (contents of R0) is loaded into program memory location 0061H (01H + 0060H)                                                     |

| LDE        | #01H[RR4],R0   | ;;     | 11H (contents of R0) is loaded into external data memory location 0061H (01H + 0060H)                                               |

| LDC        | R0,#1000H[RR2] | ;;     | $R0 \leftarrow$ contents of program memory location 1104H<br>(1000H + 0104H), $R0 = 88H$ , $R2 = 01H$ , $R3 = 04H$                  |

| LDE        | R0,#1000H[RR2] | ;;     | $R0 \leftarrow$ contents of external data memory location 1104H (1000H + 0104H), $R0 = 98H$ , $R2 = 01H$ , $R3 = 04H$               |

| LDC        | R0,1104H       | ;      | R0 $\leftarrow$ contents of program memory location 1104H, R0 = 88H                                                                 |

| LDE        | R0,1104H       | ;;     | R0 $\leftarrow$ contents of external data memory location 1104H,<br>R0 = 98H                                                        |

| LDC (note) | 1105H,R0       | ;;     | 11H (contents of R0) is loaded into program memory location 1105H, (1105H) $\leftarrow$ 11H                                         |

| LDE        | 1105H,R0       | ;;     | 11H (contents of R0) is loaded into external data memory location 1105H, (1105H) $\leftarrow$ 11H                                   |

|            |                |        |                                                                                                                                     |

NOTE: These instructions are not supported by masked ROM type devices.

# LDCD/LDED — Load Memory and Decrement

### LDCD/LDED dst,src

**Operation:** dst  $\leftarrow$  src

$rr \leftarrow rr - 1$

These instructions are used for user stacks or block transfers of data from program or data memory to the register file. The address of the memory location is specified by a working register pair. The contents of the source location are loaded into the destination location. The memory address is then decremented. The contents of the source are unaffected.

LDCD references program memory and LDED references external data memory. The assembler makes "Irr" an even number for program memory and an odd number for data memory.

### Flags: No flags are affected.

#### Format:

|     |           | Bytes | Cycles | Opcode<br>(Hex) | Addr<br><u>dst</u> |     |

|-----|-----------|-------|--------|-----------------|--------------------|-----|

| орс | dst   src | 2     | 10     | E2              | r                  | Irr |

**Examples:** Given: R6 = 10H, R7 = 33H, R8 = 12H, program memory location 1033H = 0CDH, and external data memory location 1033H = 0DDH:

| LDCD | R8,@RR6 | ; | 0CDH (contents of program memory location 1033H) is loaded<br>into R8 and RR6 is decremented by one<br>R8 = 0CDH, R6 = 10H, R7 = 32H (RR6 $\leftarrow$ RR6 - 1) |

|------|---------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDED | R8,@RR6 | ; | 0DDH (contents of data memory location 1033H) is loaded<br>into R8 and RR6 is decremented by one (RR6 $\leftarrow$ RR6 – 1)<br>R8 = 0DDH, R6 = 10H, R7 = 32H    |

# LDCI/LDEI - LOAD MEMORY AND INCREMENT

LDCI/LDEI dst,src

**Operation:** dst  $\leftarrow$  src

$rr \leftarrow rr + 1$

These instructions are used for user stacks or block transfers of data from program or data memory to the register file. The address of the memory location is specified by a working register pair. The contents of the source location are loaded into the destination location. The memory address is then incremented automatically. The contents of the source are unaffected.

LDCI refers to program memory and LDEI refers to external data memory. The assembler makes "Irr" even for program memory and odd for data memory.

Flags: No flags are affected.

### Format:

|     |           | Bytes | Cycles | Opcode | Addr Mode  |            |

|-----|-----------|-------|--------|--------|------------|------------|

|     |           |       |        | (Hex)  | <u>dst</u> | <u>src</u> |

| орс | dst   src | 2     | 10     | E3     | r          | Irr        |

|           | 1034H  | = 0C5H | ; externa | al data i | memor  | y loca | ations  | 1033H  | = 0   | DDH a    | and 1 | 034H  | I = C | )D5H: |     |   |

|-----------|--------|--------|-----------|-----------|--------|--------|---------|--------|-------|----------|-------|-------|-------|-------|-----|---|

| Examples: | Given: | R6 = 1 | 0H, R7    | = 33H,    | , R8 = | 12H    | , progi | ram me | emory | / locati | ons ' | 1033H | H = ( | 0CDH  | and | ł |

| LDCI | R8,@RR6 | <ul> <li>; 0CDH (contents of program memory location 1033H) is loaded</li> <li>; into R8 and RR6 is incremented by one (RR6 ← RR6 + 1)</li> <li>; R8 = 0CDH, R6 = 10H, R7 = 34H</li> </ul> |

|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDEI | R8,@RR6 | ; 0DDH (contents of data memory location 1033H) is loaded<br>; into R8 and RR6 is incremented by one (RR6 $\leftarrow$ RR6 + 1)<br>; R8 = 0DDH, R6 = 10H, R7 = 34H                         |

# $\mathbf{NOP} - \mathbf{No}$ Operation

NOP

**Operation:** No action is performed when the CPU executes this instruction. Typically, one or more NOPs are executed in sequence in order to effect a timing delay of variable duration.

Flags: No flags are affected.

Format:

|     | Bytes | Cycles | Opcode<br>(Hex) |

|-----|-------|--------|-----------------|

| орс | 1     | 4      | FF              |

**Example:** When the instruction

NOP

is encountered in a program, no operation occurs. Instead, there is a delay in instruction execution time.

# $\mathbf{OR}$ — Logical OR

OR dst,src

**Operation:** dst  $\leftarrow$  dst OR src

The source operand is logically ORed with the destination operand and the result is stored in the destination. The contents of the source are unaffected. The OR operation results in a "1" being stored whenever either of the corresponding bits in the two operands is a "1"; otherwise a "0" is stored.

- Flags: C: Unaffected.

- **Z:** Set if the result is "0"; cleared otherwise.

- **S:** Set if the result bit 7 is set; cleared otherwise.

- V: Always cleared to "0".

### Format:

|     |           |     | Byte | es Cycle | s Opcod<br>(Hex) |   | r Mode<br><u>src</u> |

|-----|-----------|-----|------|----------|------------------|---|----------------------|

| орс | dst   src |     | 2    | 4        | 42               | r | r                    |

|     |           |     |      | 6        | 43               | r | lr                   |

| орс | SIC       | dst | 3    | 6        | 44               | R | R                    |

|     |           |     |      | 6        | 45               | R | IR                   |

| орс | dst       | src | 3    | 6        | 46               | R | IM                   |

# **Examples:** Given: R0 = 15H, R1 = 2AH, R2 = 01H, register 00H = 08H, register 01H = 37H, and register 08H = 8AH:

| OR | R0,R1    | $\rightarrow$ | R0 = 3FH, R1 = 2AH                      |

|----|----------|---------------|-----------------------------------------|

| OR | R0,@R2   | $\rightarrow$ | R0 = 37H, R2 = 01H, register 01H = 37H  |

| OR | 00H,01H  | $\rightarrow$ | Register 00H = 3FH, register 01H = 37H  |

| OR | 01H,@00H | $\rightarrow$ | Register 00H = 08H, register 01H = 0BFH |

| OR | 00H,#02H | $\rightarrow$ | Register 00H = 0AH                      |

In the first example, if working register R0 contains the value 15H and register R1 the value 2AH, the statement "OR R0,R1" logical-ORs the R0 and R1 register contents and stores the result (3FH) in destination register R0.

The other examples show the use of the logical OR instruction with the various addressing modes and formats.

# **POP** – Pop From Stack

dst

POP

**Operation:** d

dst  $\leftarrow$  @SP SP  $\leftarrow$  SP + 1

The contents of the location addressed by the stack pointer are loaded into the destination. The stack pointer is then incremented by one.

### Flags: No flags affected.

### Format:

|     |     | Bytes | Cycles | Opcode<br>(Hex) | Addr Mode<br><u>dst</u> |

|-----|-----|-------|--------|-----------------|-------------------------|

| орс | dst | 2     | 8      | 50              | R                       |

|     |     |       | 8      | 51              | IR                      |

| Examples: | Given: Register 00H = 01H, register 01H = 1BH, SP (0D9H) = 0BBH, and stack register |

|-----------|-------------------------------------------------------------------------------------|

|           | 0BBH = 55H:                                                                         |

| POP | 00H  | $\rightarrow$ | Register 00H = $55H$ , SP = $0BCH$                |

|-----|------|---------------|---------------------------------------------------|

| POP | @00H | $\rightarrow$ | Register 00H = 01H, register 01H = 55H, SP = 0BCH |

In the first example, general register 00H contains the value 01H. The statement "POP 00H" loads the contents of location 0BBH (55H) into destination register 00H and then increments the stack pointer by one. Register 00H then contains the value 55H and the SP points to location 0BCH.

# **PUSH** — Push To Stack

| PUSH      | src |

|-----------|-----|

| 1 0 0 1 1 | 310 |

**Operation:** SP  $\leftarrow$  SP -1

$@SP \leftarrow src$

A PUSH instruction decrements the stack pointer value and loads the contents of the source (src) into the location addressed by the decremented stack pointer. The operation then adds the new value to the top of the stack.

### Flags: No flags are affected.

### Format:

|     |     | Bytes | Cycles | Opcode<br>(Hex) | Addr Mode<br><u>dst</u> |

|-----|-----|-------|--------|-----------------|-------------------------|

| орс | src | 2     | 8      | 70              | R                       |

|     |     |       | 8      | 71              | IR                      |

| Examples: | Given: Register 40H = 4FH, register 4FH = 0AAH, SP = 0C0H: |  |

|-----------|------------------------------------------------------------|--|

|-----------|------------------------------------------------------------|--|

| PUSH | 40H  | $\rightarrow$ | Register 40H = 4FH, stack register 0BFH = 4FH,<br>SP = 0BFH                    |

|------|------|---------------|--------------------------------------------------------------------------------|

| PUSH | @40H | $\rightarrow$ | Register 40H = 4FH, register 4FH = 0AAH, stack register 0BFH = 0AAH, SP = 0BFH |

In the first example, if the stack pointer contains the value 0C0H, and general register 40H the value 4FH, the statement "PUSH 40H" decrements the stack pointer from 0C0 to 0BFH. It then loads the contents of register 40H into location 0BFH. Register 0BFH then contains the value 4FH and SP points to location 0BFH.

# RCF — Reset Carry Flag

| RCF      |                    | RCF                                               |                |             |                 |

|----------|--------------------|---------------------------------------------------|----------------|-------------|-----------------|

| Operatio | n:                 | $C \leftarrow 0$                                  |                |             |                 |

|          |                    | The carry flag is cleared to logic zero, regardle | ss of its prev | ious value. |                 |

| Flags:   | C: Cleared to "0". |                                                   |                |             |                 |

|          |                    | No other flags are affected.                      |                |             |                 |

| Format:  |                    |                                                   |                |             |                 |

|          |                    |                                                   | Bytes          | Cycles      | Opcode<br>(Hex) |

|          |                    | орс                                               | 1              | 4           | CF              |

|          |                    |                                                   |                |             |                 |

**Example:** Given: C = "1" or "0":

The instruction RCF clears the carry flag (C) to logic zero.

## $\mathbf{RET} - \mathbf{Return}$

## RET

**Operation:**  $PC \leftarrow @SP$

$SP \leftarrow SP + 2$

The RET instruction is normally used to return to the previously executing procedure at the end of a procedure entered by a CALL instruction. The contents of the location addressed by the stack pointer are popped into the program counter. The next statement that is executed is the one that is addressed by the new program counter value.

Flags: No flags are affected.

## Format:

|     | Bytes | Cycles | Opcode<br>(Hex) |

|-----|-------|--------|-----------------|

| орс | 1     | 8      | AF              |

|     |       | 10     |                 |

Example: Given: SP = 0BCH, (SP) = 101AH, and PC = 1234:

RET  $\rightarrow$  PC = 101AH, SP = 0BEH

The statement "RET" pops the contents of stack pointer location 0BCH (10H) into the high byte of the program counter. The stack pointer then pops the value in location 0BDH (1AH) into the PC's low byte and the instruction at location 101AH is executed. The stack pointer now points to memory location 0BEH.

## RL — Rotate Left

RL

dst

Operation: (

$\begin{array}{l} \mathsf{C} \ \leftarrow \ \mathsf{dst} \ (7) \\ \mathsf{dst} \ (0) \ \leftarrow \ \mathsf{dst} \ (7) \end{array}$

dst (n + 1)  $\leftarrow$  dst (n), n = 0-6

The contents of the destination operand are rotated left one bit position. The initial value of bit 7 is moved to the bit zero (LSB) position and also replaces the carry flag.

- Flags: C: Set if the bit rotated from the most significant bit position (bit 7) was "1".

- Z: Set if the result is "0"; cleared otherwise.

- S: Set if the result bit 7 is set; cleared otherwise.

- V: Set if arithmetic overflow occurred, that is, if the sign of the destination changed during rotation; cleared otherwise.

#### Format:

|     |     | Bytes | Cycles | Opcode<br>(Hex) | Addr Mode<br><u>dst</u> |

|-----|-----|-------|--------|-----------------|-------------------------|

| орс | dst | 2     | 4      | 90              | R                       |

|     |     |       | 4      | 91              | IR                      |

| Examples: | Given: R | egister 00H = | = 0AAH        | register 01H = 02H and register 02H = 17H:      |

|-----------|----------|---------------|---------------|-------------------------------------------------|

|           | RL       | 00H           | $\rightarrow$ | Register 00H = 55H, C = "1"                     |

|           | RL       | @01H          | $\rightarrow$ | Register 01H = 02H, register 02H = 2EH, C = "0" |

In the first example, if general register 00H contains the value 0AAH (10101010B), the statement "RL 00H" rotates the 0AAH value left one bit position, leaving the new value 55H (01010101B) and setting the carry and overflow flags.

dst

## RLC — Rotate Left Through Carry

RLC

**Operation:** dst (0)  $\leftarrow$  C

$dst(0) \leftarrow C$  $C \leftarrow dst(7)$

dst (n + 1)  $\leftarrow$  dst (n), n = 0-6

The contents of the destination operand with the carry flag are rotated left one bit position. The initial value of bit 7 replaces the carry flag (C); the initial value of the carry flag replaces bit zero.

- Flags: C: Set if the bit rotated from the most significant bit position (bit 7) was "1".

- **Z:** Set if the result is "0"; cleared otherwise.

- S: Set if the result bit 7 is set; cleared otherwise.

- V: Set if arithmetic overflow occurred, that is, if the sign of the destination changed during rotation; cleared otherwise.

## Format:

|     |     | Bytes | Cycles | Opcode<br>(Hex) | Addr Mode<br><u>dst</u> |

|-----|-----|-------|--------|-----------------|-------------------------|

| орс | dst | 2     | 4      | 10              | R                       |

|     |     |       | 4      | 11              | IR                      |

| Examples: | Given: Register 00H = 0AAH, register 01H = 02H, and register 02H = 17H, C = "0": |

|-----------|----------------------------------------------------------------------------------|

|           |                                                                                  |

RLC 00H  $\rightarrow$  Register 00H = 54H, C = "1"

RLC @01H  $\rightarrow$  Register 01H = 02H, register 02H = 2EH, C = "0"

In the first example, if general register 00H has the value 0AAH (10101010B), the statement "RLC 00H" rotates 0AAH one bit position to the left. The initial value of bit 7 sets the carry flag and the initial value of the C flag replaces bit zero of register 00H, leaving the value 55H (01010101B). The MSB of register 00H resets the carry flag to "1" and sets the overflow flag.

## RR — Rotate Right

RR

dst

Operation: (

$C \leftarrow dst (0)$ dst (7)  $\leftarrow dst (0)$

dst (n)  $\leftarrow$  dst (n + 1), n = 0-6

The contents of the destination operand are rotated right one bit position. The initial value of bit zero (LSB) is moved to bit 7 (MSB) and also replaces the carry flag (C).

- Flags: C: Set if the bit rotated from the least significant bit position (bit zero) was "1".

- Z: Set if the result is "0"; cleared otherwise.

- S: Set if the result bit 7 is set; cleared otherwise.

- V: Set if arithmetic overflow occurred, that is, if the sign of the destination changed during rotation; cleared otherwise.

#### Format:

|     |     | Bytes | Cycles | Opcode<br>(Hex) | Addr Mode<br><u>dst</u> |

|-----|-----|-------|--------|-----------------|-------------------------|

| орс | dst | 2     | 4      | E0              | R                       |

|     |     |       | 4      | E1              | IR                      |

| Examples: | Given: | Register 00H = | 31H, register 01H = | 02H, and register $02H = 17H$ : |

|-----------|--------|----------------|---------------------|---------------------------------|

|-----------|--------|----------------|---------------------|---------------------------------|

| RR | 00H  | $\rightarrow$ | Register 00H = 98H, C = "1"                     |

|----|------|---------------|-------------------------------------------------|

| RR | @01H | $\rightarrow$ | Register 01H = 02H, register 02H = 8BH, C = "1" |

In the first example, if general register 00H contains the value 31H (00110001B), the statement "RR 00H" rotates this value one bit position to the right. The initial value of bit zero is moved to bit 7, leaving the new value 98H (10011000B) in the destination register. The initial bit zero also resets the C flag to "1" and the sign flag and overflow flag are also set to "1".

## **RRC** — Rotate Right Through Carry

RRC dst

**Operation:** dst (7)  $\leftarrow$  C

$C \leftarrow dst(0)$

dst (n)  $\leftarrow$  dst (n + 1), n = 0-6

The contents of the destination operand and the carry flag are rotated right one bit position. The initial value of bit zero (LSB) replaces the carry flag; the initial value of the carry flag replaces bit 7 (MSB).

- Flags: C: Set if the bit rotated from the least significant bit position (bit zero) was "1".

- Z: Set if the result is "0" cleared otherwise.

- S: Set if the result bit 7 is set; cleared otherwise.

- V: Set if arithmetic overflow occurred, that is, if the sign of the destination changed during rotation; cleared otherwise.

#### Format:

|     |     | Bytes | Cycles | Opcode<br>(Hex) | Addr Mode<br><u>dst</u> |

|-----|-----|-------|--------|-----------------|-------------------------|

| орс | dst | 2     | 4      | C0              | R                       |

|     |     |       | 4      | C1              | IR                      |

| Examples: | Given: Register 00H | = 55H, register 01H = | = 02H, register 02H = | 17H, and C = "0": |

|-----------|---------------------|-----------------------|-----------------------|-------------------|

|           |                     |                       |                       |                   |

| RRC | 00H  | $\rightarrow$ | Register 00H = 2AH, C = "1"                     |

|-----|------|---------------|-------------------------------------------------|

| RRC | @01H | $\rightarrow$ | Register 01H = 02H, register 02H = 0BH, C = "1" |

In the first example, if general register 00H contains the value 55H (01010101B), the statement "RRC 00H" rotates this value one bit position to the right. The initial value of bit zero ("1") replaces the carry flag and the initial value of the C flag ("1") replaces bit 7. This leaves the new value 2AH (00101010B) in destination register 00H. The sign flag and overflow flag are both cleared to "0".

## **SBC** — Subtract With Carry

SBC dst,src

**Operation:** dst  $\leftarrow$  dst - src - c

The source operand, along with the current value of the carry flag, is subtracted from the destination operand and the result is stored in the destination. The contents of the source are unaffected. Subtraction is performed by adding the two's-complement of the source operand to the destination operand. In multiple precision arithmetic, this instruction permits the carry ("borrow") from the subtraction of the low-order operands to be subtracted from the subtraction of high-order operands.

- **Flags:** C: Set if a borrow occurred (src > dst); cleared otherwise.

- **Z:** Set if the result is "0"; cleared otherwise.

- **S:** Set if the result is negative; cleared otherwise.

- V: Set if arithmetic overflow occurred, that is, if the operands were of opposite sign and the sign of the result is the same as the sign of the source; cleared otherwise.

#### Format:

| _   |           |     | B | lytes | Cycles | Opcode<br>(Hex) | Addr<br><u>dst</u> | Mode<br><u>src</u> |

|-----|-----------|-----|---|-------|--------|-----------------|--------------------|--------------------|

| орс | dst   src |     |   | 2     | 4      | 32              | r                  | r                  |