## Feedback-Loop Stabilization

#### 12.1 Introduction

Before going into the details of stabilizing a feedback loop, it is of interest to consider in a semiquantitative way, why a feedback loop may oscillate.

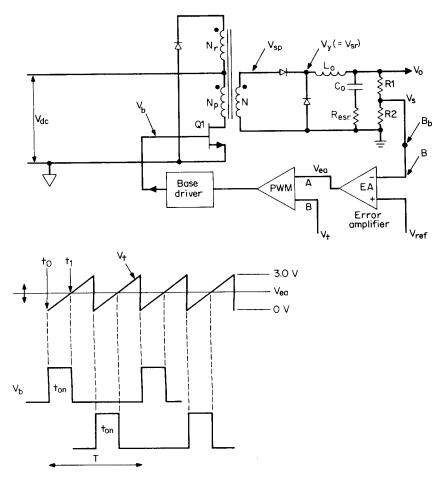

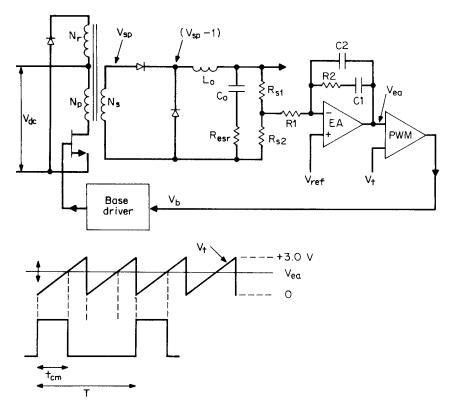

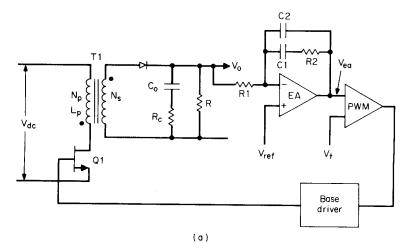

Consider the negative-feedback loop for a typical forward converter in Fig. 12.1. The essential error-amplifier and PWM functions are contained in all pulse-width-modulating chip. The chip also provide many other functions, but for understanding the stability problem, only the error amplifier and pulse-width modulator need be considered.

For slow or DC variations of the output voltage  $V_o$ , the loop is, of course, stable. A small, slow variation of  $V_o$  due to either line input or load changes will be sensed by the inverting input of error amplifier EA via the sampling network R1, R2 and compared to a reference voltage at the noninverting EA input. This will cause a small change in the DC voltage level  $V_{\rm ea}$  at the EA output and at the A input to the pulse-width-modulator PWM.

The PWM, as described heretofore, compares that DC voltage level to a roughly 0- to 3-V triangle  $V_t$  at its B input. It generates a rectangular pulse whose width  $t_{\rm on}$  is equal to the time from the start of the triangle  $t_0$  until  $t_1$ , the time the triangle crosses the DC voltage level at the B input of the PWM. That pulse fixes the on time of the output transistor of the chip and should also fix the on time of the power transistor.

Thus a slow increase (e.g.) in  $V_{\rm dc}$  causes a slow increase in  $V_{\rm y}$  and hence a slow increase in  $V_o$  since  $V_o \cong V_{\rm y} t_{\rm on}/T$ . The increase in  $V_o$  causes an increase in  $V_s$  and hence a decrease in  $V_{\rm ea}$ . Since  $t_{\rm on}$  is the time from the start of the triangle to  $t_1$ , this causes a decrease in  $t_{\rm on}$  and restores  $V_o$  to its original value. Similarly, of course, a decrease in  $V_{\rm dc}$  causes an increase in  $t_{\rm on}$  to maintain  $V_o$  constant.

Figure 12.1 A closed feedback loop in a typical forward converter.

Drive to the power transistor may be taken from either the emitter or the collector of the chip's output transistor via a current-amplifying base driver. But from whichever point—emitter or collector—output is taken, it must be ensured that polarities are such that an increase in  $V_{\rm o}$  causes a decrease in  $t_{\rm on}$ .

Note that most PWM chips have their output transistors on for the time from  $t_0$  to  $t_1$ . With such chips,  $V_s$  is fed to the inverting EA input and for an NPN power transistor, its base (or gate if a MOSFET) is driven from the emitter of the chip's output transistor.

In some PWM chips (TL494 family), however, the output transistor is on from the time the triangle at the  $V_t$  input to the PWM crosses the  $V_{\rm ea}$  level  $(t_1)$  until the end of the triangle at  $t_2$ . With such chips, if the

NPN power transistor were to be turned on when the chip output transistor was on (drive from the chip transistor's emitter), that would cause the power transistor on time to increase as  $V_{\rm dc}$  increased. This, of course, would be positive rather than negative feedback.

Thus, with chips of the TL494 family,  $V_s$  is fed to the noninverting input to the EA. This causes the output transistor on time to decrease as  $V_o$  increases and permits the power transistor to be driven from the chip transistor's emitter.

The circuit in Fig. 12.1 thus provides negative feedback and a stable circuit at low frequencies. But within the loop, there exist low-level noise voltages or possible voltage transients which have a continuous spectrum of sinusoidal Fourier components. All these Fourier components suffer gain changes and phase shifts in the  $L_o$ ,  $C_o$  output filter, the error amplifier, and the PWM from  $V_{\rm ea}$  to  $V_{\rm sr}$ . At one of these Fourier components, the gain and phase shifts can result in positive rather than negative feedback and thereby result in oscillation as described below.

### 12.2 Mechanism of Loop Oscillation

Consider the forward converter feedback loop of Fig. 12.1. Assume for a moment that the loop is broken open at point B, the inverting input to the error amplifier. At any of the Fourier components of the noise, there is gain and phase shift from B to  $V_{\rm ea}$ , from  $V_{\rm ea}$  to the average voltage at  $V_{\rm sr}$ , and from the average voltage at  $V_{\rm sr}$  through the  $L_o$ ,  $C_o$  filter around back to  $B_b$  (just before the loop break).

Now assume that a signal of some frequency  $f_1$  is injected into the loop at B and comes back around as an echo at  $B_b$ . The echo is modified in phase and gain by all the previously mentioned elements in the loop. If the modified echo has returned exactly in phase with and is equal in amplitude to the signal which started the echo, if the loop is now closed ( $B_b$  closed to B) and the injected signal is removed, the circuit will continue to oscillate at the frequency  $f_1$ . The initial signal which starts the echo and maintains the oscillation is the  $f_1$  Fourier component in the noise spectrum.

#### 12.2.1 Gain criterion for a stable circuit

Thus the first criterion for a stable loop is that at the frequency where the total open-loop gain is unity (the *crossover frequency*), the total open-loop phase shift of all elements involved must be less than  $360^{\circ}$ . The amount by which the total phase shift is less than  $360^{\circ}$  (at the frequency where the total open-loop gain is unity) is called the *phase margin*.

To ensure a stable loop under worst-case tolerances of the associated components, the usual practice is to design for at least a 35° to 45° phase margin with nominal components.

### 12.2.2 Gain slope criteria for a stable circuit

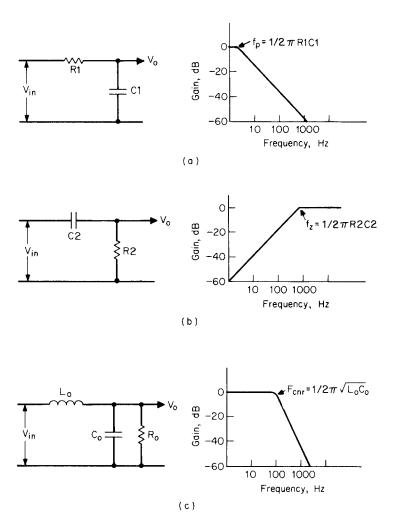

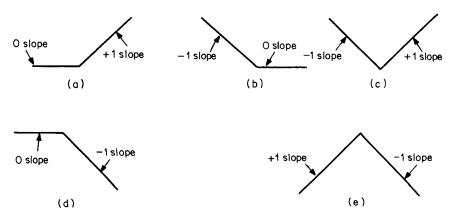

At this point, a universally used jargon expression describing the gain slope is introduced. Gain versus frequency is usually plotted in decibels (dB) on semilog paper as in Fig. 12.2. If the scales are such that a linear distance of 20 dB (numerical gain of 10) is equal to the linear distance of a factor of 10 in frequency, lines representing gain variations of  $\pm 20$  dB/decade have slopes of  $\pm 1$ . Circuit configurations having a gain variation of  $\pm 20$  dB per decade are thus described as having " $\pm 1$  gain slopes."

An elementary circuit having a gain slope of -1 (beyond the frequency  $f_p = 1/2\pi R1C1$ ) between output and input is the RC integrator of Fig. 12.2a. The RC differentiator of Fig. 12.2b has a +1 gain slope (below the frequency  $f_z = 1/2\pi R2C2$ ) or a gain variation of +20 dB/decade between output and input. Such circuits have only 20 dB/decade gain variations because as frequency increases or decreases by a factor of 10, the capacitor impedance decreases or increases by a factor of 10 but the resistor impedance remains constant.

A circuit which has a -2 or -40 dB/decade gain slope (beyond the frequency  $F_o = 1/2\pi\sqrt{L_oC_o}$ ) is the output LC filter (Fig. 12.2c), which has no resistance (ESR) in its output capacitor. This, of course, is because as frequency increases by a factor of 10, the inductor impedance increases and the capacitor impedance decreases by a factor of 10.

Now gain and phase shift versus frequency for an  $L_oC_o$  filter are plotted in Fig. 12.3a and 12.3b for various values of output resistance  $R_o^2$ . The gain curves are normalized for various ratios of  $k_1 = f/F_o$  where  $F_o = 1/2\pi\sqrt{L_oC_o}$  and for various ratios  $k_2 = R_o/\sqrt{L_o/C_o}$ .

Figure 12.3a shows that whatever the value of  $k_2$ , all gain curves, beyond the so-called corner frequency of  $F_o=1/2\pi\sqrt{L_oC_o}$  asymptotically approach a slope of -2 (-40 dB/decade). The circuit for  $k_2=1.0$  is referred to as the *critically damped* circuit. The critically damped circuit has a very small resonant "bump" in gain and at the corner frequency  $F_o$ , starts immediately falling at a -2 slope.

For  $k_2$  greater than 1 the circuit is described as *underdamped*. It is seen that underdamped LC filters can have a very large resonant bump in gain at  $F_o$ .

Circuits of  $k_2$  less than 1.0 are *overdamped*. It is seen in Fig. 12.3a that overdamped LC filters also asymptotically approach a gain slope of -2. But for a heavily overdamped ( $k_2 = 0.1$ ) filter, the frequency at

Figure 12.2 (a) An RC integrator has a gain  $dV_o/dV_{\rm in}$  of -20 dB/decade beyond  $F_p = \frac{1}{2}\pi R1C1$ . If the scales are such that 20 dB is the same linear distance as 1 decade in frequency, a gain slope of -20 dB/decade has a -1 slope. Such a circuit is referred to as a -1 slope circuit. (b) An RC differentiator has a gain of +20 dB/decade. At  $F_z = 1/2\pi R2C2$ , where  $X_{C2} = R_2$ , gain asymptotically approaches 0 dB. If scales are such that 20 dB is the same linear distance as 1 decade in frequency, a gain slope of +20 dB/decade has a +1 slope. Such a circuit is referred to as a +1 slope circuit. (c) An LC filter has a gain  $(dV_o/dV_{\rm in})$  of unity (0 dB) up to its corner frequency of  $F_{\rm cnr} = 1/2\pi \sqrt{L_o}C_o$  when critically damped  $(R_o = \sqrt{L_o/C_o})$ . Beyond  $F_{\rm cnr}$  it commences falling at a rate of -40 dB/decade. This is so because for every decade increase in frequency,  $X_L$  increased and  $X_c$  decreases in impedance by a factor of 10. If scales are such that 20 dB is the same linear distance as 1 decade in frequency, a gain slope of -40 dB/decade has a -2 slope. Such a circuit is referred to as a -2 slope circuit.

Figure 12.3 (a) Gain versus frequency for switching regulator LC filter. (b) Phase shift versus frequency for switching regulator LC filter. (Courtesy Switchtronix Press).

which the gain slope has come close to -2 is about 20 times the corner frequency  $F_o$ .

Figure 12.3b shows phase shift versus normalized frequency  $(f/F_o)$  again for various ratios of  $k_2 = R_o/\sqrt{L_o/C_o}$ . It is seen for any value of  $k_2$ , that the phase shift between output and input is 90° at the corner frequency  $(F_o = 1/2\pi\sqrt{L_o/C_o})$ . And for highly underdamped filters  $(R_o)$  greater than  $\sim 5\sqrt{L_o/C_o}$ , phase shift varies very rapidly with frequency. The shift is already 170° at a frequency of  $1.5F_o$  for  $R_o = 5\sqrt{L_o/C_o}$ .

In contrast, a circuit with a -1 gain slope can never yield more than a 90° phase shift, and its rate of change of phase shift with frequency is far slower than that of a circuit -2 gain slope as exemplified in Fig. 12.3b.

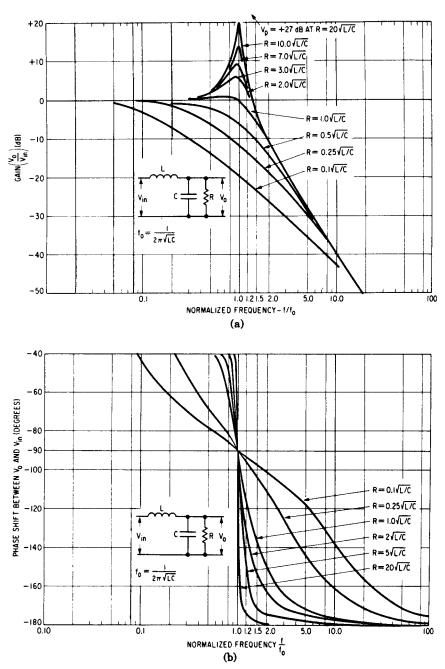

This leads to the second criterion for a stable circuit. The first criterion was that the total phase shift at the crossover frequency (frequency where total open-loop gain is unity or 0 dB) should be short of 360° by the "phase margin," which is usually taken as at least 45°.

This second criterion for a stable circuit is that to prevent rapid changes of phase shift with frequency characteristic of a circuit with a -2 gain slope, the slope of the open-loop gain-frequency curve of the entire circuit (arithmetic sum in decibels of all the gain elements involved) as it passes through crossover frequency should be -1. This is shown in Fig. 12.4.

It is not an absolute requirement that the total open-loop gain curve must come through crossover at a -1 gain slope. But it does provide insurance that if any phase-shift elements have been overlooked, the small phase shift and relatively slow phase-shift-frequency curve characteristic of a -1 gain slope element will still preserve an adequate phase margin.

The third criterion for a stable loop is to provide the desired phase margin, which will be set at 45° herein (Fig. 12.4).

To satisfy all three criteria, it is necessary to know how to calculate gains and phase shifts of all the elements in Fig. 12.1. This is shown below.

## 12.2.3 Gain characteristic of *LC* output filter with and without equivalent series resistance (ESR) in output capacitor

Aside from the flyback (which has an output capacitor filter only), all topologies discussed herein have an output LC filter. The gain-versus-frequency characteristic of this output LC filter is of fundamental importance. It must be calculated first as it determines how the gain and phase shift-versus-frequency characteristics of the error amplifier must be shaped to satisfy the three criteria for a stable loop.

Figure 12.4 Total open-loop gain and phase shift. The frequency at which the total open-loop gain is 0 dB ( $F_{\rm co}$ ) is forced to be 0 dB is usually chosen one-fourth and one-fifth the switching frequency. For loop to be stable, total open-loop phase shift at  $F_{\rm co}$  should be short of 360° by as large a value as possible. The amount by which it is short of 360° is the *phase margin*. A usual phase margin to strive for is 45°. A second criterion for a stable loop is that the total open-loop gain pass through  $F_{\rm co}$  at a -1 slope.

The gain characteristic of an output LC filter with various output load resistances is shown in Fig. 12.3a. This curve assumes that the output capacitor has zero equivalent series resistance (ESR). For the purpose of this discussion, it is sufficiently accurate to assume that the filter is critically damped, that is,  $R_o = 1.0 \sqrt{L_o/C_o}$ . If the circuit is made stable for the gain curve corresponding to  $R_o = 1.0 \sqrt{L_o/C_o}$ , it will be stable at other loads. Nevertheless, the circuit merits exami-

nation for light loads  $(R_o \gg 1.0 \sqrt{L_o/C_o})$  because of the resonant bump in gain at the LC corner frequency  $F_o = 1/2\pi \sqrt{L_oC_o}$ . This will be considered below.

Thus the gain characteristic of the output LC filter with zero ESR will be drawn as curve 12345 in Fig. 12.5 $\alpha$ . There it is seen that the gain is 0 dB (numerical gain of 1) at DC and low frequencies up to the

Figure 12.5 (a) Gain versus frequency for a critically damped LC filter in which the output capacitor has zero ESR. (b) Gain versus frequency for a critically damped LC filter in which the output capacitor has an equivalent series resistor ( $R_{\rm esr}$ ). When  $C_o$  has an ESR, the gain slope still breaks from horizontal to a -2 slope at  $F_{\rm cnr}$ . But at a frequency  $F_{\rm esr}=1/2\pi$  ( $R_{\rm esr}C_o$ ), it breaks into a -1 slope. This is because at  $F_{\rm esr}$ . The circuit is now an LR rather than an LC circuit. An LR circuit falls at a -1 slope because as frequency increases, the impedance of the series L increases, but that of the shunt R remains constant.

corner frequency  $F_o = 1/2\pi\sqrt{L_oC_o}$ . At DC and frequencies less than  $F_o$ , the impedance of  $C_o$  is much greater than that of  $L_o$  and the output-input gain is unity.

Beyond  $F_o$ , the impedance of  $C_o$  decreases and that of  $L_o$  increases at the rate of 20 dB/decade, making the gain slope fall at the rate of -40 dB/decade or at a -2 slope. Of course, the transition to a -2 slope at  $F_o$  is not as abrupt as shown. The actual gain curve leaves 0 dB smoothly just before  $F_o$  and asymptotically approaches the -2 slope shortly after  $F_o$ . But for the purposes of this discussion, gain will be shown with a relatively abrupt transition as curve 12345 in Fig. 12.5a.

Most filter capacitor types have an internal resistance  $R_{\rm esr}$  in series with their output leads as shown in Fig. 12.5b. This modifies the gain characteristic between the output and input terminals in a characteristic way.

Beyond  $F_o$ , in the lower frequency range where the impedance of  $C_o$  is much greater than  $R_{\rm esr}$ , looking down to ground from  $V_o$ , the only effective impedance is that of  $C_o$ . In this frequency range, the gain still falls at a -2 slope. At higher frequencies, where the impedance of  $C_o$  is less than  $R_{\rm esr}$ , the effective impedance looking down from  $V_o$  to ground is that of  $R_{\rm esr}$  alone. Hence in that frequency range, the circuit is an LR rather than an LC circuit. In that frequency range, the impedance of  $L_o$  increases at the rate of 20 dB/decade but that of  $R_{\rm esr}$  remains constant. Thus in that frequency range, gain falls at a -1 slope.

The break from a -2 to a -1 gain slope occurs at the frequency  $F_{\rm esr} = 1/2\pi R_{\rm esr} C_o$ , where the impedance of  $C_o$  is equal to  $R_{\rm esr}$ . This is shown as  $G_{lc}$  in curve 123456 in Fig. 12.5b. The break in slope from -2 to -1 is, of course, asymptotic, but it is sufficiently accurate to assume it to be abrupt as shown.

### 12.2.4 Pulse-width-modulator gain

In Fig. 12.1, the gain from the error-amplifier output to the average voltage at  $V_{\rm sr}$  (input end of the output inductor) is the PWM gain and is designated as  $G_{\rm pwm}$ .

It may be puzzling how this can be referred to as a *voltage gain*. For at  $V_{\rm ea}$ , there are DC voltage level variations proportional to the erroramplifier input at point B, and at  $V_{\rm sr}$ , there are fixed-amplitude pulses of adjustable width.

The significance and magnitude of this gain can be seen as follows. In Fig. 12.1, the PWM compares the DC voltage level from  $V_{\rm ea}$  to a 3-V triangle at  $V_{\rm e}$ . In all PWM chips which produce two 180° out-of-phase adjustable-width pulses (for driving push-pulls, half or full bridges) these pulses occur once per triangle and have a maximum on or high time of a half period. After the PWM, the pulses are binary-

counted and alternately routed to two separate output terminals (see Fig. 5.2a). In a forward converter, only one of these outputs is used.

Now (Fig. 12.1b), when  $V_{\rm ea}$  is at the bottom of the 3-V triangle, on time or pulse width at  $V_{\rm sr}$  is zero. The average voltage  $V_{\rm av}$  at  $V_{\rm sr}$  is then zero as  $V_{\rm av} = (V_{\rm sp} - 1)(t_{\rm on}/T)$ , where  $V_{\rm sp}$  is the secondary peak voltage. When  $V_{\rm ea}$  has moved up to the top of the 3-V triangle,  $t_{\rm on}/T = 0.5$  and  $V_{\rm av} = 0.5$  ( $V_{\rm sp} - 1$ ). The modulator DC gain  $G_m$ , then, between  $V_{\rm av}$  and  $V_{\rm ea}$  is

$$G_m = \frac{0.5(V_{\rm sp} - 1)}{3} \tag{12.1}$$

This gain is independent of frequency.

There is also a loss  $G_s$  due to the sampling network  $R_1$ ,  $R_2$  in Fig. 12.1. Most of the frequently used PWM chips cannot tolerate more than 2.5 V at the reference input to the error amplifier (point A). Thus, when sampling a +5-V output,  $R_1=R_2$  and gain  $G_s$  between  $V_s$  and  $V_o$  in Fig. 12.1 is -6 dB.

## 12.2.5 Total output *LC* filter plus modulator and sampling network gain

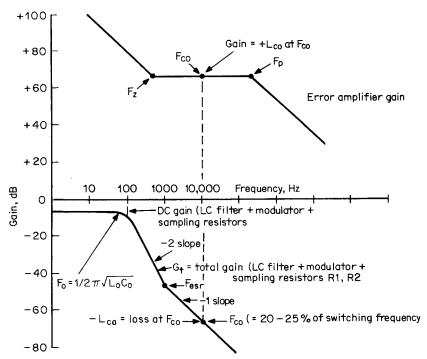

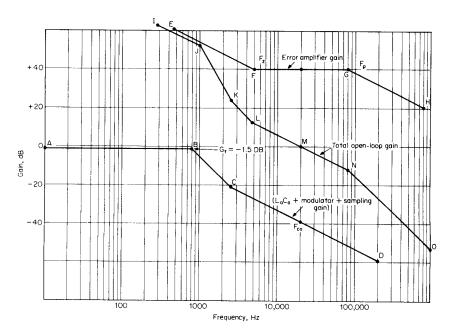

From the above, the total gain  $G_t$  (in decibels) of the output LC filter gain  $G_f$  plus modulator gain  $G_m$  plus sampling network gain  $G_s$  is plotted as in Fig. 12.6. It is equal to  $G_m + G_s$  from DC up to  $F_o = 1/2\pi \sqrt{L_oC_o}$ . At  $F_o$ , it breaks into a -2 slope and remains at that slope up to the frequency  $F_{\rm esr}$  where the impedance of  $C_o$  equals  $R_{\rm esr}$ . At that frequency, it breaks into a -1 slope.

From this curve, the error-amplifier gain and phase-shift-versusfrequency characteristic is established to meet the three criteria for a stable loop as described below.

### 12.3 Shaping Error-Amplifier Gain-Versus-Frequency Characteristic

Recall that the first criterion for a stable loop is that at the frequency  $F_{co}$  where the total open-loop gain is unity (0 dB), total open-loop phase shift must be short of 360° by the desired *phase margin*, which will herein be taken as 45°.

The sequence of steps is then first to establish the crossover frequency  $F_{\rm co}$ , where the total open-loop gain should be 0 dB. Then choose the error-amplifier gain so that the total open-loop gain is forced to be 0 dB at that frequency. Next design the error-amplifier gain slope so that the total open-loop gain comes through  $F_{\rm co}$  at a -1 slope (Fig. 12.4). Finally, tailor the error-amplifier gain versus frequency so that the desired phase margin is achieved.

Figure 12.6 Gain  $G_t$  = sum of (LC filter + modulator + output voltage sampling resistors) gains determines error-amplifier gain. Error-amplifier gain at  $F_{co}$  is made equal and opposite to loss of  $G_t$ . Error-amplifier gain slope at  $F_{co}$  is made horizontal with upward and downward breaks at  $F_z$  and  $F_p$ . Location of  $F_z$  and  $F_p$  in frequency determines total circuit phase margin.

Sampling theory shows that  $F_{\rm co}$  must be less than half the switching frequency for the loop to be stable. But it must be considerably less than that, or there will be large-amplitude switching frequency ripple at the output. Thus, the usual practice is to fix  $F_{\rm co}$  at one-fourth to one-fifth the switching frequency.

Thus, refer to Fig. 12.6, which is the open-loop gain of the LC filter plus the PWM modulator plus the sampling network. The capacitor in the output filter is assumed in Fig. 12.6 to have an ESR which causes a break in the slope from -2 to -1 at  $F_{\rm esr} = 1/2\pi R_{\rm esr} C_o$ . Assume that  $F_{\rm co}$  is one-fifth the switching frequency and read the loss in decibels at that point.

In most cases, the output capacitor will have an ESR and  $F_{\rm esr}$  will come at a lower frequency than  $F_{\rm co}$ . Thus at  $F_{\rm co}$  the  $G_1$  =  $(G_{lc}+G_{\rm pwm}+G_s)$  curve will already have a -1 slope.

Now when gains are plotted in decibels, both gains and gain slopes of gain elements in cascade are additive. Hence, to force crossover frequency to be at the desired one-fifth the switching frequency, choose the error-amplifier gain at  $F_{\rm co}$  to be equal and opposite in decibels to the  $G_t$  =  $(G_{lc}+G_{\rm pwm}+G_s)$  loss at that frequency.

That forces  $F_{co}$  to occur at the desired point. Then, if the error-amplifier gain slope at  $F_{co}$  is horizontal, since the  $G_t$  curve at  $F_{co}$  already has a -1 slope, the sum of the error amplifier plus the  $G_t$  curve comes through crossover frequency at the desired -1 slope and the second criterion for a stable loop has been met.

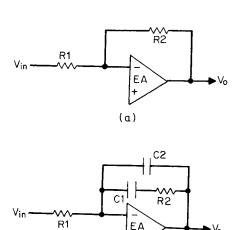

Now the error-amplifier gain has been fixed as equal and opposite to the  $G_t$  loss at  $F_{\rm co}$  and to have a horizontal slope as it passes through  $F_{\rm co}$  (Fig. 12.6). Such a gain characteristic can be achieved with an operational amplifier with a resistor input and resistor feedback as in Fig. 12.7a. Recall that the gain of such an operational amplifier is  $G_{\rm ea} = Z2/Z1 = R2/R1$ . But how far in frequency to the left and right of  $F_{\rm co}$  should it continue to have this constant gain?

Recall that the total open-loop gain is the sum of the error-amplifier gain plus  $G_1$  gain. If the error-amplifier gain remained constant down to DC, the total open-loop gain would not be very large at 120 Hz—the frequency of the AC power line ripple.

Yet it is desired to keep power line ripple attenuated down to a very low level at the output. To degenerate the 120-Hz ripple sufficiently, the open-loop gain at that frequency should be as high as possible. Thus at some frequency to the left of  $F_{\rm co}$ , the error-amplifier gain should be permitted to increase rapidly.

This can be done by placing a capacitor C1 in series with R2 (Fig. 12.7b). This yields the low-frequency gain characteristic shown in Fig. 12.6. In the frequency range where the impedance of C1 is small compared to R2, the gain is horizontal and simply equal to R2/R1. At

(b)

Figure 12.7 (a) Error amplifier with resistor feedback R2 and resistor input R1 arms have a gain equal to R2/R1 which is independent of frequency up to the frequency where the open-loop error amplifier inside the loop (EA) commences falling off the gain. (b) Using complex feedback and input arms permits shaping the gain-versus-frequency and phase-shift-versus-frequency curves. The configuration above has the gain-versus-frequency characteristic of Fig. 12.6.

lower frequencies where the impedance of C2 is much higher than R2, effectively R2 is out of the circuit and the gain is  $X_{cI}/R_1$ . This gain increases at the rate of +20 dB/decade ( + 1 slope) toward lower frequencies and yields the higher gain at 120 Hz. Going in the direction of higher frequency, the -1 gain slope breaks and becomes horizontal at a frequency of  $F_z = 1/2\pi R2C1$ .

Now going to the right of  $F_{\rm co}$  toward higher frequency (Fig. 12.6), if the error-amplifier gain curve were permitted to remain horizontal, total open-loop gain would remain relatively high at the high frequencies. But high gain at high frequencies is undesirable as thin, high-frequency noise spikes would be picked up and transmitted at large amplitudes to the output. Thus gain should be permitted to fall off at high frequencies.

This is easily done by placing a capacitor C2 across the series combination of R2 and C1 (Fig. 12.7b). At  $F_{co}$ ,  $X_{c1}$  is already small compared to R2 and C1 is effectively out of the circuit.

At higher frequencies where  $X_{c2}$  is small compared to R2, however, R2 is effectively out of the circuit and gain is  $X_{c2}/R_1$ . Now the gain characteristic beyond  $F_{co}$  is horizontal up to a frequency  $F_p$  (=1/2 $\pi$ R2C2), where it breaks and thereafter falls at a -1 slope as can be seen in Fig. 12.6. This lower gain at high frequency keeps high-frequency noise spikes from coming through to the output.

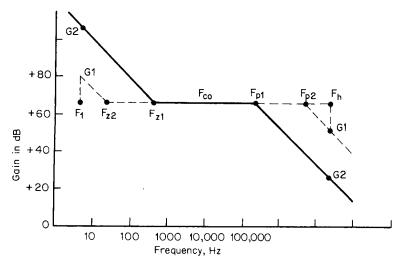

Now the break frequencies  $F_z$  and  $F_p$  must be chosen. They will be chosen so that  $F_{\rm co}/F_z = F_p/F_{\rm co}$ . The farther apart  $F_z$  and  $F_p$  are, the greater the phase margin at  $F_{\rm co}$ . Large phase margins are desirable, but if  $F_z$  is chosen too low, low-frequency gain will be lower at 120 Hz than if a higher frequency were chosen (Fig. 12.8). Thus 120-Hz attenuation will be poorer. If  $F_p$  is chosen too high, gain at high frequencies is higher than if a lower  $F_p$  is chosen (Fig. 12.8). Thus high-frequency noise spikes would come through at a higher amplitude.

Thus a compromise between separating  $F_z$  and  $F_p$  by a large amount to increase phase margin and decreasing the separation to achieve better 120-Hz attenuation and lower-amplitude high-frequency noise spikes is sought.

This compromise and a more exact analysis of the problem is made easy by introducing the concept of transfer functions, poles, and zeros as shown below.

## 12.4 Error-Amplifier Transfer Function, Poles, and Zeros

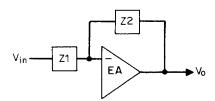

The circuit of an operational amplifier with a complex impedance  $Z_1$  input arm and a complex impedance  $Z_2$  feedback arm is shown in Fig. 12.9. Its gain is  $Z_2/Z_1$ . If  $Z_1$  is a pure resistor R1 and  $Z_2$  is a pure re-

Figure 12.8 Where to locate break frequencies  $F_z$  and  $F_p$ . The farther apart  $F_z$  and  $F_p$  are spread, the greater the phase margin. But spreading them further apart reduces low-frequency gain, which reduces the degeneration of low-frequency line ripple. It also increases high gain, which permits high-frequency, thin noise spikes to come through at greater amplitude. If  $F_z$  were at  $F_{z2}$  instead of  $F_{z1}$ , gain at some low frequency  $F_1$  would be  $G_1$  instead  $G_2$ . And if  $F_p$  were at  $F_{p2}$  instead of  $F_{p1}$ , gain at some high frequency  $F_h$  would be  $G_1$  instead of  $G_2$ .

Figure 12.9 If inputs and feedback arms are various combinations of Rs and Cs, various gain-versus-frequency and phase-shift-versus-frequency curves are possible. By expressing impedances  $Z_1$  and  $Z_2$  in terms of an s operator (=jw), and performing a number of algebraic manipulations, a simplified expression for the gain arises. From this simplified gain expression (transfer function) the gain-versus-frequency and phase-shift-versus-frequency curves can be drawn at a glance.

sistor R2 as in Fig. 12.7a, gain is  $R_2/R_1$  and is independent of frequency. Phase shift between  $V_o$  and  $V_{\rm in}$  is 180°, as the input is to the inverting terminal.

Now impedances in  $Z_1$ ,  $Z_2$  are expressed in terms of the complex variable  $s = j(2\pi f) = jw$ . Thus the impedance of a capacitor C1 is then 1/sC1 and that of a resistor R1 and capacitor C1 in series is (R1 + 1/sC1).

The impedance of an arm consisting of a capacitor C2 in parallel with a series combination of R1 and C1 is then

$$Z = \frac{(r + 1/sC1)(1/sC2)}{r + 1/sC1 + 1/sC2}$$

(12.2)

Now the gain or transfer function of the operational error amplifier is written in terms of its  $Z_1$ ,  $Z_2$  impedances, which are expressed in terms of the complex variable s. Thus  $G(s) = Z_2(s)/Z_1(s)$ , and by algebraic manipulation, G(s) is broken down into a simplified numerator and denominator which are functions of s: G(s) = N(s)/D(s). The numerator and denominator, again by algebraic manipulation, are factored and N(s), G(s) are expressed in terms of these factors. Thus

$$G(s) = \frac{N(s)}{D(s)} = \frac{(1 + sz_1)(1 + sz_2)(1 + sz_3)}{sp_0(1 + sp_1)(1 + sp_2)(1 + sp_3)}$$

(12.3)

These z and p values are RC products and represent frequencies. These frequencies are obtained by setting the factors equal to zero. Thus

$$1 + sz_1 = 1 + s(j2\pi fz_1) = 1 + j2\pi fR1C1 = 0$$

or  $f_1 = 1/2\pi R1C1$

The frequencies corresponding to the z values are called zero frequencies, and those corresponding to the p values are called pole frequencies. There is always a factor in the denominator which has the "1" missing (note  $sp_0$  above). This represents an important pole frequency,  $F_{\rm po}=1/2\pi R_o C_o$ , which is called the pole at the origin.

From the location of the pole at the origin and the zero and pole frequencies, the gain-versus-frequency characteristic of the error amplifier can be drawn as discussed below.

## 12.5 Rules for Gain Slope Changes Due to Zero and Pole Frequencies

The zero and pole frequencies represent points where the erroramplifier gain slope changes.

A zero represents a +1 change in gain slope. Thus (Fig. 12.10a), if a zero appears at a point in frequency where the gain slope is zero, it turns the gain into a +1 slope. If it appears where the original gain slope is -1 (Fig. 12.10b), it turns the gain slope to zero. Or if there are two zeros at the same frequency (two factors in the numerator of Eq. 12.3 having the same RC product) where the original gain slope is -1,

Figure 12.10 (a) A zero appearing on a gain curve where the original slope was horizontal turns that gain slope to +1 or +20 dB/decade. (b) A zero appearing on a gain curve where the original slope was -1, terms that gain slope horizontal. (c) Two zeros at the same frequency appearing on a gain curve where the original slope was -1, turns that slope to +1. The first zero turns the -1 slope horizontal; the second zero at the same frequency turns the horizontal slope to +1. (d) A pole appearing on a gain curve where the original slope is horizontal turns that slope to -1 or 20 dB/decade. (e) Two poles at the same frequency appearing on a gain curve where the original slope is +1 turns that slope to -1. The first pole turns the original +1 slope horizontal; the second one at the same frequency turns the horizontal slope to -1 or -20 dB/decade.

the first zero turns the gain slope horizontal, and the second zero at the same frequency turns the gain into a +1 slope (Fig. 12.10c).

A pole represents a -1 change in gain slope. If it appears in frequency where the original gain slope is horizontal (slope is zero), it turns the gain into a -1 slope (Fig. 12.10*d*). Or if there are two poles at the same frequency at a point where the original gain slope is +1, the first pole turns the slope horizontal and the second at that same frequency turns the slope to -1 (Fig. 12.10*e*).

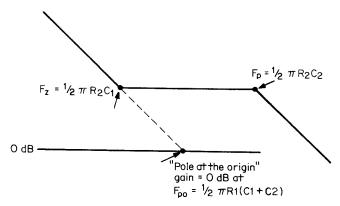

The pole at the origin, as does any pole, represents a gain slope of -1. It also indicates the frequency at which the gain is 1 or 0 dB. Thus, drawing the total gain curve for the error amplifier starts with the pole at the origin as follows. Go to 0 dB at the frequency of the pole at the origin  $F_{\rm po}=1/2\pi R_o C_o$ . At  $F_{\rm po}$ , draw a line backward in frequency with a slope of +1 (Fig. 12.11). Now if somewhere on this line, which has a -1 slope in the direction of higher frequency, the transfer function has a zero at a frequency  $F_z=1/2\pi R1C1$ , turn the gain slope horizontal at  $F_z$ . Extend the horizontal gain indefinitely. But if at some higher frequency there is a pole in the transfer function at a frequency  $F_p=1/2\pi R2C2$ , turn the horizontal slope into a -1 slope at  $F_p$  (Fig. 12.11).

The gain along the horizontal part of the transfer function is R2/R1

Figure 12.11 Drawing the gain curve of the error amplifier of Fig. 12.7b directly from its transfer function of Eq. 12.3.

and is made (in decibels) equal and opposite to the loss of the  $G_t$  curve (Fig. 12.6) at  $F_{\rm co}$ .

Thus an error-amplifier gain curve having a single pole at the origin, a single zero, and another single pole has the desired shape shown in Fig. 12.11. It is implemented by the circuit of Fig. 12.7b. It remains only to select the location of the zero and pole frequencies which yield the desired phase margin. This will be discussed below.

### 12.6 Derivation of Transfer Function of an Error Amplifier with Single Zero and Single Pole from Its Schematic

It has been shown above that if an error amplifier had a single zero, a single pole, and a pole at the origin, its gain-versus-frequency curve would be as in Fig. 12.11.

Now it will be demonstrated how the transfer function of an error amplifier is derived and that the circuit of Fig. 12.7b does truly have a single zero, a single pole, and a pole at the origin. Gain of the circuit in Fig. 12.7b is

$$\begin{split} G &= \frac{dV_o}{dV_i} \\ &= \frac{Z_2}{Z_1} \\ &= \frac{(R2 + 1/jwC1)(1/jwC2)}{R1(R2 + 1/jwC1 + 1/jwC2)} \end{split}$$

Now introduce the complex variable s = jw. Then

$$G = \frac{(R2 + 1/sC1)(1/sC2)}{R1(R2 + 1/sC1 + 1/sC2)}$$

And by algebraic manipulation

$$G = \frac{1 + sR2C1}{sR1(C1 + C2)(1 + sR2C1C2/C1 + C2)}$$

And since generally  $C2 \ll C1$

$$G = \frac{1 + sR2C1}{sR1(C1 + C2)(1 + R2C2)}$$

(12.4)

The error amplifier of Fig. 12.7b, having the transfer function of Eq. 12.4, is commonly referred to as a *Type 2 amplifier* in conformance with the designation introduced by Venable in his classic paper. A Type 2 error amplifier is used when the output filter capacitor has an ESR so that  $F_{co}$  lies on a -1 slope of the  $G_1$  curve (Fig. 12.6).

Examination of this transfer function for the circuit of Fig. 12.7b permits immediate drawing of its gain characteristic as follows (Fig. 12.11). Equation 12.4 shows that this circuit (Fig. 12.7b) has a pole at the origin at a frequency of  $F_{\rm po}=1/2\pi R1(C1+C2)$ . Thus, go to 0 dB at that frequency and draw a line backward toward lower frequency with a slope of +1.

From Eq. 12.4, the circuit has zero at a frequency of  $F_z = 1/2\pi R2C1$ . Go to that sloped line and turn it horizontal at  $F_z$ . Again from Eq. 12.4, the circuit has a pole at a frequency of  $F_p = 1/2\pi R2C2$ . Now go out along that horizontal line and turn it into a -1 slope at  $F_n$ .

Now that the transfer function of the Type 2 error amplifier can be drawn from its pole and zero frequencies, it remains to be able to locate them (choosing R1, R2, C1, C2) so as to achieve the desired phase margin. This is demonstrated below.

## 12.7 Calculation of Type 2 Error-Amplifier Phase Shift from Its Zero and Pole Locations

Adopting Venable's scheme, the ratio  $F_{\rm co}/F_z=K$  will be chosen equal to  $F_p/F_{\rm co}=K$ .

Now a zero, like an RC differentiator (Fig. 12.2b), causes a phase lead. A pole, like an RC integrator (Fig. 12.2a), causes a phase lag.

The phase lead at a frequency F due to a zero at a frequency  $F_z$  is

$$\Theta_{\rm ld} = \tan^{-1} \frac{F}{F_z}$$

But we are interested in the phase lead at  $F_{\rm co}$  due to a zero at a frequency  $F_z$ . This is

$$\Theta_{\rm ld} \left( \text{at } F_{\rm co} \right) = \tan^{-1} K \tag{12.5}$$

The phase lag at a frequency F due to a pole at a frequency  $F_p$  is

$$\Theta_{\text{lag}} = \tan^{-1} \frac{F}{F_p}$$

and we are interested in the lag at  $F_{co}$  due to the pole at  $F_p$ . This is

$$\Theta_{\text{lag}} \left( \text{at } F_{\text{co}} \right) = \tan^{-1} \frac{1}{K} \tag{12.6}$$

The total phase shift at  $F_{co}$  due to the lead of the zero at  $F_z$  and the lag due to the pole at  $F_p$  is the sum of Eqs. 12.5 and 12.6.

These shifts are in addition to the inherent low-frequency phase shift of the error amplifier with its pole at the origin. The error amplifier is an inverter and at low frequency causes a 180° phase shift.

At low frequencies, the pole at the origin causes a  $90^{\circ}$  phase shift. This is just another way of saying that at low frequencies, the circuit is just an integrator with resistor input and capacitor feedback. This is seen from Fig. 12.7b. At low frequencies, the impedance of C1 is much greater than R2. The feedback arm is thus only C1 and C2 in parallel.

Thus the inherent low-frequency phase lag is 180° because of the phase inversion plus 90° due to the pole at the origin or a total lag of 270°. Total phase lag, including the lead due to the zero and lag due to the pole, is then

$$\Theta_{\text{(total lag)}} = 270^{\circ} - \tan^{-1} K + \tan^{-1} \frac{1}{K}$$

(12.7)

Note that this is still a net phase lag as when K is a very large number (zero and pole frequencies very far apart), the lead due to the zero is a maximum of  $90^{\circ}$  and the lag due to the pole is  $0^{\circ}$ .

Total phase lag through the error amplifier, calculated from Eq. 12.7 is shown in Table 12.1.

## 12.8 Phase Shift through *LC* Filter Having ESR in its Output Capacitor

The total open-loop phase shift consists of that through the error amplifier plus that through the output LC filter. Figure 12.3b showed for  $R_o=20\sqrt{L_o/C_o}$  and no ESR in the filter capacitor, the lag through the filter itself is already 175° at  $1.2F_o$ .

This lag is modified significantly if the output capacitor has an ESR

TABLE 12.1 Phase Lag through a Type 2 Error Amplifier for Various Values of  $K(=F_{co}/F_z=F_p/F_{co})$

| K  | Lag (from Eq. 12.7) |

|----|---------------------|

| 2  | 233°                |

| 3  | 216°                |

| 4  | 208°                |

| 5  | 202°                |

| 6  | 198°                |

| 10 | 191°                |

as in Fig. 12.5b. In that figure, the gain slope breaks from a -2 to a -1 slope at the so-called ESR zero frequency of  $F_{\rm esr}=1/2\pi R_{\rm esr}C_o$ . Recall that at  $F_{\rm esr}$ , the impedance of  $C_o$  equals that of  $R_{\rm esr}$ . Beyond  $F_{\rm esr}$ , the impedance of  $C_o$  becomes smaller than  $R_{\rm esr}$  and the circuit becomes increasingly like an LR rather than an LC circuit. Moreover, an LR circuit can cause only a 90° phase lag as compared to the possible maximum of 180° for an LC circuit.

Thus the ESR zero creates a boost in phase over a possible maximum of 180°. Phase lag at a frequency F due to an ESR zero at  $F_{\rm esro}$  is

$$\Theta_{\rm lc} = 180^{\circ} - \tan^{-1} \frac{F}{F_{\rm esro}}$$

and since we are interested in the phase lag at  $F_{co}$  due to the zero at  $F_{esro}$

$$\Theta_{lc} = 180^{\circ} - \tan^{-1} \frac{F_{co}}{F_{coro}}$$

(12.8)

Phase lags through the LC filter (having an ESR zero) are shown in Table 12.2 for various values of  $F_{\rm co}/F_{\rm esro}$  (from Eq. 12.8).

TABLE 12.2 Phase Lag through an LC Filter at  $F_{co}$  Due to a Zero at  $F_{esro}$

| $F_{ m co}\!/F_{ m esro}$ | Phase lag | $F_{ m co}\!/\!F_{ m esro}$ | Phase lag      |

|---------------------------|-----------|-----------------------------|----------------|

| 0.25                      | 166°      | 2.5                         | 112°           |

| 0.50                      | 153°      | 3                           | 108°           |

| 0.75                      | 143°      | 4                           | 104°           |

| 1.0                       | 135°      | 5                           | 101°           |

| 1.2                       | 130°      | 6                           | 99.5°          |

| 1.4                       | 126°      | 7                           | 98.1°          |

| 1.6                       | 122°      | 8                           | 97.1°          |

| 1.8                       | 119°      | 9                           | 96.3°          |

| 2.0                       | 116°      | 10                          | $95.7^{\circ}$ |

448

Thus, by setting the error-amplifier gain in the horizontal part of its gain curve (Fig. 12.6) equal and opposite to the  $G_t$  (Fig. 12.6) loss at  $F_{\rm co}$ , the location of  $F_{\rm co}$  is fixed where it is desired. Since  $F_{\rm co}$  will in most cases be located on the -1 slope of the  $G_t$  curve, the total gain curve will come through  $F_{\rm co}$  at a -1 slope. From Tables 12.1 and 12.2, the proper value of K (locations of the zero and pole) is established to yield the desired phase margin.

# 12.9 Design Example—Stabilizing a Forward Converter Feedback Loop with a Type 2 Error Amplifier

The design example presented below demonstrates how much of the material discussed in all previous chapters is interrelated.

Stabilize the feedback loop for a forward converter with the following specifications:

| $V_o$                                | 5.0 V   |

|--------------------------------------|---------|

| $I_{o(\mathbf{nom})}$                | 10 A    |

| Minimum $I_o$                        | 1 A     |

| Switching frequency                  | 100 kHz |

| Minimum output ripple (peak to peak) | 50  mV  |

It is assumed that the filter output capacitor has an ESR and  $F_{\rm co}$  will occur on the -1 slope of the LC filter. This permits the use of a Type 2 error amplifier with the gain characteristics of Fig. 12.6. The circuit is shown in Fig. 12.12.

First  $L_o$ ,  $C_o$  will be calculated and the gain characteristic of the output filter will be drawn. From Eq. 2.47

$$L_o = \frac{3V_oT}{I_{on}}$$

$$= \frac{3 \times 5 \times 10^{-6}}{10}$$

$$= 15 \times 10^{-6} \text{ H}$$

and from Eq. 2.48

$$C_o = 65 \times 10^{-6} \frac{dI}{V_{\rm or}}$$

where dI is twice the minimum output current =  $2 \times 1 = 2$  A and  $V_{\rm or}$  is the output ripple voltage = 0.05 V. Then  $C_o = 65 \times 10^{-6} \times 2/0.05 = 2600$  microfarads.

Figure 12.12 Forward converter design example schematic stabilizing the feedback loop.

Corner frequency of the output LC filter, from Sec. 12.2.3, is

$$F_o = 1/2\pi \sqrt{L_o C_o}$$

=  $1/2\pi \sqrt{15 \times 10^{-6} \times 2600 \times 10^{-6}}$

= 806 Hz

Again from Sec. 12.2.3, the frequency of the ESR zero (frequency where the gain slope abruptly changes from a-2 to a-1 slope) is

$$F_{\rm esr} = 1/2\pi R_{\rm esr}C_o$$

= 1/2 $\pi$ (65 × 10 – 6) (assuming, as in Sec. 2.3.11.2, that over a large range of aluminum electrolytic capacitor magnitudes and voltage ratings, that  $R_{\rm esr}C_o$  is constant and equal to 65 × 10 – 6)

From Eq. 12.1, the modulator gain  $G_m$  is  $G_m = 0.5(V_{\rm sp}-1)/3$ , and when the duty cycle is 0.5, for  $V_o = 5\rm{V}$ ,  $V_{\rm sp} = 11~\rm{V}$  since  $V_o = (V_{\rm sp}-1)T_{\rm on}/T$ . Then  $G_m = 0.5(11-1)/3 = 1.67 = +4.5~\rm{dB}$ .

For the usual SG1524-type PWM chip, which can tolerate only 2.5 V at the reference input to the error amplifier, for  $V_o = 5$  V,  $R_{s1} = R_{s2}$ . Sampling network gain (loss) is then  $G_s = -6$  dB. Then  $G_m + G_s = +4.5 - 6.0 = -1.5$  dB.

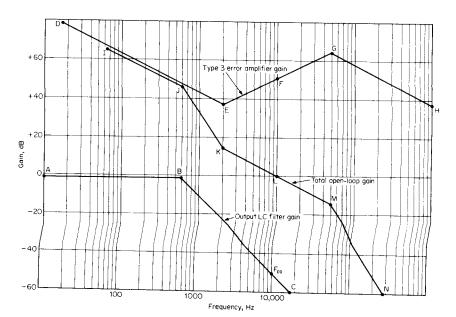

The open-loop gain curve of everything but the error amplifier is then  $G_t = G_{\rm lc} + G_m + G_s$  and is drawn in Fig. 12.13 as curve ABCD. From A to the corner frequency at 806 Hz (B) it has a value of  $G_m + G_s = -1.5$  dB. At B, it breaks into a -2 slope and continues at that slope up to the ESR zero at 2500 Hz (C). At point C, it breaks into a -1 slope.

Now crossover frequency is taken at one-fifth the switching frequency or 20 kHz. From the  $G_t$  curve, loss at 20 kHz is -40 dB (numerical loss of 1/100). Hence, to make 20 kHz the crossover frequency, the error-amplifier gain at that frequency is made +40 dB. Since the total open-loop gain of the error amplifier plus curve ABCD) must come through crossover at a -1 slope, the error-amplifier gain curve must have zero slope between points F and G in curve EFGH of Fig. 12.13 since ABCD already has a -1 slope at 20 kHz.

Figure 12.13 Design example stabilizing the feedback loop for Fig. 12.12.

This horizontal gain slope between points F and G is obtained as described above with a Type 2 error amplifier. The gain of the Type 2 error amplifier in the horizontal part of its slope is R2/R1. If R1 is arbitrarily taken as  $1000 \ \Omega$ ,  $R_2$  is  $100,000 \ \Omega$ .

Now a zero is located at  $F_z$  to increase low-frequency gain to degenerate 120-Hz line ripple and a pole is located at G to commence decreasing high-frequency gain so as to minimize thin noise spikes at the output. The zero and the pole will be located to give the desired phase margin.

Assume a 45° phase margin. Then total phase shift around the loop at 20 kHz is  $360-45=315^\circ$ . But the LC filter by itself causes a phase lag given by Eq. 12.7. From that equation, the lag for  $F_{\rm co}=20$  kHz and  $F_{\rm esro}=2500$  Hz is 97° (Table 12.2). Thus the error amplifier is permitted only 315 - 97 or 218°. Table 12.1 shows that for an error-amplifier lag of 218°, a K factor of slightly less than 3 would suffice.

To provide somewhat more insurance, assume a K factor of 4 which yields a phase lag of 208°. This, plus the 97° lag of the LC filter, yields a total lag of 305° and a phase margin of 360 – 305° or 55° at  $F_{\rm co}$ .

For a K factor of 4, the zero is at  $F_z = 20/4 = 5$  kHz. From Eq. 12.3,  $F_z = 1/2\pi R 2C1$ . For R2 determined above as 100K,  $C1 = 1/2\pi (100,000)(5000) = 318 \times 10^{-12}$ .

Again for the K factor of 4, the pole is at  $F_{\rm po}=20\times 4=80~\rm kHz$ . From Eq. 12.3,  $F_{\rm po}=1/2\pi R2C2$ . For R2=100K,  $F_{\rm po}=80~\rm kHz$ ,  $C2=1/2\pi(100,000)(80,000)=20\times 10^{-12}$ . This completes the design; the final gain curves are shown in Fig. 12.13. Curve IJKLMO is the total open-loop gain. It is the sum of curves ABCD and EFGH.

## 12.10 Type 3 Error Amplifier—When Used and Transfer Function

In Sec. 2.3.11.2, it was pointed out that the output ripple  $V_{\rm or}=R_o\,dI$  where  $R_o$  is the ESR of the filter output capacitor  $C_o$  and dI is twice the minimum DC current. Now most aluminum electrolytic capacitors do have an ESR. Study of many capacitor manufacturers' catalogs indicates that for such capacitors,  $R_oC_o$  is constant and equal to an average value of  $65\times10^{-6}$ .

Thus, using conventional aluminum electrolytic capacitors, the only way to reduce output ripple is to decrease  $R_o$ , which can be done only by increasing  $C_o$ . This, of course, increases size of the capacitor, which may be unacceptable.

Within the past few years, capacitor manufacturers have been able (at considerably greater cost) to produce aluminum electrolytic capacitors with essentially zero ESR for those applications where output ripple must be reduced to an absolute minimum.

plifier on the +1 slope of Fig. 12.14b will be set equal and opposite to the loss of the LC filter (Fig. 12.14a) at the desired  $F_{\rm co}$ .

From Table 12.3 and the transfer function of Eq. 12.10, the *RC* products which set the zero and pole frequencies at the desired points are determined as in the design example below.

# 12.13 Design Example—Stabilizing a Forward Converter Feedback Loop with a Type 3 Error Amplifier

Design the feedback loop for a forward converter having the following specifications:

| $V_o$                        | 5.0 V   |

|------------------------------|---------|

| $I_{o(\mathbf{nom})}$        | 10 A    |

| $I_{o(\min)}$                | 1.0 A   |

| Switching frequency          | 50  kHz |

| Output ripple (peak to peak) | < 20 mV |

Assume that the output capacitor is of the type advertised as having zero ESR.

First the output LC filter and its corner frequency are calculated. Refer to Fig. 12.15. From Eq. 2.47

$$L_o = \frac{3V_oT}{I_o}$$

=\frac{3 \times 5 \times 20 \times 10^{-6}}{10}

= 30 \times 10^{-6} H

Now it was assumed that the output capacitor had zero ESR so that ripple due to ESR should be zero. But there is a small capacitive ripple component (Sec. 1.2.7). This is usually very small, and hence a filter capacitor much smaller than the 2600- $\mu$ F capacitor used in the Type 2 error-amplifier design example can be used. But to be conservative, for this design assume the same 2600- $\mu$ F capacitor is used and that it has zero ESR. Then

$$F_o = 1/2\pi \sqrt{L_o C_o}$$

=  $1/2\pi \sqrt{30 \times 10^{-6} \times 2600 \times 10^{-6}}$

= 570 Hz

Assume, as for the Type 2 error-amplifier design example, that the modulator plus sampling resistor gain is -1.5 dB. The gain of the LC filter plus modulator plus sampling resistor gain is plotted in Fig. 12.16 as curve ABC. It is horizontal at a level of -1.5 dB up to the corner frequency of 570 Hz at point B. There it changes abruptly to a -2 slope and remains at that slope since the capacitor has no ESR.

Frequency  $F_{\rm co}$  is chosen as one-fifth the switching frequency or 50/5=10 kHz. On curve ABC of Fig. 12.16, loss at 10 kHz is -50 dB. Hence to force 10 kHz to be  $F_{\rm co}$ , the error-amplifier gain at 10 kHz is set at +50 dB (point F in Fig. 12.16). But the error amplifier must have a +1 slope at  $F_{\rm co}$  to yield a net -1 slope when added to the -2 slope of the LC filter. Thus, at point F draw a line of +1 slope. Extend this in the direction of lower frequencies to  $F_z$ —the frequency of the double zero. Extend it in the direction of higher frequencies to  $F_p$ , the frequency of the double pole. Then determine  $F_z$  and  $F_p$  from the K factor (Table 12.3) required to yield the desired phase margin.

Assume a phase margin of  $45^{\circ}$ . Then total phase lag of the error amplifier plus the LC filter is  $360-45=315^{\circ}$ . But the LC filter, not having an ESR zero, has a lag of  $180^{\circ}$ . This leaves a permissible lag of  $315-180=135^{\circ}$  for the error amplifier.

From Table 12.3, a K factor of 5 yields a lag of 136°, which is close

Figure 12.16 Gain curves—design example of Sec. 12.13. Output capacitor with zero ESR and Type 3 error amplifier.

enough. For  $F_{\rm co}=10$  kHz, K=5,  $F_z$  is 2 kHz and  $F_p$  is 50 kHz. Thus in Fig. 12.16, the +1 sloped line is extended down to 2 kHz at E, where it breaks upward to a +1 slope (-1 slope in direction of higher frequencies due to the pole at the origin). It is extended on a +1 slope from F to the double-pole frequency at 50 kHz. There it turns down to a -1 slope because of the two poles.

The curve *IJKLMN* is the total open-loop gain and is the sum of curves *ABC* and *DEFGH*. It is seen to have a gain of 0 dB at 10 kHz (the cross-over frequency  $F_{\rm co}$ ) and to come through  $F_{\rm co}$  at a -1 slope. The K factor of 5 yields the required 45° phase margin. Components must now be selected to yield the error-amplifier gain curve *DEFGH* in Fig. 12.16.

## 12.14 Component Selection to Yield Desired Type 3 Error-Amplifier Gain Curve

There are six components to be selected (R1, R2, R3, C1, C2, C3) and four equations for zero and pole frequencies (Eqs. 12.12 to 12.15).

Arbitrarily choose  $R1 = 1000 \Omega$ . Now the first zero (at 2000 Hz) occurs when  $R2 = X_{c1}$  and the impedance of the feedback arm at that frequency is mainly that of R2 itself. Thus gain at 2000 Hz is R2/R1. From Fig. 12.16, gain of the error amplifier at 2000 Hz is +37 dB or a numerical gain of 70.8. Then for R1 = 1K, R2 = 70.8K, from Eq. 12.12, we obtain

$$C1 = 1/2\pi R 2F_z$$

=  $1/2\pi (70,800)2000$

=  $0.011 \mu F$

from Eq. 12.14

$$C2 = 1/2\pi R 2F_p$$

=  $1/2\pi (70,800)(50,000)$

= 45 pF

from Eq. 12.13

$$C3 = 1/2\pi R 1 F_z$$

=  $1/2\pi (1000)(2000)$

=  $0.08 \,\mu\text{F}$

and finally from Eq. 12.15

$$R3 = 1/2\pi C3F_p$$

$$= 1/2\pi (0.08 \times 10^{-6})(50,000)$$

$$= 40 \Omega$$

### 12.15 Conditional Stability in Feedback Loops

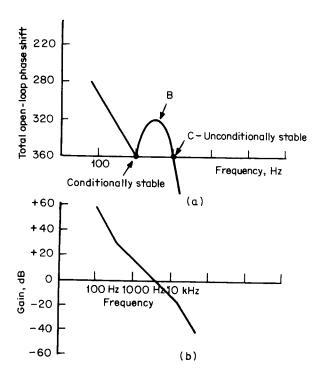

A feedback loop may be stable under normal operating conditions when it is up and running, but can be shocked into continuous oscillation at turnon or by a line input transient. This odd situation, called *conditional stability*, can be understood from Fig. 12.17a and 12.17b.

Figure 12.17aand 12.17b contains plots of total open-loop phase shift and total open-loop gain versus frequency, respectively. Conditional stability may arise if there are two frequencies (points A and C) at which the total open-loop phase shift reaches 360° as in Fig. 12.17a.

Recall that the criterion for oscillation is that at the frequency where the total open-loop gain is unity or 0 dB, the total open-loop

Figure 12.17 A loop may be conditionally stable if there are two frequencies where the total open-loop phase shift is  $360^{\circ}$ . Loop is conditionally stable at point A as a momentary drop in gain to 0 dB such as may occur at initial turnon may result in the conditions for oscillation, i.e.,  $360^{\circ}$  total open-loop phase shift and 0 dB gain. Once oscillation breaks out, it will continue. Circuit is unconditionally stable at B as momentary increases in gain are very unlikely.

phase shift is 360°. The loop is still stable if the total open-loop phase shift is 360° at a given frequency but the total open-loop gain at that frequency is greater than 1.

This may be difficult to grasp, as it would appear that if at some frequency the echo of a signal coming around the loop is exactly in phase with the original signal but larger in amplitude, it would grow larger in amplitude each time around the loop. It would thus build up to a level where the losses would be such to limit the oscillation to some high level and remain in oscillation. This does not occur, as can be demonstrated mathematically. But for the purposes herein, it will simply be accepted that oscillations do not occur if the total open-loop gain is greater than unity at the frequency where the total open-loop phase shift is 360°.

Thus in Fig. 12.17a, the loop is unconditionally stable at B as there the open-loop gain is unity but the open-loop phase shift is less than 360° by about 40°—i.e., there is a phase margin at point B. The loop is also stable at point C as there the open-loop phase shift is 360° but gain is less than unity—i.e., there is gain margin at point C. But at point C the loop is conditionally stable. Although the total open-loop phase shift is 360°, the gain is greater than unity (about +16 dB) and, as stated, the loop is stable for those conditions.

However, if under certain conditions—say, at initial turnon when the circuit has not yet come to equilibrium and open-loop gain momentarily drops 16 dB at the frequency of point A—the condition for oscillation exists. Gain is unity and phase shift is 360°. The circuit will break into oscillation and remain oscillatory. Point C is not a likely location for such conditional oscillation as it is not possible for gain to increase momentarily.

If conditional stability exists (most likely at initial turnon), it is likely to occur at the corner frequency of the output LC filter under conditions of light load. It is seen in Fig. 12.3a and 12.3b that a lightly loaded LC filter has a large resonant bump in gain and very fast phase shifts at its corner frequency. The large phase shifts can result in a total of 360° at the LC corner frequency. If total openloop gain (which is not easily predictable during the turnon transient may be unity or may momentarily be unity—the loop may break into oscillation.

It is rather difficult to calculate whether this may occur. The safest way to avoid this possibility is to provide a phase boost at the LC corner frequency by introducing a zero there to cancel some of the phase lag in the loop. This can be done easily by adding a capacitor in shunt with the upper resistor in the output voltage sampling network (Fig. 12.12).

## 12.16 Stabilizing a Discontinuous-Mode Flyback Converter

## 12.16.1 DC gain from error-amplifier output to output voltage node

The essential elements of the loop are shown in Fig. 12.18a. The first step in designing the feedback loop is to calculate its DC or low-frequency gain from the error-amplifier output to the output voltage node. Assume an efficiency of 80 percent. Then from Eq. 4.2a

$$P_o = \frac{0.8(1/2L)(I_p)^2}{T} = \frac{(V_o)^2}{R_o}$$

(12.16)

But  $I_p = V_{dc}\overline{T_{on}}L_p$ ; then

$$P_o = \frac{0.8L_p(V_{dc}\overline{T_{on}}/L_p)^2}{2T} = \frac{(V_o)^2}{R_o}$$

(12.17)

Figure 12.18 Discontinuous-mode flyback feedback loop.

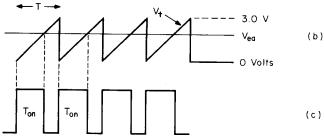

Referring to Fig. 12.18b, it is seen that the PWM compares the output of the error amplifier  $V_{\rm ea}$  to a 0- to 3-V triangle. It generates a rectangular pulse whose width  $(T_{\rm on};$  Fig. 12.18c) is equal to the time from the start of the triangle to its intersection with DC voltage level  $V_{\rm ea}$ . This  $T_{\rm on}$  will be the on time of power transistor Q1. It is seen in Fig. 12.18b that  $V_{\rm ea}/3 = T_{\rm on}/T$  or  $T_{\rm on} = V_{\rm ea}T/3$ . Putting this into Eq. 12.16, we have

$$P_{o} = \frac{0.8L_{p}(V_{dc}/L_{p})^{2}(V_{ea}T/3)^{2}}{2T} = \frac{(V_{o})^{2}}{R_{o}}$$

$$V_{o} = \frac{V_{dc}V_{ea}}{3}\sqrt{\frac{0.4R_{o}T}{L_{p}}}$$

(12.18)

or

and the DC or low-frequency gain from the error-amplifier output to the output node is

$$\frac{\Delta V_o}{\Delta V_{\rm ea}} = \frac{V_{\rm dc}}{3} \sqrt{\frac{0.4 R_o T}{L_p}}$$

(12.19)

# 12.16.2 Discontinuous-mode flyback transfer function or AC voltage gain from error-amplifier output to output voltage node

Now assume a small sinusoidal signal of frequency  $f_n$  inserted in series at the error-amplifier output point. This will cause a sinusoidal modulation in amplitude of the triangular current pulses (of peak amplitude  $I_p$ ) in the T1 primary. Consequently, there is a sinusoidal amplitude modulation in the triangular secondary current pulses (whose instantaneous amplitude is  $I_p N_p/N_s$ ).

The average value of these triangular secondary current pulses then is modulated at the same sinusoidal frequency  $f_n$ . There is thus a sinusoidal current of frequency  $f_n$  flowing into the top of the paralleled combination of  $R_o$  and  $C_o$ .

But this alternating current flows into the Thevenin equivalent of  $R_o$  and  $C_o$  in series. It is thus seen that the output voltage across  $C_o$  falls off in amplitude at the rate of -20 dB/decade or at a -1 slope starting from the frequency of  $F_p = 1/2\pi R_o C_o$ .

This is simply another way of saying that the transfer function from the error-amplifier output to the output voltage node has a pole at

$$F_p = 1/2\pi R_o C_o \tag{12.20}$$

and DC gain below the pole frequency is given by Eq. 12.19.

This is in contrast to topologies which have an LC output filter. In such topologies, a sinusoidal voltage inserted at the error-amplifier output node results in a sinusoidal voltage at the input to the LC filter. That voltage, coming through the LC filter, falls off in amplitude at -40 dB/decade rate or -2 slope. Or to use the common jargon expression, the LC filter has a two-pole rolloff at the output node.

This -1 slope or *single-pole rolloff* of the flyback topology output circuit, of course, changes the error-amplifier transfer function required to stabilize the feedback loop. The flyback converter output filter capacitor, in most cases, also has an ESR zero at a frequency of

$$F_z = 1/2\pi R_c C_o \tag{12.21}$$

Now, a complete analysis of the stabilization problem should consider maximum and minimum values of both DC input voltage and of  $R_o$ . Equation 12.19 shows DC gain as proportional to  $V_{\rm dc}$  and to the square root of  $R_o$ . Further, the output circuit pole frequency is inversely proportional to  $R_o$ .

Thus in the following graphical analysis, all four combinations of  $V_{\rm dc}$  and  $R_o$  should be considered as the output circuit transfer function may vary significantly with them.

For one output circuit transfer function (one set of line and load conditions), the error-amplifier transfer function is designed to establish  $F_{\rm co}$  at a desired frequency and to have the total gain curve come through  $F_{\rm co}$  at a -1 slope. Care must be taken, then, that at another output circuit transfer function (different load and line conditions), the total gain curve does not come through  $F_{\rm co}$  at a -2 slope and possibly cause oscillation.

For this example, consider that  $V_{\rm dc}$  variations are small enough to be neglected. Thus calculate DC gain from Eq. 12.19 and output circuit pole frequency from Eq. 12.20. Assume  $R_{o({\rm max})} = 10R_{o({\rm min})}$ .

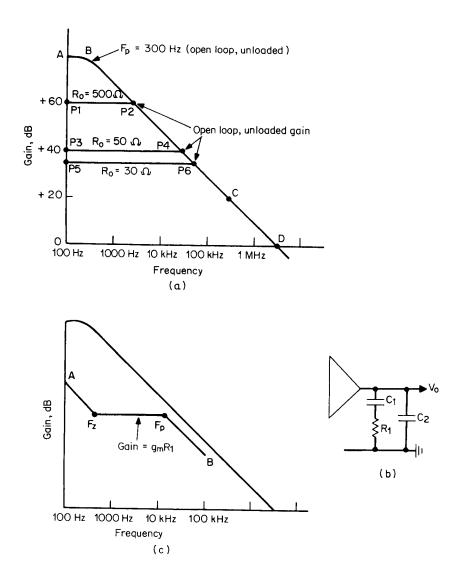

Now in Fig. 12.19, curve ABCD is the output circuit transfer function for  $R_{o(\max)}$ . It has a gain given by Eq. 12.19 from A to B. At B, it breaks into a -1 slope because of the output pole given by Eq. 12.20. At C, its slope turns horizontal because of the ESR zero of the output capacitor. Frequency at point C is given by Eq. 12.21, whereas in Sec. 1.3.7,  $R_cC_o$  is  $65 \times 10^{-6}$  for an aluminum electrolytic capacitor over a large range of voltage and capacitance ratings.

Also in Fig. 12.19, curve EFGH is the output circuit transfer function for  $R_{o(\min)} = R_{o(\max)}/10$ . Its pole frequency is 10 times that for  $R_o$  as  $F_p$  is inversely proportional to  $R_o$ . DC gain at F is 10 dB below that for  $R_{o(\max)}$  as gain is proportional to the square root of  $R_o$  (20  $\log \sqrt{10} = 10dB$ ).

Figure 12.19 Gain curves for stabilizing the feedback loop or the discontinuous-mode flyback of design example in Sec. 12.18.

Thus the output circuit transfer function for  $R_{o(\min)}$  is drawn as follows. Go to point F, which is at a frequency 10 times that of point B and 10 dB below point B. Draw a horizontal line back toward DC for the low-frequency gain (line FE). At F, draw a line of -1 slope (-20 dB/decade) and continue it to the ESR zero frequency at G. At G, draw a line of horizontal slope out toward higher frequency.

From output circuit transfer functions *ABCD* and *EFGH* of Fig. 12.19, the error-amplifier gain or transfer function curve is drawn as described below (Sec. 12.17).

### 12.17 Error-Amplifier Transfer Function for Discontinuous-Mode Flyback

In Fig. 12.19, for  $R_{o(\min)}$ , on curve *EFGH*,  $F_{co}$  will be established at one-fifth the switching frequency (point P1) as stated in Sec. 12.3. Most often,  $F_{co}$  will occur on the horizontal slope of the output circuit transfer function.

To force  $F_{\rm co}$  to be at the desired point, the error amplifier will be designed to have a gain at  $F_{\rm co}$  (point P2) equal and opposite to the output circuit loss at point P1. Since the slope of EFGH at  $F_{\rm co}$  is horizon-

tal, the error-amplifier gain slope must be -1 (in the direction of higher frequencies) at point P2.

Thus, go to point P2 and draw a line backward with a slope of +1 in the direction of lower frequencies. Extend it to a frequency (point P3) somewhat lower than the frequency at C. For at  $R_{o(\max)}$ , the output circuit transfer function will be ABCD. Since the total gain curve must come through the new  $F_{co}$  for  $R_{o(\max)}$  at a -1 slope, this new  $F_{co}$  will occur at the frequency where the loss along the horizontal line CD is equal and opposite (at point P4) to the gain of the error amplifier on its -1 slope.

The exact frequency for point P3 is not critical. It must be lower than the frequency at C to ensure that for the absolutely maximum  $R_o$ , where point C will be depressed to its greatest loss, this maximum loss can be matched by the equal and opposite gain of the error amplifier somewhere along its -1 slope.

Thus a pole is located at the frequency  $F_p$  corresponding to the pole at point P3. A Type 2 error amplifier is used. The input resistor R1 (Fig. 12.18a) is arbitrarily selected sufficiently high so as not to load down the sampling resistor network.

Gain along the horizontal arm (points P3-P5) is read from the graph and made equal to R2/R1 (Fig. 12.18a). This fixes resistor R2. From the pole frequency  $F_p$  and R2, the value of C2 in Fig. 12.18a (=  $1/2\pi F_p R2$ ) is fixed.

Now the gain is extended along the horizontal line P3-P5 and a zero is introduced at point P5 to increase low-frequency gain and offer a phase boost. Frequency of the zero  $F_z$  at point P5 is not critical; it should be about a decade below  $F_p$ . To locate the zero at  $F_z$ , C1 (Fig. 12.18a) is chosen as  $C_1 = 1/2\pi R2F_z$ .

The design example of the following section will clarify all the above.

## 12.18 Design Example—Stabilizing a Discontinuous-Mode Flyback Converter

Stabilize the feedback loop of the design example in Sec. 4.3.2.7. It is assumed that the output capacitor has an ESR and so a Type 2 error amplifier will be used. The circuit is shown in Fig. 12.18a. Recall its specifications:

| $V_o$                 | 5.0 V |

|-----------------------|-------|

| $I_{o(\mathbf{nom})}$ | 10 A  |

| $I_{o(\min)}$         | 1.0 A |

| $V_{ m dc(max)}$      | 60 V  |

466

| $V_{ m dc(min)}$                | 38 V    |

|---------------------------------|---------|

| $V_{ m dc(ay)}$                 | 49 V    |

| Switching frequency             | 50 kHz  |

| L. (calculated in Sec. 4.3.2.7) | 56.6 µH |

Recall from Sec. 4.3.2.7 that  $C_o$  was calculated as 2000  $\mu$ F. But it was pointed out there that at the instant of turnoff, the peak secondary current of 66 A would cause a thin spike of  $66 \times 0.03 = 2$  V across the anticipated ESR of 0.03 V for a 2000- $\mu$ F capacitor. It was noted that either this thin spike could be integrated away with a small LC circuit or  $C_o$  could be increased to lower its ESR.

Here, both will be done. Capacitance  $C_o$  will be increased to 5000  $\mu F$  to decrease  $R_c$  to (2/5)0.03 or  $0.012~\Omega$  (since  $R_c$  is inversely proportional to  $C_o$ ). The initial spike at Q1 turnoff is then  $66\times0.012$  or 0.79 V peak. This can easily be integrated down to an acceptable level with a small LC which will be outside the feedback loop.

Now the output circuit gain curve can be drawn—first for  $R_{o(\min)}$  of  $5/10 = 0.5 \Omega$ . The DC gain from Eq. 12.19 is

$$G = \frac{V_{dc}}{3} \sqrt{\frac{0.4R_o T}{L_p}}$$

$$= \frac{49}{3} \sqrt{\frac{0.4 \times 0.5 \times 20 \times 10^{-6}}{56.6 \times 10^{-6}}}$$

$$= 4.3$$

$$= +12.8 \text{ dB}$$

Pole frequency, from Eq. 12.20, is

$$F_p = 1/2\pi R_o C_o$$

= 1/2\pi 0.5 \times 5000 \times 10^{-6}

= 63.7 Hz

and ESR zero frequency, from Eq. 12.20, is

$$F_{\rm esro} = 1/2\pi R_o C_o$$

= 1/2\pi 65 \times 10^{-6}

= 2500 Hz

The output circuit gain curve for  $R_o=0.5~\Omega$  is then drawn as *EFGH* in Fig. 12.19. It is horizontal at a level of +12.8 dB up to  $F_p=63.7~\mathrm{Hz}$ . There it breaks to a -1 slope down to the ESR zero at 2500 Hz. The error-amplifier gain curve can now be drawn.

Then choose  $F_{co}$  as one-fifth the switching frequency or as 50/5 = 10

kHz. On *EFGH*, the loss is -19 dB at 10 kHz. Hence make the erroramplifier gain +19 dB at 10 kHz. Go to 10 kHz and +19 dB (point P2) and draw a line backward with a slope of +1 (+20 dB/decade) in the direction of lower frequency. Now extend that line to a frequency somewhat lower than  $F_{\rm esro}$ —say, to point P3 at 1 kHz, +39 dB. At point P3, draw a horizontal line back to—say—300 Hz at point P5 (where a zero will be located).

The location of the zero is not critical. In Sec. 12.17, it was suggested the zero at point P5 should be one decade below point P3. Some designers actually omit the zero at point P5.<sup>5</sup> But here it is added to gain some phase boost. Thus, for a zero at point P5, at that point turn the gain slope upward to a +1 slope (again in the direction of lower frequency).

Now verify that for  $R_{o(\max)}$  of 5  $\Omega$ , the total gain curve (output circuit plus error-amplifier transfer function) comes through  $F_{co}$  at a -1 slope.

For  $R_o=5~\Omega$ , Eq. 12.19 gives a DC gain of 13.8 or +23 dB. And Eq. 12.20 gives the pole frequency as 6.4 Hz. The frequency of the ESR zero remains at 2500 Hz. Thus the output circuit transfer function for  $R_o=5~\Omega$  is ABCD.

The new  $F_{\rm co}$  is then the frequency where the gain of the error amplifier on P6–P5–P3–P7 equals the loss on ABCD. This is seen to be at point P4 (3200 Hz), where the output filter loss is -29 dB and the error-amplifier gain is +29 dB. The sum of the error-amplifier gain curve and ABCD (equal to total gain curve) is seen to have a -1 slope as it passes through  $F_{\rm co}$ .

It should be noted, however, that if  $R_o$  were somewhat larger, the curve ABCD would be depressed to a lower value along its entire length. Then the point at which the previously fixed error-amplifier gain curve is equal and opposite to the output filter loss curve would occur on the -1 slope of each curve.

The total gain curve would then come through the new  $F_{\rm co}$  at a -2 slope and oscillations could occur. Thus, as a general rule, discontinuous-mode flybacks should be tested carefully for stability at minimum load current (maximum  $R_o$ ).

The error-amplifier transfer function of P6--P5--P3--P7 is implemented as follows. In Fig. 12.18a, arbitrarily choose  $R_1 = 1000~\Omega$ . Gain at point P3 is seen in Fig. 12.19 to be +38 dB or numerical gain of 79. Thus  $R_2/R_1 = 79$  or  $R_2 = 79,000~\Omega$ . For the pole at point P3 at 1 kHz,  $C_2 = 1/(2\pi F_p R_2)$  or  $C_2 = 2000~\text{pF}$ . For the error-amplifier zero at 300 Hz,  $C_1 = 1/(2\pi F_z R_2) = 6700~\text{pF}$ .

Because of the single-pole rolloff characteristic of the output circuit, its absolute maximum phase lag is 90°. But because of the ESR zero, it is much less and there rarely is a phase-margin problem in the discontinuous-mode flyback.

Thus consider the situation for  $R_o=0.5~\Omega$ . Lag at  $F_{\rm co}$  (10 kHz) due to the pole at 64 Hz and the ESR zero at 2500 Hz is

Output circuit lag =

$$\tan^{1}\left(\frac{10,000}{64}\right) - \tan^{1}\left(\frac{10,000}{25,000}\right)$$

=  $89.6 - 76.0$

=  $13.6^{\circ}$

and the error-amplifier lag at  $10,000~\rm{Hz}$  due to the zero at  $300~\rm{Hz}$  and the pole at  $1000~\rm{Hz}$  (see Fig. 12.20, curve P6-P5-P3-P7) is

$$270 - \tan^{-1}\left(\frac{10,000}{300}\right) + \tan^{-1}\left(\frac{10,000}{1000}\right) = 270 - 88 + 84 = 266^{\circ}$$

Total phase lag at 10,000 is then 13.6 + 266 = 280°. This yields a phase margin at  $F_{\rm co}$  of 360 - 280 = 80°.

### 12.19 Transconductance Error Amplifiers

Many of the commonly used PWM chips (1524, 1525, 1526 family) have transconductance error amplifiers. Transconductance  $g_m$  is the change in output current per unit change in input voltage. Thus

$$g_m = \frac{dI_o}{dV_{\rm in}}$$

Then for shunt impedance  $Z_o$  at the output node to ground

$$dV_{o} = dI_{o}Z_{o} = g_{m} dV_{in}Z_{o}$$

or gain G is

$$G = \frac{dV_o}{dV_{in}} = g_m Z_o$$

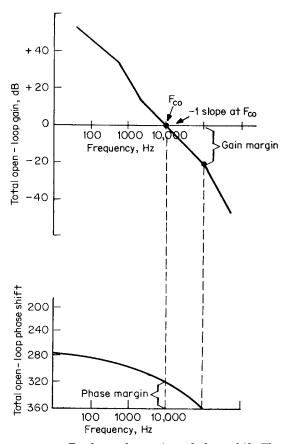

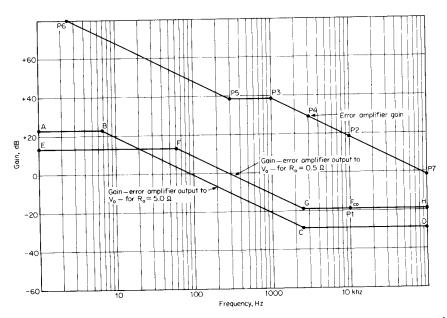

The unloaded, open-loop gain characteristic of the 1524, 1525-family amplifiers have a DC gain of nominally +80 dB, have a pole at 300 Hz, and thereafter fall at a -1 or -20 dB/decade slope. This is seen as curve ABCD in Fig. 12.20a.

A pure resistance  $R_o$  shunted from output node to ground yields a gain curve which is constant and equal to  $g_mR_o$  from DC up to the frequency where it intersects the curve ABCD in Fig. 12.20a. For the 1524, 1525 family,  $g_m$  is nominally 2 mA/V. Thus gains for  $R_o = 500K$ , 50K, and 30K are respectively 1000, 100, and 60 and are shown as curves P1-P2, P3-P4, and P5-P6 in Fig. 12.20a.

In most cases, Type 2 error-amplifier gain characteristics are re-

Figure 12.20 (a) Open-loop unloaded gain curve for PWM chip 1524, 1525 error amplifiers in ABCD. When loaded with indicated shunt resistors to ground, gain is constant at  $G = g_m R_o$ . (Courtesy Silicon General). (b) A Type 2 error-amplifier gain curve with shunt network to ground. (c) Gain with circuit of Fig. 12.20b is  $A-F_z-F_p-B$ :  $F_z=1/2\pi R1C1$ ;  $F_p=1/2\pi R1C2$ .

quired. This is easily obtained with the network shown in Fig. 12.20*b* shunted to ground.

At low frequencies,  $X_{C1}$  is much greater than R1 and effectively C1 and C2 are in parallel with the internal 100 pF to ground which caused the open-loop 300-Hz pole. This shifts the 300-Hz pole to a

lower frequency, and after that lower frequency, gain resumes falling at a -1 slope. At a frequency  $F_z$  ( =  $1/2\pi R1C1$ ), where  $X_{C1}=R_1$ , there is a zero and gain slope turns horizontal at a magnitude  $g_mR1$ . Further on in frequency at  $F_p=1/2\pi R1C2$  where  $X_{C2}=R1$ , the pole turns the gain slope to -1.

The gain curve with the circuit configuration of Fig. 12.20b is shown in Fig. 12.20c.

Most frequently, in the 1524, 1525 family of PWM chips the erroramplifier gain curves are shaped in the above-mentioned fashion with the network of Fig. 12.20b shunted to ground rather than being used in the conventional operational-amplifier mode.

Whether a network as Fig. 12.20b is shunted to ground or returned around to the inverting input terminal as in a conventional operational amplifier, there is a restriction on the magnitude of R1 arising from the following. The internal error amplifiers in the abovementioned chips cannot emit or absorb more than 100  $\mu$ A. With a 3-V triangle at the PWM comparator, the error-amplifier output may have to move the 3 V from the bottom to the top of the triangle for sudden line or load changes. Thus for R1 less than 30,000  $\Omega$ , this 3-V fast swing would demand more than the available 100  $\mu$ A. Response time to fast load or line changes would then be sluggish.

Because of this 100-µA limit on output current, many designers prefer not to use the error amplifier internal to the PWM chip. Since the chip's output node is brought out to one of the output pins, some prefer to use a better external error amplifier and connect it to the chip's error-amplifier output node at the appropriate output pin.

However, it may be essential from a cost viewpoint to use the chip's internal error amplifier. Calculation of the output filter may show that its loss at  $F_{\rm co}$  is so low that to match the error-amplifier gain to it,  $R_1$  must be less than 30,000  $\Omega$ . If this situation arises,  $R_1$  can be increased to 30,000  $\Omega$  to match an artificially increased output filter loss at  $F_{\rm co}$ . This increased output filter loss at  $F_{\rm co}$  can easily be achieved by shifting its pole frequency to a lower value by increasing the output filter's inductance or capacitance.

#### References

- D. Venable, "The K Factor: A New Mathematical Tool for Stability Analysis and Synthesis," Proceedings Powercon 10, 1983.

- A. Pressman, Switching and Linear Power Supply, Power Converter Design, pp. 331–332, Switchtronix Press, Waban, Mass., 1977.

- K. Billings, Switchmode Power Supply Handbook, Chap. 8, McGraw-Hill, New York, 1989.

- G. Chryssis, High Frequency Switching Power Supplies, 2d ed., Chap. 9, McGraw-Hill, New York, 1989.

- Unitrode Corp., Power Supply Design Seminar Handbook, Apps. B, C, Watertown, Mass., 1988.