# Control System Design and Small-Signal Analysis of a Phase-Shift-Controlled Series-Resonant Inverter for Induction Heating

L. Grajales and F. C. Lee Virginia Polytechnic Institute and State University

Abstract - A phase-shift-controlled series-resonant inverter operating at zero-voltage-switching (ZVS) is used as the power supply for an induction heating system. This system has two control loops: the phase-shift control loop regulates the output power, and the frequency control loop ensures ZVS for all load conditions. The design and implementation of these control loops are explained. The complete closed-loop small-signal model is obtained using the extended describing function method. The model predictions are compared with experimental data measured from a lab prototype.

#### I. INTRODUCTION

A phase-shift controlled series-resonant inverter (PSC-SRI) operating at 500 kHz, 10 kW is used as the power supply for an induction heating system. A PSC-SRI has been suggested for induction heating applications because of its hardware simplicity [Grajales, Nakaoka]. The PSC-SRI does not require a pre-regulator and the resonant inductor is composed of the coil, work-piece and transformer leakage inductance. In addition the PSC-SRI operates over a narrow frequency range because the switching frequency varies only to maintain zero turn-on losses, also called zero-voltage switching (ZVS). The proposed PSC-SRI has two control loops: the phase-shift control loop regulates the output power, and the frequency control loop ensures ZVS. The phase-shift is regulated with a PWM duty-cycle control strategy. The frequency is regulated using an adaptation of the current charge control method.

Most induction heating applications require heating the work-piece at a given temperature for a given time. During the heating process the load resistance and inductance vary, especially when the work-piece reaches the Curie temperature. Therefore, since the load inductance is part of the resonant inductance, the resonant frequency of the system will vary. The frequency control strategy for the PSC-SRI keeps track of the resonant frequency to maintain ZVS while switching as close as possible to resonance to minimize circulating energy. Because of the high risk of MOSFET damage when ZVS is not achieved, it is important to know the response time and the reliability of the frequency control loop. At the same time, depending on the application, there might be a demand for an accurate power control for a given temperature profile. Hence, the bandwidth, phase margin, and gain margin of the frequency and power control loops should be properly designed to guarantee a robust system. The smallsignal model is a useful tool to analyze the performance of the control loops. It helps corroborate hardware loop measurements, and it allows experimenting with several compensation schemes before they are implemented.

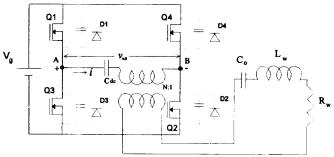

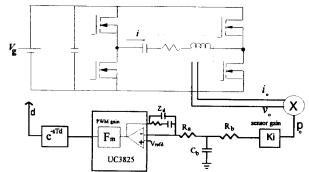

Fig. 1 PSC-SRI power stage circuit

This paper will describe the PSC-SRI operation. It will use the extended describing function method for modeling the inverter power-stage. The closed-loop small-signal model will be derived for both the phase-shift and the frequency control loops. Loop-gain transfer functions will be obtained and compared with experimental data measured from a laboratory prototype.

# II. PHASE-SHIFT CONTROLLED SERIES-RESONANT INVERTER PROPERTIES

The power stage of the circuit, a full-bridge series-resonant inverter, is shown in Fig. 1.  $L_W$  and  $R_W$  are the coil plus work-piece equivalent inductance and resistance, respectively.  $C_O$  is the resonant capacitance, and  $C_{CO}$  is the dc current blocking capacitor. Also,  $f_s$  is the switching frequency, and  $f_O$  is the resonant frequency, where  $f_O = \frac{1}{2\pi\sqrt{L_W C_O}}$ .

Power MOSFETs are selected as the switching devices for this application because of the high switching frequency requirement. The four transistors, Q1-Q4, are operated with a 50% duty cycle. The switches in each leg of the bridge are turned on and off 180 degrees out of phase. When operating above resonance, the load current, i, lags the quasi-square wave voltage,  $v_{AB}$ , as shown in Fig. 2(a). Body diodes conduct current after the MOSFET's output capacitance is discharged. During this diode conduction period, the MOSFETs can be turned on at zero voltage [Sabaté]. Zero voltage switching (ZVS) must be ensured at all times to prevent possible device damage. Output power of the inverter is regulated by varying the phase-shift between switches Q1 and Q2. The resulting voltage across the tank is a quasisquare wave with a duty ratio d. If the switching frequency is kept constant and close to resonance, ZVS will be lost for decreasing values of d because the load current becomes positive before Q2 turns on. To prevent loosing ZVS, the controller increases the switching frequency to allow for more

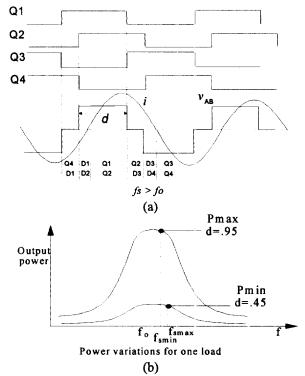

Fig. 2 (a) PSC-SRI Power stage circuit waveforms (b) Power regulation for one load condition.

negative load current before Q2 turns on, ensuring a full discharge of the MOSFET's output capacitance.

Figure 2(b) shows an example of the control strategy for a particular load condition. This example shows that when d = 0.95, maximum power is obtained and that the switching frequency is very close to resonance (ZVS is maintained), whereas when low output power is desired for the same load condition, d = 0.45. The switching frequency that ensures ZVS is farther from resonance when d = 0.45 than when d = 0.95.

## III. SMALL-SIGNAL MODEL

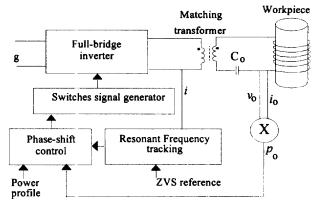

Figure 3 shows the system's diagram with the two control loops: frequency and phase-shift. The slow loop is the phaseshift control loop, which senses the output power, Po, and varies the phase-shift to maintain P<sub>0</sub> at the desired value.

The fast loop is the frequency control loop, which senses the tank current and determines how far above resonance it should operate to maintain ZVS. In this section, the smallsignal model will be obtained, first for the power stage, and subsequently for each of the control loops. The modeling method used is known as "extended describing function method".

#### A. Power Stage Small Signal Model

In this section, a summarized procedure of how to obtain the small-signal model of the power stage of the PSC-SRI will be given. For further extended describing function modeling techniques and other circuit models see [Yang, 1991].

Fig. 3 PSC-SRI system diagram.

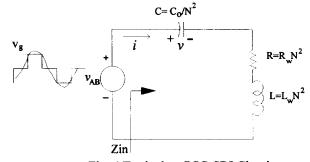

The PSC-SRI power stage circuit can be represented by the equivalent circuit shown in Fig. 4.

First, Kirchhoff's voltage law is applied to the circuit in Fig. 4 to give

$$L\frac{di}{dt} + v + iR = v_{AB} , \qquad (1)$$

$$C\frac{dv}{dt} = i. (2)$$

The output variable is the average power at the resistance:

$$P_o = \frac{Ri^2}{2} \ . \tag{3}$$

The harmonic approximation is used for the inductor current and capacitor voltage so that

$$i(t) \approx i_c(t) \cdot \cos(\omega_s t) + i_s(t) \cdot \sin(\omega_s t)$$

, (4)

$$v(t) \approx v_c(t) \cdot \cos(\omega_s t) + v_s(t) \cdot \sin(\omega_s t)$$

, (5)

and the extended describing function is applied to the input voltage,

$$v_{AB} = \frac{4}{\pi} v_g \sin(\frac{\pi}{2} d) \sin(\omega t) = v_e \sin(\omega t).$$

(6)

Fig. 4 Equivalent PSC-SRI Circuit

Substituting (4)-(6) into (1)-(2), and using the harmonic balance procedure, we can decompose (1)-(2) into four equations by grouping separately the sine terms and the cosine terms to obtain:

sine terms:

$$\frac{dv_s}{dt} = \frac{i_s}{C} + \omega_s v_c, \qquad (7)$$

$$\frac{di_s}{dt} = \frac{-v_s - i_s R + v_e}{I} + \omega_s i_c, \qquad (8)$$

$$\frac{di_s}{dt} = \frac{-v_s - i_s R + v_e}{I} + \omega_s i_c , \qquad (8)$$

form of

$$\frac{dv_c}{dt} = \frac{i_c}{C} - \omega_s v_s \,, \tag{9}$$

$$\frac{di_c}{dt} = \frac{-v_c - i_c R}{L} - \omega_s i_s. \tag{10}$$

Equations (7)-(10) can now be used to solve for the operating point by letting all the derivatives be zero. Their solutions are given in appendix A.

The linearized model is found by perturbing the largesignal system given by (7)-(10) around the operating point [Vg, D, Ws, Q], where Vg is the input voltage, Ws is the switching frequency, D is the duty ratio, and Q is the load factor defined as  $Q = \frac{W_s L}{R}$ . The perturbed variables are the inputs, the state variables, and the output. Each will have the

$$h(t) = H + \hat{h}(t), \qquad (11)$$

where H is at the operating point, and  $\hat{h}(t)$  is a small amplitude perturbation. Hence, these perturbed variables are replaced in (7)-(10), and then, by finding the Taylor expansion and considering only the first partial derivatives. we obtain the linearized model [Kassakian]. For example, (8) can be expressed as:

$$\frac{di_s}{dt} = f(v_s, v_c, i_s, i_c, d, v_g, w_s); \tag{12}$$

hence, its linearized equation is

$$\frac{d\hat{i}_s}{dt} \approx \frac{\partial f}{\partial v_s} \hat{v}_s + \frac{\partial f}{\partial v_c} \hat{v}_c + \frac{\partial f}{\partial i_s} \hat{i}_s + \frac{\partial f}{\partial i_c} \hat{i}_c + \frac{\partial f}{\partial \omega_s} \hat{\omega}_s + \frac{\partial f}{\partial v_g} \hat{v}_g + \frac{\partial f}{\partial d} \hat{d} , \quad (13)$$

where each  $\frac{\partial f}{\partial x}$  is evaluated at the operating points.

Equation (13) is acceptable as long as the perturbation is small-signal, since higher order terms can be neglected. This linearization procedure is done to (7)-(10) to obtain the complete linearized model

$$\frac{d\hat{v}_s}{dt} = \frac{i_s}{C} + W_s \hat{v}_c + V_c \hat{\omega}_s , \qquad (14)$$

$$\frac{d\hat{i}_{s}}{dt} = \frac{\hat{v}_{s}}{L} - \frac{R}{L} \hat{i}_{s} + W_{s} \hat{i}_{c} + I_{c} \hat{\omega}_{s} + \frac{2V_{g}}{L} cos(\frac{\pi}{2}D) \hat{d} + \frac{4}{\pi L} sin(\frac{\pi}{2}D) \hat{v}_{g}, \quad (15)$$

$$\frac{d\hat{\mathbf{v}}_c}{dt} = \frac{\hat{i}_c}{C} - W_s \hat{\mathbf{v}}_s - V_s \hat{\boldsymbol{\omega}}_s , \qquad (16)$$

$$\frac{d\hat{i}_c}{dt} = -\frac{\hat{v}_c}{L} - \frac{R}{L}\hat{i}_c - W_s\hat{i}_s - I_s\hat{\omega}_s. \tag{17}$$

This model can also be expressed in matrix form,

$$\dot{x} = Ax + B_1 u_1 + B_2 u_2 + B_3 u_3$$

,

$y = Cx$ , (18)

where, y is a vector that includes the output variables and x is a vector that includes the state variables, such as,

$$x = [\hat{i}_s \ \hat{i}_c \ \hat{v}_s \ \hat{v}_c]', \qquad y = \hat{p}_o.$$

(19)

$$x = \begin{bmatrix} \hat{i}_s & \hat{i}_c & \hat{v}_s & \hat{v}_c \end{bmatrix}', \qquad y = \hat{p}_o.$$

(19)

$y = [RI_s RI_c \ 0 \ 0]x$ . The eigen values of the A matrix are the same as the poles of the open loop system. These poles are calculated from

$$det(sI - A) = 0 (21)$$

which results in four poles located at:

Poles

$$p_1$$

and  $p_2$ :  $-\frac{l}{2}\frac{R}{L}\pm j\left(\omega_o\sqrt{l-\frac{l}{4Q^2}}-\omega_s\right)$  (22)

Poles

$$p_3$$

and  $p_4$ :  $-\frac{l}{2}\frac{R}{L}\pm j\left(\omega_o\sqrt{l-\frac{l}{4Q^2}}+\omega_s\right)$  (23)

Poles p<sub>1</sub> and p<sub>2</sub> have been considered to be "beat frequency poles", that is, because they are assumed to be located at the frequency  $\omega = \omega_o - \omega_s$ , but as the pole equations show, the pole location is dependent on the load factor Q. The beat frequency approximation is not satisfactory for low values of Q, and/or when  $\omega_s$  is very close to  $\omega_o$ . The remaining poles, p<sub>3</sub> and p<sub>4</sub> are located at high frequencies, and their effect on the small-signal response can be neglected.

### B. Power Regulation Loop Small-Signal Model

The output power is regulated by varying the duty cycle of the tank voltage, as explained in section II.

As shown in Fig. 5, the control strategy for the power regulation loop is very simple. Its main components are the multiplier and a PWM controller IC. The output power is measured by multiplying the coil voltage and current. This signal is compared against a reference voltage, if the output power signal is higher than the reference, the duty cycle will decrease. If the output power is lower than the reference, the duty cycle will increase.

Figure 5 shows the close loop for the power regulation. from which (after perturbing and linearizing), the following relationship for  $\hat{d}$  is obtained:

$$\hat{d} = -F_m K_i G_d(s) \frac{e^{-sTd}}{(s+a_p) R_b C_b} \hat{p}_o , \qquad (24)$$

where F<sub>m</sub> is the gain of the pulse width modulator (PWM), K<sub>i</sub> is the total gain of the power sensor, G<sub>d</sub>(s) is the compensator's transfer function,  $\hat{p}_o$  is the perturbed output power, and T<sub>d</sub> takes into account the driver's propagation delay. Hence,

$$G_d(s) = \frac{Z_d}{R_a} \,. \tag{25}$$

Hence,

Fig. 5 Power regulation loop schematic

Also,

$$F_{m} = \frac{\hat{d}}{\hat{v}_{d}} = \frac{1}{S_{n}T_{s}},$$

(26)

where  $S_n$  is the on-time slope magnitude of the PWM ramp, and  $T_s = \frac{2\pi}{\omega_s}$ .

Since the controller is designed to regulate the average output power, resistors  $R_a$ ,  $R_b$ , and  $C_b$  have been added to average the multiplier instantaneous output power. These components contribute to the addition of pole  $a_p$  in (24) so that

$$a_p = \frac{1}{(R_a//R_b)C_b} \,. \tag{27}$$

The perturbed output power, given in (24), can be expressed as,

$$\hat{p}_o = RI_s \hat{i}_s + RI_c \hat{i}_c . \tag{28}$$

# C. Frequency Loop Analysis

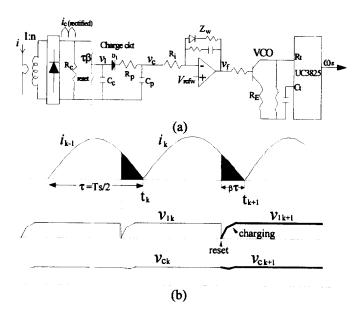

The frequency control circuit is composed of a charge measurement circuit, a compensator, and a voltage-controlled oscillator (VCO), as shown in Fig. 6(a). This circuit regulates the tank current charge during the ZVS transition (shaded area) to guarantee that ZVS is always achieved. If the measured charge is lower than desired, the circuit will increase the switching frequency to allow for additional time lagging between the tank voltage and the tank current, increasing the amount of charge. If the measured charge is larger than desired, then the switching frequency is decreased to improve the power factor. In summary, the charge circuit measures the primary current  $i_p$ , rectifies it, and measures the integral of the current during the time  $\beta \tau$ . The result of the integration is represented by v<sub>c</sub>. Voltage v<sub>c</sub> is compared with the reference voltage v<sub>refw</sub>, to produce a compensated error voltage v<sub>f</sub>. A simple VCO is built for the PWM 3825 IC which ensures that the output frequency varies directly proportionally to v<sub>f</sub> [Jovanović].

In this section, the closed loop small-signal model of the frequency-loop will be derived. Hence, it is necessary to find an equation that relates the output frequency,  $\omega_s$ , with the input current  $i_p$ . This equation is then linearized and attached to the power stage model to complete the close-loop model. The derivation of the charge model will be carried out in three steps.

Fig. 6 Frequency control: (a) circuit implementation, (b) charge circuit waveforms.

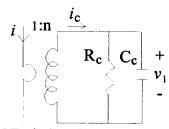

1) Solving for  $v_l$ , and  $v_c$  as a function of  $i_p$ : Figure 7 shows the equivalent circuit during the period  $\tau\beta$ . During this time, capacitor  $C_c$  is charged with i to produce voltage  $v_l$ . Diode  $D_l$  is assumed to be off during the charging of  $C_c$ , but even if  $D_l$  turns on some time during the charging of  $C_l$ , the circuit of Fig. 7 is still a good approximation, since  $R_p$  // $R_i$  >>  $R_c$  and  $C_c$ >> $C_p$ .

Thus, applying Kirchhoff's current law to the circuit in Fig. 7 results in

$$C_c \frac{dv_l}{dt} = \frac{i}{n} - \frac{v_l}{R_c} \,. \tag{29}$$

Equation.(29) provides the solution for  $\nu_1$  during the time  $\tau\beta$ ; however, from Fig. 6 (b) we see that  $v_1$  remains constant during a period  $\tau$  until it is reset. Hence, using (29) we can find the value reached by  $v_1$  at  $t_{k+1}$  ( $k=0,1,2...\infty$ .), and assume that it will remain at this value until it is reset. There is a slight decrease of  $v_1$  during the non-charging time due to resistor  $R_p/R_i$ , and its effect will be included later. From (29) and Fig. 6(b) we can observe that  $v_{1(k+1)}$  is a function of  $i_k$ , as well as  $\tau_k\beta_k$ . Since we are studying perturbations at frequencies lower than the resonant frequency, we can assume that  $v_{1k}$ ,  $i_k$ , and  $\tau_k\beta_k$  remain constant during each k period.

Fig. 7 Equivalent charge circuit during τβ.

The expression for  $v_{I(k+I)}$  is then

$$v_{I(k+1)} = \int_{t_{k+1}-\beta_k \tau_k}^{t_{k+1}} \frac{e^{-a(t_{k+1}-s)}}{nC_c} |i_k(s)| ds , \qquad (30)$$

where  $i_k(s)$  can be replaced by (4). The solution of (30) is

$v_{I(k+1)} =$

$$\frac{\left|i_{sk}\omega_{sk}-i_{ck}a-e^{-\beta_k\tau_ka}\left[\left(i_{sk}a+i_{ck}\omega_{sk}\right)\sin\beta_k\pi+\left(i_{sk}\omega_{sk}-i_{ck}a\right)\cos\beta_k\pi\right]\right|}{nC_c\left(a^2+\omega_{sk}^2\right)}$$

where a and  $\beta_k$  are defined in appendix A.

Equation (31) can be perturbed and linearized with a mathematical software package such as MapleV or Mathematica. The linearized solution around the operating point  $[V_g, D, W_g, Q]$ , is

$$\hat{v}_{I(k+1)} = A \left( E_{\infty \infty} \hat{\omega}_{sk} + E_{d\omega} \hat{d}_k + H_{is\omega} \hat{i}_{sk} + H_{ic\omega} \hat{i}_{ck} \right)$$

(32)

where A,  $E_{\omega\omega}$ ,  $E_{d\omega}$ ,  $H_{is\omega}$ ,  $H_{ic\omega}$  are gains that depend on the operating points; their definitions are given in appendix A. The selection of "E" or "H" depends on whether the multiplying variable is a current-controlled voltage source or a voltage-controlled voltage source. This will become clear in section E, where the circuit model is derived.

Equation (32) shows a discrete relationship between the output voltage  $v_{1(k+1)}$  and  $\omega_{sk}$ ,  $d_k$ ,  $i_{sk}$ , and  $i_{ck}$ . Hence, a z-transformation can be applied [Tang] as follows:

$$z\hat{v}_{l}(z) = A\left(E_{\omega\omega}\hat{\omega}_{s}(z) + E_{d\omega}\hat{d}(z) + H_{is\omega}\hat{i}_{s}(z) + H_{ic\omega}\hat{i}_{c}(z)\right). \tag{33}$$

Equation (33) can now be transformed into a sampled continuous time expression such as [Franklin]

$$\hat{v}_{l}(s) = \frac{s\tau}{(e^{s\tau} - l)} A \left( E_{\omega\omega} \hat{\omega}_{s}(s) + E_{d\omega} \hat{d}(s) + H_{is\omega} \hat{i}_{s}(s) + H_{ic\omega} \hat{i}_{c}(s) \right).$$

(34)

The sample and hold expression outside the brackets in (34) has been approximated to a power series expansions; an example of a second order polynomial is given in [Ridley]. Having  $v_1$ , we now can solve for  $v_c$  and take into account the slight discharging caused by  $(R_p // R_i)$ . Diode  $D_1$  and the  $(R_p // R_i)C_p$  circuit in Fig. 6(b) do not let  $v_c$  discharge during the resetting and charging of  $v_1$ . The disadvantage is that  $(R_p // R_i)C_p$  contributes a pole to the system; therefore, it should be designed as a high frequency pole so that it would not affect the closed loop performance. Hence,  $\hat{v}_c$  is

$$\hat{v}_c(s) = \frac{\hat{v}_I(s)}{(s+b)R_pC_p}, \qquad (35)$$

where

$$b = \frac{1}{\langle R_p || R_i \rangle C_p} \,. \tag{36}$$

2) Solving for  $v_f$  after the compensation circuit: the relationship between  $v_f(s)$  and  $v_c(s)$  is found from Fig. 6(a). This solution is perturbed and linearized to give,

$$\hat{v}_f(s) = -\hat{v}_c(s) \frac{Z_w}{R_c} = -\hat{v}_c(s) G_w(s). \tag{37}$$

3) Expressing  $\omega_s$  as a function of  $v_f$  using the VCO linear relationship: in [Jovanovic] an equation that shows the linear

relationship between  $\omega_s$  and  $v_f$  is given. The small signal solution for  $\hat{\omega}_s$  is then,

$$\hat{\omega}_s(s) = K_{VCO} \hat{v}_f(s) . \tag{38}$$

where  $K_{VCO}$  can be measured experimentally, or it can be approximated by the equation given in [Jovanovic].

The final solution for  $\hat{\omega}_s$  is obtained by replacing (34)-(37) on (38), that is,

$$\hat{\omega}_s(s) = -G_e(s)G_w(s)A\left(E_{\omega\omega}\hat{\omega}_s(s) + E_{d\omega}\hat{d}(s) + H_{is\omega}\hat{i}_s(s) + H_{ic\omega}\hat{i}_c(s)\right),(39)$$

where

$$G_e(s) = \frac{s\tau}{(e^{s\tau} - 1)} \frac{K_{VCO}}{(s + b)R_p C_p}, \qquad (40)$$

and

$$G_{w}(s) = \frac{Z_{w}(s)}{R}. \tag{41}$$

D. Error-Amplifier Compensation

The compensation scheme selected for each of the control loops is just an example among many possible implementations. The compensation used for the power regulation loop is represented by (25) and it is shown in Fig 5. This compensation network provides: (a) a pole at zero (an integrator) for high DC gain, (b) a zero at low frequency, to increase the loop gain bandwidth, and (c) a high frequency pole. The performance of this compensation network will be discussed in part IV.

The compensation used for the frequency control loop is represented by (41), and its implementation is shown in Fig. 6(a). A diode has been placed in the op amp feedback path, in order to have two different compensation schemes, depending on the error sign. The purpose of this nonlinear compensation is to have fast response, regardless of saturation, when the error is positive, and to prevent saturation, although penalizing the response time, when the error is negative. Ideally, the diode will be off when  $v_c$  is lower than  $v_{refw}$ ; hence, the error will be positive. The positive-error compensation includes a pole at zero frequency, for high DC gain, and a zero at low frequency. Positive error means that the inverter frequency is too low and that ZVS might be lost. Thus, it is acceptable to have the op amp saturated with a positive output to quickly regain ZVS. On the other hand, the diode will be on when vc is greater than vrefw; thus, the error will be negative. In this case, the pole is not at zero, but moves to a slightly higher frequency, thus decreasing the high DC gain.. The negative error compensation will not saturate the op amp as quickly as in the positive case. A thorough analysis of the closed-loop performance of this nonlinear compensation is not simple, especially when analyzing its behavior during transient response. Transient behavior analysis is beyond the scope of this paper. Experimental loopgain curves will be given in part IV. It will be shown that this compensation behaves satisfactorily; however, combinations of pole and zero placements should be tested to further improve the gain and the bandwidth.

# E. Complete Small-Signal Model

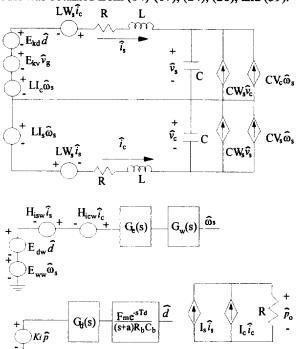

The complete small-signal model is shown in Fig. 8. This model was obtained from (14)-(17), (24), (28), and (39).

Fig. 8 Small-signal model includes power-stage, frequency control loop and phase-shift control loop.

The small-signal model as shown in Fig. 8 can now be implemented using PSPICE, MATLAB or similar simulation software, to obtain the frequency response of the system.

#### IV. EXPERIMENTAL VERIFICATIONS

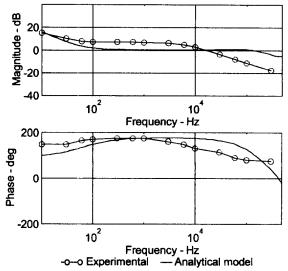

Figure 9 shows the experimental and analytical frequency loop-gain curves with the power regulation loop open. The operating point and the PSPICE program are given in appendix B. From these curves it can be seen that the frequency loop is stable. However, its gain is relatively low as well as the crossover frequency. Modifications to the compensation circuitry can be made to increase the gain and crossover frequency. Though, as explained in section III D, the DC gain can not be large when the error is negative to prevent saturation in the negative direction. Additional, analysis of the frequency loop-gain at different operating points show that the gain decreases as the load resistance increases, the load resistance increases during the heating cycle. Therefore, the compensation for this loop should be design for the highest load resistance point.

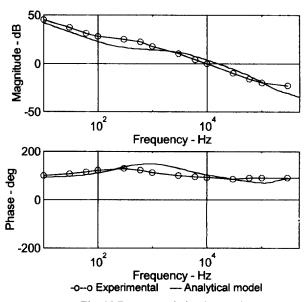

Figure 10 shows the experimental and analytical power regulation loop-gain curves with the frequency loop closed. The operating points of Fig. 10 curves are similar to that of Fig. 9 except for: f<sub>s</sub>=554 kHz; V<sub>g</sub>=103 V; D=0.62. The compensation used for the power regulation loop satisfactorily provides high DC gain and large phase margin.

Fig. 9 Frequency control loop-gain.

Fig. 10 Power regulation loop-gain.

# V. CONCLUSIONS

The complete closed-loop small-signal model for a phase-shift-controlled series-resonant inverter used for induction heating was obtained using the extended describing function method. The model predictions were verified with experimental data measured from a lab prototype

The small signal model proved to be a useful tool to analyze the performance of the two control loops: the phase-shift control loop and the frequency control loop. In particular the frequency loop-gain analysis showed that improvements could be made to increase its gain and its bandwidth. This model will be used for further closed-loop performance studies at various load operating points, which generally occur during the heating cycle of an induction heating system.

#### REFERENCES

Franklin, G. F., Powell, J. D., Digital Control of Dynamic Systems, Addison-Wesley, 1980 pp.77-90

Grajales, L., Sabaté, J. A., Wang, K. R., Tabisz, W. A., F. C. Lee, "Design of a 10 k W, 500 kHz Phase-Shift Controlled Series-Resonant Inverter for Induction Heating," Proc. of Industry Applications Society, Toronto, Canada 1993 pp. 843-849

Jovanović, M. M. Hopkins, D. C., Lee, F. C., "Design Aspects for High Frequency Off-line Quasi-Resonant Converters", Proc. High Frequency Power Conversion Conference; Washington, D.C., pp. 83-97, 1987.

Kassakian, J. G., Schlecht, M. F., Verghese, G. C., Principles of Power Electronics, Addison Wesley, 1991 pp 329-360.

Nakaoka, M., Maruhashi, T., Koga, T., Sugawara, S., and Nishimura, T., , A Phase-Difference Angle Control-Mode PWM High-Frequency Resonant Inverters Using Static Induction-Transistors and-Thyristors, \* Proc. Power Electronics Specialist's Conference; Blacksburg, Virginia, 1987.

Ridley, R. B., A New Small-Signal Model for Current-Mode Control, Ph. D. Dissertation, Virginia Tech, Blacksburg, VA 1990.

Sabaté, J. A., Farrington, R. W., Jovanović, M. M, Lee, F. C., "Effect of Switch Capacitance on Zero-Voltage Switching of Resonant Converters," Proc. Applied Power Electronics Conference; Toledo, Spain, 1992.

Tang, W., Lee, F. C., Ridley, R. B., Cohen, I., "Charge Control: Modeling, Analysis and Design", Proceedings of the Virginia Power Electronics Center Seminar, Blacksburg, VA, 1992 pp. 47-56.

Yang, E., Lee, F. C., Jovanović, M. M., "Extended Describing Function Technique Applied to the Modeling of Resonant Converters", Proceedings of the Virginia Power Electronics Center Seminar, Blacksburg, VA, 1991 pp. 179-191.

#### APPENDIX A

Operating Points:

$$I_{s} = \frac{V_{g}W_{s}^{2}C^{2}R}{\Delta}, \quad I_{c} = \frac{V_{g}W_{s}C(1 - W_{s}^{2}LC)}{\Delta}, \quad V_{s} = \frac{V_{g}(1 - W_{s}^{2}LC)}{\Delta},$$

$$V_{c} = \frac{V_{g}W_{s}CR}{\Delta}, \quad \Delta = W_{s}^{4}C^{2}L^{2} - 2W_{s}^{2}CL + 1 + W_{s}^{2}C^{2}R^{2}. \quad (A1)$$

Power Stage Small-Signal Model Constants

$$E_{kd} = \frac{2V_g}{L} cos(\frac{\pi}{2}D), \quad E_{kv} = \frac{4}{\pi L} sin(\frac{\pi}{2}D)$$

(A2)

Frequency Control Constants:

From (31) let

$$V_{I\_sigm} = \frac{I_s W_s - I_c a - e^{-a\frac{B}{W_s}} \left[ (I_s a + I_c W_s) sin B + (I_s W_s - I_c a) cos B \right]}{n C_c \left( a^2 + W_s^2 \right)}$$

then,

$$A = \begin{cases} 1, \text{ when } (V_{I\_sign}) > 0 \\ -1, \text{ when } (V_{I\_sign}) < 0 \\ \text{Not defined when } (V_{I\_sign}) = 0 \end{cases}$$

(A3)

$$B = \beta \pi = -\arctan(\frac{I_c}{I}) - \frac{\pi}{2}(I - D)$$

(A4)

$$H_{is\omega} = KK \left[ \frac{I_c e^{-a\frac{B}{W_s}}}{(I_s^2 + I_c^2)} \left[ \frac{a}{W_s} H I + H 2 \right] - e^{-a\frac{B}{W_s}} (a \sin B + W_s \cos B) + W_s \right]$$

(A5)

$$H_{ic\omega} = KK \left[ \frac{I_s e^{-a\frac{B}{W_s}}}{(I_s^2 + I_c^2)} \left[ -\frac{a}{W_s} H I - H 2 \right] + e^{-a\frac{B}{W_s}} (-W_s \sin B + a\cos B) - a \right]$$

(A6)

$$E_{d\omega} = e^{-a\frac{B}{W_s}} KK \left[ \frac{a\pi}{2W_s} H l + \frac{\pi}{2} H 2 \right]$$

(A7)

$$E_{\omega\omega} = KK \left[ I_s - e^{-a\frac{B}{W_s}} \left( HI(\frac{aB}{W_s^2} - \frac{2W_s}{a^2 + W_s^2}) + I_c \sin B + I_s \cos B \right) - \frac{2W_s}{a^2 + W_s^2} (I_s W_s - I_c a) \right]$$

(A8)

$$H1 = ((I_s a + I_c W_s) \sin B + (I_s W_s - I_c a) \cos B)$$

(A9)

$$H2 = \left(-(I_s a + I_c W_s) cos B + (I_s W_s - I_c a) sin B\right) \tag{A10}$$

$$KK = \frac{1}{nC_c(a^2 + W_s^2)}, \quad a = \frac{1}{R_cC_c},$$

(A11)

Pspice frequency loop-gain implementation:

SRI-PSC frequency loop gain, Small Signal Model

\* Circuit parameters Q=2.2 L=6.77uH C=19.3nF N=4 R=10

\* Operating Point Vg=136 Fs=496 khz D=0.97

vg 20 0 ac 0 rg 20 0 1k vd 50 0 ac 0 rd 50 0 1k

\* The upper part of the resonant tank

es 1 0 70 0 -.04263m ekv 2 1 20 0 1.272 ekd 3 2 50 0 12.813 vpis 3 4 dc 0 hzs 5 4 vpic 21.0134 rs 5 6 10 ls 6 7 6,77u cs 7 0 19.3n gis 0 7 8 0 0.0599 gws 0 7 70 0 -4.696u

\* The lower part of the resonant tank

ec 0 13 70 0 0 09868m vpic 13 12 dc 0 hzc 12 10 vpis 21.0134 10 9 10 8 0 19.3n 8 0 7 0 0.0599 gwc 8 0 70 0 -2.029u

\* Opamp frequency loop eopf 70 0 0 80 1000k ropf 70 0 1000k r4 85 80 5.6k \*r5 80 70 120k

r6 80 86 27k c6 86 70 0.10u

\* He(s) (The gain Kvco was included in His, Hic, Ew, Ed)

eGe 85 0 LAPLACE  $\{v(90)\} = \{13.77*s/((exp(s*1e-6)-1)*(s+14.077e6))\}$

eww 31 0 70 0 -0.0168 edw 32 31 50 0 287.22e3 hisw 33 32 vpis -3.4913e3

hicw 84 33 vpic -16.5e3

\* The injected signal vcl 90 84 ac l rge 90 0 1000k

\*The loop gain measurement is V(84)/V(90)

\* Vdb(84)/Vdb(90)= Vdb(84)-Vdb(90) Vp(V(84)/V(90))=Vp(84)-vp(90) print ac vdb(90) vdb(84) vp(90) vp(84)

.ac dec 20 10 500k .probe