Date: 2005/03/11

## **Specifications for Approval**

| Customer   | : |               |        |  |

|------------|---|---------------|--------|--|

|            |   |               |        |  |

| Model name | : | GG1306B5SAN6T | REV: A |  |

Description : LIQUID CRYSRAL DISPLAY MODULE

| DESIGN | CHECK | APPROVED |

|--------|-------|----------|

|        |       |          |

- **\* CONTENTS**

- 1. FEATURES

- 2. MECHANICAL SPECIFICATIONS

- **3. ELECTICAL SPECIFICATIONS**

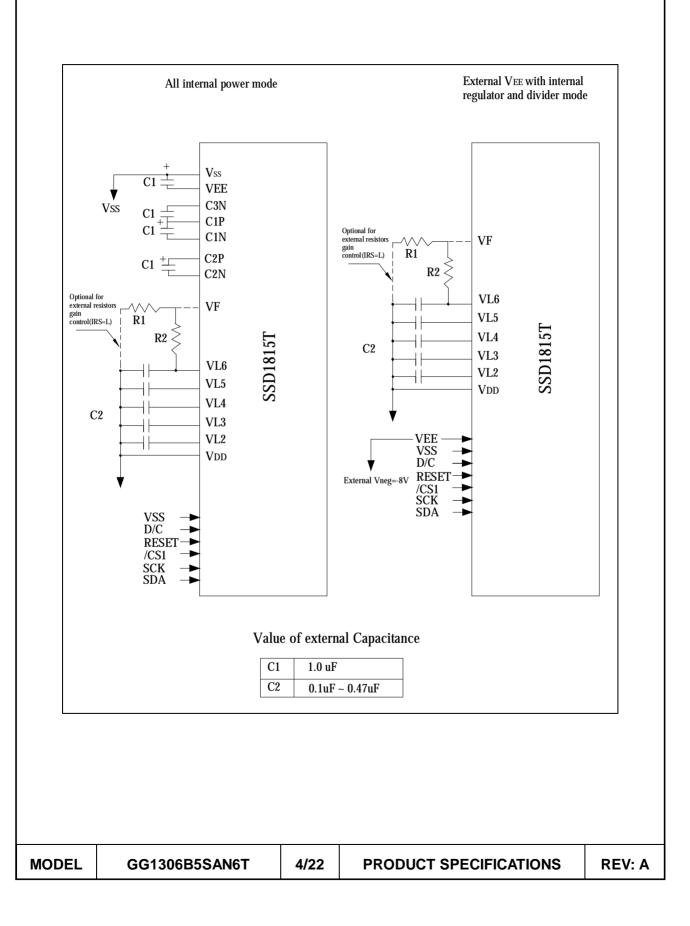

- 4. POWER SUPPLY

- 5. ELECTRO-OPTICAL CHARACTERISTICS

- 6. INTERFACE PIN FUNCTION

- 7. COMMAND LIST

- 8. TIMING CHARACTERISTICS

- 9. QUALITY SPECIFICATION

- 10. RELIABILITY

- 11. HANDLING PRECATION

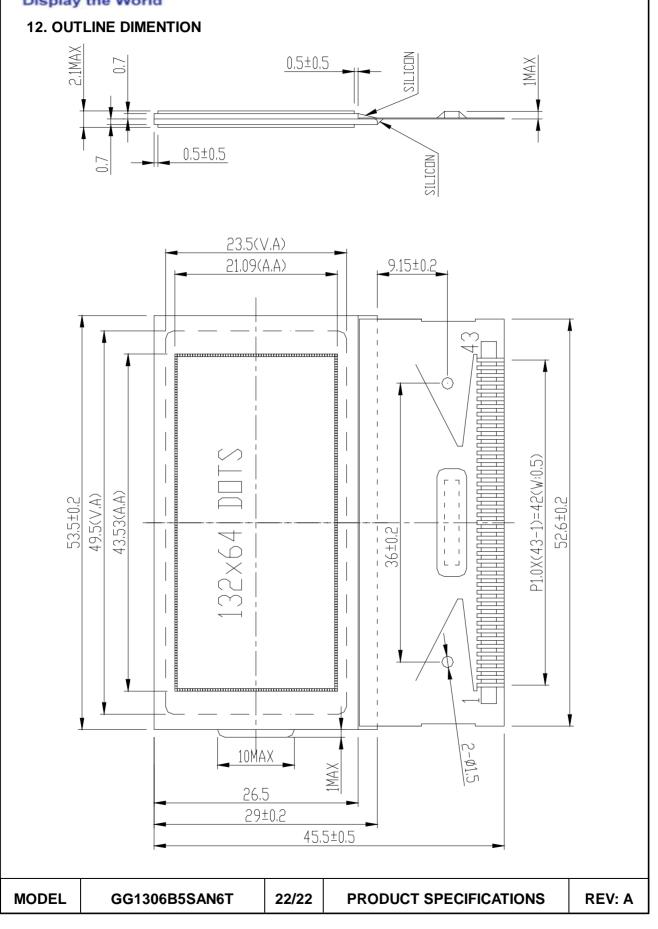

- **12 OUTLINE DIMENTION**

- X ANNEX : 1. SAMPLES OUTGOING INSPECTION REPORT

- 2. DEFINITION OF LCM SERIES NUMBER

- 3. REVISION RECORD

| MODEL | GG1306B5SAN6T | 1/22 | PRODUCT SPECIFICATIONS | REV: A |

|-------|---------------|------|------------------------|--------|

#### **1. FEATURES**

The features of LCD are as follows

| * Display mode         | : STN, Positive, Reflective |

|------------------------|-----------------------------|

| * Color                | : Display dot : Dark Blue   |

|                        | Background: Yellow-Green    |

| * Display Format       | : 132Dots × 64Dots          |

| * IC                   | : Solomon SSD1815T          |

| * Interface Input Data | : 8-Bit Parallel or Serial  |

| * Driving Method       | : 1/64 Duty, 1/9 Bias       |

| * Viewing Direction    | : 6 O'clock                 |

#### 2. MECHANICAL SPECIFICATIONS

| ltem                   | Specification                 | Unit |

|------------------------|-------------------------------|------|

| Module Size            | 53.5(W) X 45.5(H) X 2.1MAX(T) | mm   |

| Viewing Area           | 49.5(W) X 23.5(H)             | mm   |

| Effective Display Area | 43.53(W) X 21.09(H)           | mm   |

| Number of Dots         | 132 X 64Dots                  |      |

| Dot Size               | 0.3(W) X 0.3(H)               | mm   |

| Dot Pitch              | 0.33(W) X 0.33(H)             | mm   |

#### 3. ELECTRICAL SPECIFICATIONS

3-1. Absolute Maximum Ratings (Vss=0V)

| ltem                         | Symbol  | Star    |   |         |      |

|------------------------------|---------|---------|---|---------|------|

| item                         | Symbol  | Min.    |   | Max.    | Unit |

| Supply Voltage For Logic     | Vdd-Vss | -0.3    | _ | +4.0    | V    |

| Supply Voltage For LCD Drive | VIcd    | -0.3    | _ | +16.0   | V    |

| Input Voltage                | Vin     | Vss-0.3 | _ | Vdd+0.3 | V    |

| Operating Temp.              | Тор     | -20     | - | +70     | °C   |

| Storage Temp.                | Тѕт     | -25     | - | +75     | °C   |

| MODEL | GG1306B5SAN6T | 2/22 | PRODUCT SPECIFICATIONS | REV: A |

|-------|---------------|------|------------------------|--------|

## 3. ELECTRICAL SPECIFICATIONS (Continued)

| Item                     |           | Symbol          | Test<br>Condition        | Min.   | Тур. | Max.   | Unit |

|--------------------------|-----------|-----------------|--------------------------|--------|------|--------|------|

| Supply Voltage For Logic |           | Vdd – Vss       | -                        | 2.4    | 3.0  | 3.5    | V    |

| Supply Voltage For LCD   |           | Vdd – Vo        | <b>Ta=25</b> ℃           | 8.5    | 9.0  | 9.5    | V    |

|                          | "H" Level | V IH            |                          | 0.8Vdd | _    | Vdd    | V    |

| Input Voltage            | "L" Level | V IL            |                          | Vss    | _    | 0.2Vdd | V    |

|                          | "H" Level | V <sub>OH</sub> | I <sub>он</sub> = -0.1mA | 0.9Vdd | _    | Vdd    | V    |

| Output Voltage           | "L" Level | V <sub>OL</sub> | $I_{OL}=0.1 \text{mA}$   | 0      | _    | 0.1Vdd | V    |

| Current Con              | sumption  | I <sub>DD</sub> | Vdd = 3.0V               | -      | 0.38 | 2.0    | mA   |

NOTE: 1)Duty ratio=1/64, Bias=1/9

2).Measured in Dots ON-state

| MODEL | GG1306B5SAN6T | 3/22 | PRODUCT SPECIFICATIONS | REV: A |

|-------|---------------|------|------------------------|--------|

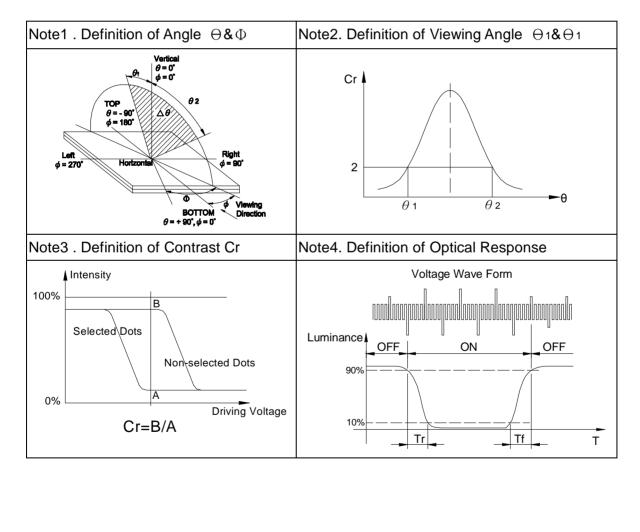

#### 5. ELECTRO - OPTICAL CHARACTERISTICS

| ltem              | Symbol         | Temp.        | Min. | Тур. | Max. | Unit | Conditions         | Note |

|-------------------|----------------|--------------|------|------|------|------|--------------------|------|

| Viewing           | θ <b>2</b> −θ1 | <b>25</b> ℃  | 30   | 80   | -    | Dog  |                    | 1 0  |

| Angle             | Φ              | 250          | 60   | 70   | -    | Deg. | -                  | 1,2  |

| Contrast<br>Ratio | Cr             | <b>25</b> ℃  | 2    | 3.9  | 4.7  | -    | ⊖=0°<br>Φ=0°       | 3    |

| Response          | Ta             | <b>25</b> °C | -    | 120  | 250  |      | ⊖=0°               | 4    |

| Time(rise)        | Tr             | <b>0</b> °C  | -    | 950  | 1150 | ms   | $\Phi = 0^{\circ}$ | 4    |

| Response          | Τ(             | <b>25</b> °C | -    | 160  | 250  |      | ⊖=0°               | 4    |

| Time(fall)        | Tf             | <b>0</b> °C  | -    | 950  | 1150 | ms   | <b>⊕=0°</b>        | 4    |

| Μ | 0 | D | Ε | L |  |

|---|---|---|---|---|--|

6. Interface Pin Function

| Pin   | Symbol  | I/O    |                                                                       |                                                            | Function                                   |            |  |

|-------|---------|--------|-----------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------|------------|--|

|       | Dummy   |        | No connec                                                             | cted                                                       |                                            |            |  |

|       |         |        | LCD AC s                                                              | signal inp                                                 | put /output. When SSD1815 is used in mas   | ter /slave |  |

| 1     | 1 M I/O |        |                                                                       | mode(multi-chip). The M pins must be connected to each oth |                                            |            |  |

| 1     | IVI     | 1/0    | M/S = " H                                                             | [ " : Outp                                                 | ut                                         |            |  |

|       |         |        | M/S = " L                                                             | " : Input                                                  |                                            |            |  |

| 2     | CL      | I/0    | Display cl                                                            | ock inpu                                                   | t/output . When SSD1815 is used in maste   | r / slave  |  |

| 2     | CL      | 1/0    | mode(mul                                                              | ti-chip).                                                  | The CL pins must be connected to each of   | ther.      |  |

|       |         |        | LCD display blanking control input/output. When SSD1815 is used in    |                                                            |                                            |            |  |

| 3     | /DOF    | I/O    | master/slave mode (multi-chip), the DIPS pins must be connected to    |                                                            |                                            |            |  |

| 5     | /DOF    | 1/0    | each other MS="H": Output                                             |                                                            |                                            |            |  |

|       |         |        | MS="L": Input                                                         |                                                            |                                            |            |  |

| 4     | CS1B    | Ι      | Chip selec                                                            | et inputs                                                  | pins.                                      |            |  |

|       |         |        | Data/instruction I/O is enabled only when CS1B is "L" and CS2 is "H". |                                                            |                                            |            |  |

| 5     | CS2     | Ι      | When chip select is non-active, DB0 to DB7 may be high impedance      |                                                            |                                            | pedance    |  |

|       |         |        |                                                                       |                                                            |                                            |            |  |

| 6     | /RES    | Ι      | Reset inpu                                                            | ıt pin. W                                                  | hen RESETB is "L", initialization is execu | ted.       |  |

|       |         |        | Register S                                                            | elect inp                                                  | ut                                         |            |  |

| 7     | D/C     | I      | D/C = " H                                                             | ["" the d                                                  | lata on DB[7~0] is display data            |            |  |

|       |         |        | D/C = " L                                                             | " " the d                                                  | ata on DB[7~0] is control data             |            |  |

|       |         |        | When inte                                                             | erfacing t                                                 | o a 6800 series MPU:Active High.           |            |  |

| 8     |         | т      | RW_WR=                                                                | ="H": Re                                                   | ad                                         |            |  |

| 8     | RW_WR   | I      | RW_WR=                                                                | ="L": Wr                                                   | ite                                        |            |  |

|       |         |        | When inte                                                             | erfacing t                                                 | o an 8080-series MPU , RW_WR is enable     | ed at low. |  |

|       |         |        | •                                                                     |                                                            |                                            |            |  |

|       |         |        |                                                                       |                                                            |                                            |            |  |

|       |         |        |                                                                       |                                                            |                                            |            |  |

|       |         |        |                                                                       |                                                            |                                            |            |  |

| MODEL | - GG13  | 06B5SA | N6T                                                                   | 6/22                                                       | PRODUCT SPECIFICATIONS                     | REV: A     |  |

#### 6. Interface Pin Function (Continue)

| 35       | VDD        | Supply | Power supply .                                                                                                           |  |  |  |  |

|----------|------------|--------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 34       | VF         | Ι      | This pin is the input of the built-in voltage regulator.                                                                 |  |  |  |  |

| 33       | VL6        | I/O    | This pin is the most negative LCD driving voltage. It can be supplied externally or generated by the internal regulator. |  |  |  |  |

| 32       | VL5        |        |                                                                                                                          |  |  |  |  |

| 31       | VL4        | 4      | $VDD \ge VL2 \ge VL3 \ge VL4 \ge VL5 \ge VL6$                                                                            |  |  |  |  |

| 30       | VL3        | I/O    | by the internal bias divider. They have the following relationship:                                                      |  |  |  |  |

| 29       | VL2        | 4      | LCD driving voltages. They can be supplied externally or generated                                                       |  |  |  |  |

|          |            | Suppry |                                                                                                                          |  |  |  |  |

| 27       | VFS<br>VDD | Supply | voltage regulator. Power supply .                                                                                        |  |  |  |  |

| 27       |            | I      | This pin provide an external voltage reference for the internal                                                          |  |  |  |  |

| 25       | C2P        | 1      |                                                                                                                          |  |  |  |  |

| 24<br>25 | C1N<br>C2N | 0      | s connected between these pin.Different connection will result in ifferent DC-DC converter multiple factor, 2X,3X,or 4X. |  |  |  |  |

| 23       | C1P<br>C1N |        | When internal DC-DC voltage converter is used, external capacitor                                                        |  |  |  |  |

| 22       | C3N        | -      |                                                                                                                          |  |  |  |  |

| 21       | VEE        | Supply | Power supply .                                                                                                           |  |  |  |  |

| 20       | VSS1       | I      | Reference voltage input for internal DC-DC converter.                                                                    |  |  |  |  |

| 19       | VSS        | Supply | Ground.                                                                                                                  |  |  |  |  |

| 18       | VDD        | Supply | Power supply .                                                                                                           |  |  |  |  |

| 17       | D7_SDA     |        |                                                                                                                          |  |  |  |  |

| 16       | D6_SCK     | -      |                                                                                                                          |  |  |  |  |

| 15       | D5         | 4      | When Chip select is not active, DB7 to DB0 will be high impedance.                                                       |  |  |  |  |

| 14       | D4         | 1/0    | D5 to D0 : high impedance.                                                                                               |  |  |  |  |

| 13       | D3         | I/O    | D6 : Serial input clock (SCK)                                                                                            |  |  |  |  |

| 12       | D2         |        | D7 : Serial input data (SDA)                                                                                             |  |  |  |  |

| 11       | D1         |        | When the serial interface selected ( $PS = "L"$ )                                                                        |  |  |  |  |

| 10       | D0         |        | this signal is Low, data bus output is enabled.                                                                          |  |  |  |  |

|          |            |        | This input connects the RD signal of the 8080-series MPU. While this signal is Low , data bus output is enabled.         |  |  |  |  |

| 9        | E/RD       | I      | When interfacing to 8080-series MPU : Active Low                                                                         |  |  |  |  |

|          |            | _      | This is used as an enable clock input in of the 6800-series MPU                                                          |  |  |  |  |

|          |            |        | When interfacing to a 6800 series MPU : Active High.                                                                     |  |  |  |  |

MODEL

**Display the World**

| 6. Interface Pin Function (Continue) |        |   |                                                                                                                                                                                                |  |  |

|--------------------------------------|--------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 36                                   | M/S    | Ι | This pin is the master / slave mode selection input.                                                                                                                                           |  |  |

| 37                                   | CLS    | Ι | This pin is the intermal clock enable pin.                                                                                                                                                     |  |  |

| 38                                   | C68/80 | Ι | This pin is microprocessor interface selection input. When the pin<br>is pulled high, 6800 series interface is selected and when the pin<br>pulled low, 8080 series MCU interface is selected. |  |  |

| 39                                   | PS     | I | This pin is serial /parallel interface selection input.<br>PS="H": Parallel mode                                                                                                               |  |  |

| 40                                   | /HPM   | I | PS="L": Serial mode<br>This pin is the control input of High Power Mode. The function<br>of this pin is only enabled for High Power model which required<br>special ordering                   |  |  |

| 41                                   | IRS    | Ι | This is the input pin to enable the internal resistors network for the voltage regulator.IRS="H": Internal resistors; IRS="L": External resistors.                                             |  |  |

|                                      | Dummy  |   | No connection                                                                                                                                                                                  |  |  |

## 6. Interface Pin Function (Continue)

| MODEL | GG1306B5SAN6T | 8/22 | PRODUCT SPECIFICATIONS | REV: A |

|-------|---------------|------|------------------------|--------|

## 7. COMMAND LIST

| Bit Pattern                                                                  | Write Com <u>mand</u><br>(D/C=0, R/W(WR)=0. E(i |                                | Comment                                                                                                                                                                                                                                                                                                   |                         |  |

|------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|

| 0000X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> >                           | Set Lower Column Addre                          |                                | Set the lower nibble of the colume address replicitly $\chi_{\gamma}\chi_{\gamma}\chi_{\gamma}\chi_{1}\chi_{0}$ as data bits. The initial display line registe 2000b during PCR.                                                                                                                          | 1                       |  |

| 0001X <sub>3</sub> X <sub>2</sub> X₁>                                        | G Set Higher Column Adda                        |                                | Set the higher hibble of the colume address register usi X <sub>3</sub> X <sub>2</sub> X <sub>4</sub> X <sub>4</sub> as data bits. The initial display line register is reset 2000b during PCR.                                                                                                           |                         |  |

| 00100X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>                            | Set Internal Regulator R                        |                                | Internal regulator gain increases as $X_0 X_1 X_0$ increases to 111p. At POR, $X_2 X_1 X_0 = 100b$ .                                                                                                                                                                                                      | i from 000b             |  |

| 00101X <sub>6</sub> X <sub>1</sub> X <sub>6</sub> Set Power Control Register |                                                 |                                | $X_0$ =0 turns off the output op amp buffer (POR)<br>$X_0$ =1 turns on the output op-amp buffer<br>$X_1$ =0 turns off the internal regulator (POR)<br>$X_1$ =1 turns on the internal regulator<br>$X_2$ =0 turns off the internal voltage booster (POR)<br>$X_2$ =1 turns on the internal voltage booster |                         |  |

| 01X <sub>6</sub> X <sub>2</sub> X <sub>3</sub> X <sub>2</sub> X              | Set Display Starl Line                          |                                | Set display RAM display start line register from<br>X ჯ კარებე IXე.<br>Display start line register is reset to 000000 ouring PO                                                                                                                                                                           | -                       |  |

| 10000001<br>** X <sub>2</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> 3 | Set Contrast Control Reg                        |                                | Set Contrast level from 64 contrast steps. Contrast ind<br>decreases) as $X_3X_3X_2X_2X_3X_3$ is increased.<br>$X_5X_2X_2X_2X_1X_0 = 100000b$ (POR)                                                                                                                                                       | reases (V <sub>LS</sub> |  |

| 1010000X <sub>0</sub>                                                        | Sot Sogment Ro-map                              |                                | X₀=0, column address 0Ch is mapped to SEG0 (POR)<br>X₀=1, column address 82h is mapped to SEG0<br>Refer to Figure 5 for example.                                                                                                                                                                          |                         |  |

| 1010001X;;                                                                   | Set LCC Bias                                    |                                | $X_0{=}0$ 1/9 bias (POR) $X_0{=}1$ 1/7 bias For setting bias ratio to 1/4, 1/5, 1/6 or 1/8, see Extended Command Table                                                                                                                                                                                    |                         |  |

| 1010010X <sub>0</sub>                                                        | Set Entire Display On/Ol                        |                                | X₀=0 nor⇔al display (POR)<br>X₀=1 entire display on                                                                                                                                                                                                                                                       |                         |  |

| 1010011X <sub>0</sub>                                                        | Set Normal/Reverse Disp                         |                                | X <sub>0</sub> =0 normal display (POR)<br>X <sub>0</sub> =1 reverse display                                                                                                                                                                                                                               |                         |  |

| 1010111X <sub>2</sub>                                                        | Set Display On/Off                              |                                | X <sub>0</sub> =0_turns off LCD panel (POR)<br>X <sub>0</sub> =1_turns on LCD panel                                                                                                                                                                                                                       |                         |  |

| 101+X <sub>8</sub> X <sub>2</sub> X <sub>1</sub> >                           | 6 Set Page Acdress                              |                                | Set GDDRAN Page Address (0-3) using $X_3 X_2 X_1 X_0$                                                                                                                                                                                                                                                     |                         |  |

| 1100X <sub>3</sub>                                                           | Set COM Cutput Scan D                           |                                | Xq=0 normal mode (POR)<br>Xg=1 remapped mode. COM0 to COM[N-1] becomes COM[<br>to COM0 when Multiplex ratio is equal to N. See Figu<br>as an example for N equal to 64.                                                                                                                                   |                         |  |

| 111000000                                                                    | Set Read-Modify-Write M                         |                                | Read-modify-write mode will be entered in which the coll<br>accrease will not be incremented during display data raad. At P<br>Read-modify-write mode is turned OFF                                                                                                                                       |                         |  |

| 11100010                                                                     | Software Reset                                  |                                | Initialize the internal status register.                                                                                                                                                                                                                                                                  |                         |  |

| 11101110                                                                     | Set End of Read-Modify-                         |                                | Exit Read-modify-write mode, Column address before<br>mode will be restored. At POR, Read-modify-write mod                                                                                                                                                                                                | - 1                     |  |

| 1010110X <sub>0</sub>                                                        | Set Indicator On/Off                            |                                | $X_0 = 0$ : indicator off (POR, no need of second comman $X_0 = 1$ : indicator on (second command byte required)                                                                                                                                                                                          | nd byte)                |  |

| $\label{eq:constraint} \begin{array}{llllllllllllllllllllllllllllllllllll$   |                                                 | nd is required<br>tor On" com- | $X_1X_0 = 00$ : Indicator off<br>d $X_1X_0 = 01$ : indicator on and blinking at ~1 second interval<br>- $X_1X_0 = 10$ : indicator on and blinking at ~1/2 second interval<br>X_1X_0 = 11: indicator on constantly                                                                                         |                         |  |

| 11100011                                                                     | NCP                                             |                                | Command for No Operation                                                                                                                                                                                                                                                                                  |                         |  |

| 11110 <b>0</b> C0                                                            | Test Mode Reset                                 |                                | Reserved for IC festing, Do NOT use,                                                                                                                                                                                                                                                                      |                         |  |

| 11-1 ****                                                                    | Set Test Mode                                   |                                | Reserved for IC testing. Do NOT use.                                                                                                                                                                                                                                                                      |                         |  |

| *******                                                                      | Set Power Save Mode                             |                                | Standby or sleep mode will be entered with compound                                                                                                                                                                                                                                                       | commands                |  |

| IODEL                                                                        | GG1306B5SAN6T                                   | 9/22                           | PRODUCT SPECIFICATIONS                                                                                                                                                                                                                                                                                    | REV: A                  |  |

## 7. COMMAND LIST (Continued )

| Bit Pattern                                                                                                                                       | Read Command<br>(D/C-C, R/W(WR)-1, E(RD)-0) | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>2</sub> D <sub>2</sub> D₋D <sub>2</sub><br>(Data Read Back from the<br>driver) | Status Register Read                        | D <sub>7</sub> =0: indicates an internal operation is completed<br>D <sub>7</sub> =1: indicates an internal operation is in progress.<br>D <sub>8</sub> =0: indicates reverse segment mapping with column address<br>D <sub>8</sub> =1: indicates normal segment mapping with column address<br>D <sub>5</sub> =0: indicates the display is ON<br>D <sub>5</sub> =1: indicates the display is OFF<br>D <sub>7</sub> =0: initialization is not in progress<br>D <sub>2</sub> =1: initialization is in progress after RES or software reset<br>D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> = 1010, these 4-bit is fixed to 1010 which could be used<br>to identify as Solomon Systech Device. |

#### Extended Command Table

| Blt Pattern                                                                                             | Command                                                                                                                                                             | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10101000<br>00X5X4X3X5X1X5                                                                              | $X_5 X_2 X_3 X_2 X_1 X_0^\circ$ Set Multiplex Ratio                                                                                                                 | To select multiplex ratio N from 2 to 65 [Included loop Line] N = $X_5 X_2 X_9 X_5 X_1 X_0 + 2$ , eg. N = 111111b + 2 = 65 (POR)                                                                                                                                                                                                                                                                                                                 |

| 10101001<br>X7X8X=X2X1X2X1X2                                                                            | X · X <sub>U</sub> : Set Baa Reto                                                                                                                                   | $\begin{split} X_1 X_0 &= 00; \ 1/8, \ 1/6 \\ X_1 X_0 &= 01; \ 1/6, \ 1/5 \\ X_1 X_0 &= 10; \ 1/6, \ 1/7 \ (POR) \\ X_1 X_0 &= 11; \ Prohibited \end{split}$                                                                                                                                                                                                                                                                                     |

|                                                                                                         | $X_4 X_3 X_2$ : Set TC Value                                                                                                                                        | $X_4 X_7 X_2 = 000; -0.01 %/C (TC0, POR)$<br>$X_4 X_3 X_2 = 010; -0.10 %/C (TC2)$<br>$X_4 X_3 X_2 = 100; -0.18 %/C (TC4)$<br>$X_4 X_3 X_2 = 111; -0.25 %/C (TC7)$<br>$X_4 X_3 X_2 = 001, 011, 101; T00; Reserved$                                                                                                                                                                                                                                |

|                                                                                                         | $X_{\pi}X_{\theta}X_{\eta};$ Modify Osc. Freq.                                                                                                                      | Increase the value of $X_7X_3X_5$ will increase the oscillator frequency and vice versa. This command is not recommenced to be used. $X_7X_5X_5 = 0.11(POR)$                                                                                                                                                                                                                                                                                     |

| 1010101X <sub>0</sub>                                                                                   | X <sub>D</sub> : Sct 1/4 Bias Ratio                                                                                                                                 | $X_{\rm C}$ = 0: use Normal Setting (POR) $X_{\rm C}$ = 1: fixed at 1/4 Bias                                                                                                                                                                                                                                                                                                                                                                     |

| 11010010<br>0X <sub>E</sub> X <sub>C</sub> 0C010                                                        | X <sub>6</sub> X <sub>5</sub> : Sot Total Frame Phases                                                                                                              | The On/Off of the Static Icon is given by 3 phases/1 phase overlap<br>ping of the M and MSTAT signals. This command set how many<br>phases of dividing the M/NSTAT signals for each frame<br>The more the phases. The loss the overlapping and thus the lowe<br>the effective driving voltage<br>$X_3X_5 = 00; 3 \text{ phases}$<br>$X_9X_9 = 01; 5 \text{ phases}$<br>$X_2X_5 = 10; 7 \text{ phases}$ (PCR)<br>$X_3X_5 = 11; 16 \text{ phases}$ |

| 11⊡10011<br>DOX <sub>5</sub> X <sub>4</sub> X <sub>3</sub> X <sub>3</sub> X <sub>1</sub> X <sub>2</sub> | X <sub>6</sub> X <sub>2</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> : Set Display Offset<br>(for mux ratic has been<br>set less than 64 only) | After POR, $X_3X_2X_3X_2X_1X_0 = 0$<br>After setting muximation less than 64, data will be displayed at Contend<br>of matrix. See Table 1.<br>To move display towards Row 0 by L, $X_5X_2X_3X_2X_1X_2 = L$<br>To move display away from Row 0 by L, $X_5X_2X_3X_2X_1X_1 = 64$ L<br>Note: max. value of L = (64 - display mux)/2                                                                                                                  |

| MODEL | GG1306B5SAN6T | 10/22 | PRODUCT SPECIFICATIONS | REV: A |

|-------|---------------|-------|------------------------|--------|

|       |               |       |                        |        |

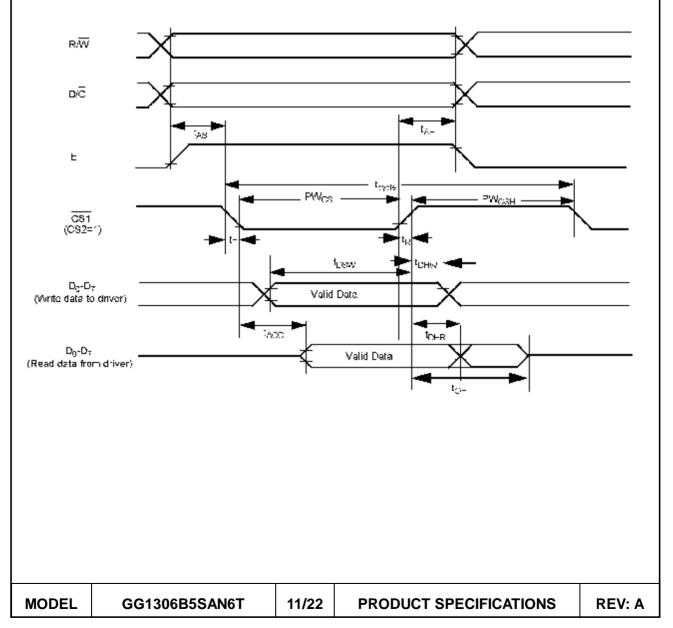

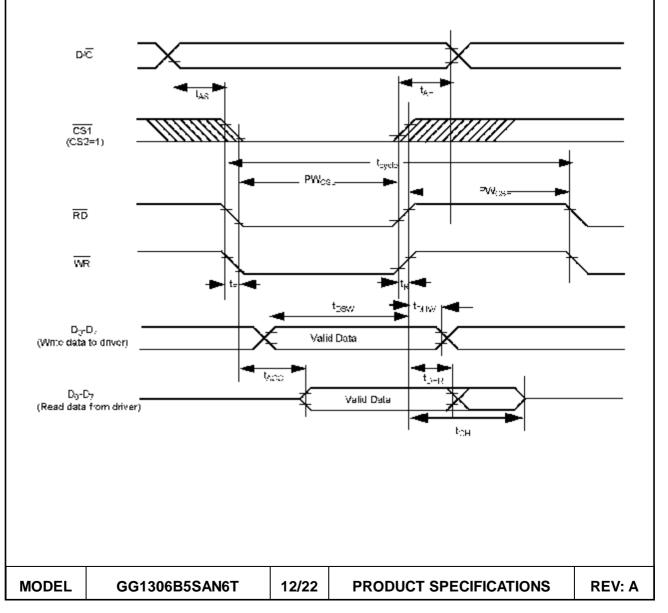

#### **8.TIMING CHARACTERISTICS**

| Symbol             | Parameter                                                                   | Min       | Тур | Max | Unit             |

|--------------------|-----------------------------------------------------------------------------|-----------|-----|-----|------------------|

| t <sub>oyolo</sub> | Clock Cycle Time                                                            | 300       |     |     | ns               |

| t <sub>AS</sub>    | Address Setup Time                                                          | С         | -   | -   | ПБ               |

| t <sub>A</sub>     | Address Hold Time                                                           | с         | -   | -   | ns               |

| $t_{\rm ASW}$      | Write Data Setup Time                                                       | 40        | -   | -   | ns               |

| t <sub>uerw</sub>  | Write Data Hold Time                                                        | 15        | -   | -   | nв               |

| <b>t</b> ru a      | Read Data Hold Time                                                         | 20        |     |     | ns               |

| t <sub>on</sub>    | Output Disable Time                                                         | -         | -   | 70  | пв               |

| teoc               | Access Time                                                                 | -         | -   | 140 | ns               |

| PW <sub>C3</sub>   | Chip Select Low Pulse Width (read)<br>Chip Select Low Pulse Width (write)   | 120<br>60 | -   | -   | п <b>5</b><br>nв |

| PWcsti             | Chip Select High Pulse Wicth (read)<br>Chip Select High Pulse Wicth (writz) | 60<br>60  | -   | -   | ns<br>ns         |

| t <sub>R</sub>     | Rise Time                                                                   | -         | -   | 15  | ns               |

| t⊨                 | Fall Time                                                                   | -         | -   | 15  | ns               |

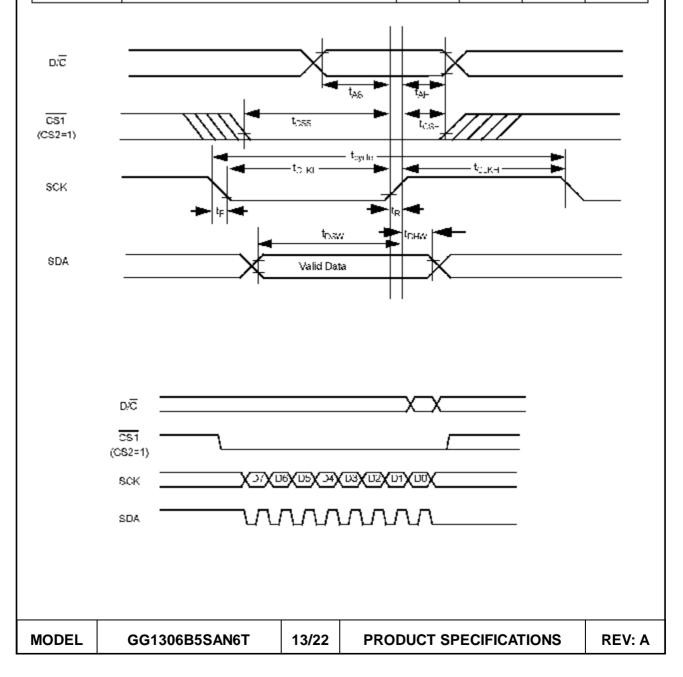

## 8.TIMING CHARACTERISTICS (Continued)

| Symbol               | Parameter                                                                   | Min       | Тур | Мал | Unit     |

|----------------------|-----------------------------------------------------------------------------|-----------|-----|-----|----------|

| L <sub>cyple</sub>   | Gluck Cycle Time                                                            | 300       | -   | -   | ពន       |

| $L_{A33}$            | Address Setup Time                                                          | C         | -   | -   | ពន       |

| t <sub>AH</sub>      | Address Hold Time                                                           | ) D       | -   | -   | ns       |

| t <sub>DBW</sub>     | Write Data Setup Time                                                       | 40        | -   | -   | ាន       |

| $t_{\Gamma(-M)}$     | Write Data Hold Time                                                        | 15        | -   | -   | ាន       |

| t <sub>D-R</sub>     | Read Data Hold Time                                                         | 20        | -   | -   | ns       |

| to⊣                  | Cutput Disable Time                                                         | -         | -   | 70  | ns       |

| $t_{A(\mathcal{G})}$ | Access Time                                                                 | -         | -   | 140 | ns       |

| PW <sub>CS-</sub>    | Chip Select Low Pulse Width (read)<br>Chip Select Low Pulse Width (write)   | 120<br>60 | -   | -   | ns<br>na |

| PW <sub>(23</sub>    | Chip Select High Pulse Width (read)<br>Chip Select High Pulse Width (write) | 60<br>60  | -   | -   | ns<br>ns |

| t.,                  | Rise Time                                                                   | -         | -   | 15  | ne       |

| t <sub>r</sub>       | Fall Time                                                                   |           |     | 15  | ns       |

## 8.TIMING CHARACTERISTICS (Continued)

| Symbol                | Parameter                                        | Min | Тур | Max | Unit |

|-----------------------|--------------------------------------------------|-----|-----|-----|------|

| 1 <sub>oyotes</sub>   | Clock Cycle Time                                 | 250 |     |     | ns   |

| $t_{AS}$              | Acdress Setup Time                               | 150 | -   | -   | ль   |

| t <sub>A 1</sub>      | Address Hold Time                                | 150 |     |     | ns   |

| t <sub>OBS</sub>      | Chip Select Setup Time (for D, input)            | 120 | -   | -   | ль   |

| t <sub>esti</sub>     | Chip Select Hold Time (for D <sub>0</sub> input) | 60  |     |     | ns   |

| t <sub>DBW</sub>      | Write Data Setup Time                            | 100 | -   | -   | пь   |

| t <sub>M IW</sub>     | Write Data Hold Time                             | 100 |     |     | ns   |

| $t_{\rm OLK_{\rm c}}$ | Clock Low Time                                   | 100 | -   | -   | ль   |

| t <sub>a ku</sub>     | Clock High Time                                  | 100 |     |     | ns   |

| ЭR                    | Rise Time                                        | -   | -   | 15  | ль   |

| tΓ                    | Fall Time                                        |     |     | 15  | ns   |

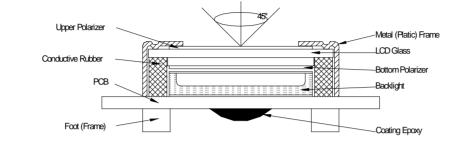

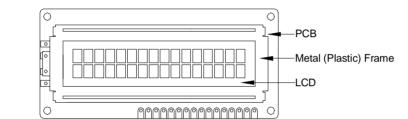

#### 9. QUALITY SPECIFICATION

- 9 1. LCM Appearance and Electric inspection Condition

- 1. Inspection will be done by placing LCM 30cm away from inspector's eyeballs under normal illumination.

2. View Angle: with in 45° around perpendicular line.

## 9 - 2. Definition

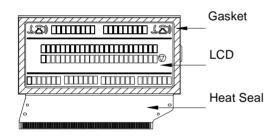

#### 2. Heat Seal

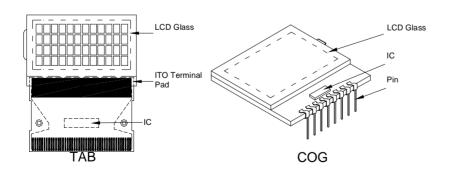

## 3. TAB and COG

| MODEL | GG1306B5SAN6T | 14/22 | PRODUCT SPECIFICATIONS | REV: A |

|-------|---------------|-------|------------------------|--------|

**Display the World**

## 9. QUALITY SPECIFICATION (Continued)

- 9-3. Sampling Plan and Acceptance

- 1.Sampling Plan

MIL - STD - 105E (  $\parallel$  ) ordinary single inspection is used.

2.Acceptance

| Major defect: | AQL = 0.25% |

|---------------|-------------|

| Minor defect: | AQL = 0.65% |

#### 9-4. Criteria

#### 1.COB

| Defect | Inspection Item Inspection Standards |                                                                            |        |  |  |

|--------|--------------------------------------|----------------------------------------------------------------------------|--------|--|--|

| Major  | PCB copper flakes peeling off        | Any copper flake in viewing Area should be greater than 1.0mm <sup>2</sup> | Reject |  |  |

| Major  | Height of coating epoxy              | Exceed the dimension of drawing                                            | Reject |  |  |

| Major  | Void or hole of coating epoxy        | Expose bonding wire or IC                                                  | Reject |  |  |

| Major  | PCB cutting defect                   | Exceed the dimension of drawing                                            | Reject |  |  |

#### 2.SMT

| Defect | Inspection Item                                                                                                                                                                                   |                      | Inspection Standa                  | irds   |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------|--------|

| Minor  | Component marking not re                                                                                                                                                                          | eadable              |                                    | Reject |

| Minor  | Component height                                                                                                                                                                                  |                      | Exceed the dimension<br>Of drawing | Reject |

| Major  | Component solder defect (miss<br>wrong component or wrong original                                                                                                                                |                      |                                    | Reject |

| Minor  | Component position s<br>component solderi<br>X<br>$\rightarrow$ $\downarrow$ | X < 3/4Z<br>Y > 1/3D | Reject<br>Reject                   |        |

| Minor  | Component tilt                                                                                                                                                                                    | onent<br>↓<br>↑      | Y > 1/3D                           | Reject |

| Minor  |                                                                                                                                                                                                   | nt<br>PAD<br>— РСВ   | <i>θ</i> ≤ 20°                     | Reject |

| DEL    | GG1306B5SAN6T 15/22                                                                                                                                                                               | PRODU                |                                    | REV    |

**Display the World**

## 9. QUALITY SECIFICATION (Continued)

- 9-4. Criteria (Continued)

- 3. Metal (Plastic) Frame

| Defect | Inspection Item          | h                                                                                                                                                                | nspection Standa                             | rds                             |  |  |  |

|--------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------|--|--|--|

| Major  | Crack / breakage         | Any                                                                                                                                                              | /where                                       | Reject                          |  |  |  |

|        |                          | W                                                                                                                                                                | L                                            | Acceptable of<br>Scratch        |  |  |  |

|        |                          | w<0.1mm                                                                                                                                                          | Any                                          | Ignore                          |  |  |  |

|        |                          | 0.1 <u>&lt;</u> w<0.2mm                                                                                                                                          | L <u>&lt;</u> 5.0mm                          | 2                               |  |  |  |

| Minor  | Frame Scratch            | 0.2 <u>&lt;</u> w<0.3mm                                                                                                                                          | L <u>&lt;</u> 3.0mm                          | 1                               |  |  |  |

| -      |                          | w <u>&gt;</u> 0.3mm                                                                                                                                              | Any                                          | 0                               |  |  |  |

|        |                          | Note : 1. Above criteria applicable to scratch lines<br>with distance greater than 5mm.<br>2. Scratch on the back side of frame (not<br>visible) can be ignored. |                                              |                                 |  |  |  |

|        |                          |                                                                                                                                                                  |                                              | Acceptable of<br>Dents / Pricks |  |  |  |

|        |                          | Φ <u>&lt;</u>                                                                                                                                                    | 2                                            |                                 |  |  |  |

|        | Frame Dent, Prick        | 1.0<⊕ <u>&lt;</u> 1.5mm                                                                                                                                          |                                              | 1                               |  |  |  |

| Minor  | $\Phi = \frac{L + W}{2}$ | 1.5                                                                                                                                                              | $nm < \Phi$                                  | 0                               |  |  |  |

|        | 2                        | / pricks with dis                                                                                                                                                | to any two dents<br>5mm<br>side of frame (no |                                 |  |  |  |

| Minor  | Frame Deformation        | Excee                                                                                                                                                            | d the dimension of                           | drawing                         |  |  |  |

| Minor  | Metal Frame Oxidation    |                                                                                                                                                                  | Any rust                                     |                                 |  |  |  |

## 4. Flexible Film Connector (FFC)

| Defect | Inspection Item               | Inspection Standa                                | rds        |  |  |

|--------|-------------------------------|--------------------------------------------------|------------|--|--|

| Minor  | Tilted soldering              | Within the angle +5°                             | Acceptable |  |  |

| Minor  | Uneven solder joint /bump     |                                                  | Reject     |  |  |

| Minor  | Hole $\Phi = \frac{L + W}{2}$ | Expose the conductive line                       | Reject     |  |  |

| WILLOU | Hole $\Psi = \frac{1}{2}$     | Hole $\Phi = \frac{1}{2}$ $\Phi > 1.0 \text{mm}$ |            |  |  |

| Minor  | Alipor Position shift         | Y > 1/3D                                         | Reject     |  |  |

| WIITO  |                               | X > 1/2Z                                         | Reject     |  |  |

| MODEL | GG1306B5SAN6T | 16/22 | PRODUCT SPECIFICATIONS | REV: A |

|-------|---------------|-------|------------------------|--------|

|-------|---------------|-------|------------------------|--------|

#### 9. QUALITY SPECIFICATION (Continued)

9-4. Criteria (Continued)

5. Screw

| Defect | Inspection Item      | Inspection Standards             |        |  |  |

|--------|----------------------|----------------------------------|--------|--|--|

| Major  | Screw missing/loosen |                                  | Reject |  |  |

| Minor  | Screw oxidation      | Any rust                         | Reject |  |  |

| Minor  | Screw deformation    | Difficult to accept screw driver | Reject |  |  |

6. Heatseal 💉 TCP 💉 FPC

| Defect | Inspection Item                                                                                   | Inspection Standards        |        |

|--------|---------------------------------------------------------------------------------------------------|-----------------------------|--------|

| Major  | Scratch expose conductive layer                                                                   |                             | Reject |

| Minor  | HS Hole $\Phi = \frac{L + W}{2}$                                                                  | $\Phi$ > 0.5mm              | Reject |

| Major  | Adhesion strength                                                                                 | Less than the specification | Reject |

| Minor  | Position shift<br>$y \xrightarrow{-\psi} \xrightarrow{-\psi} \xrightarrow{-\psi} \xrightarrow{D}$ | Y > 1/3D                    | Reject |

|        |                                                                                                   | X > 1/2Z                    | Reject |

| Major  | Conductive line break                                                                             |                             | Reject |

7. LED Backing Protective Film and Others

| Defect | Inspection Item      | Inspection Standards                                                                                            |        |  |  |

|--------|----------------------|-----------------------------------------------------------------------------------------------------------------|--------|--|--|

|        |                      | Acceptable number of units                                                                                      |        |  |  |

|        |                      | ⊕ <u>&lt;</u> 0.10mm                                                                                            | Ignore |  |  |

|        |                      | 0.10<⊕ <u>&lt;</u> 0.15mm                                                                                       | 2      |  |  |

| Minor  | LED dirty, prick     | 0.15<⊕ <u>&lt;</u> 0.2mm                                                                                        | 1      |  |  |

|        |                      | ⊕>0.2mm                                                                                                         | 0      |  |  |

|        |                      | The distance between any two spots should be $\geq$ 5mm Any spot/dot/void outside of viewing area is acceptable |        |  |  |

| Minor  | Protective film tilt | Not fully cover LCD Re                                                                                          |        |  |  |

| Major  | COG coating          | Not fully cover ITO circuit                                                                                     | Reject |  |  |

## 8. Electric Inspection

| Defect | Inspection Item | Inspection Standards |        |

|--------|-----------------|----------------------|--------|

| Major  | Short           |                      | Reject |

| Major  | Open            |                      | Reject |

| MODEL | GG1306B5SAN6T | 17/22 | PRODUCT SPECIFICATIONS | REV: A |

|-------|---------------|-------|------------------------|--------|

|-------|---------------|-------|------------------------|--------|

## 9. QUALITY SPECIFICATION (Continued)

9-4. Criteria (Continued)

9. Inspection Specification of LCD

| Defect | insp                          | ect Item                                                                          |               |             | I                                             | Ins             | pection                              | S                | standard                                | S                |                  |

|--------|-------------------------------|-----------------------------------------------------------------------------------|---------------|-------------|-----------------------------------------------|-----------------|--------------------------------------|------------------|-----------------------------------------|------------------|------------------|

|        |                               | * Glass Scrat                                                                     | ch            | W           |                                               | W <u>&lt;</u>   | 0.03                                 | 0.               | 03 <w<u>&lt;0.0</w<u>                   | 5 \              | N>0.05           |

|        |                               | <ul> <li>* Glass Scrat</li> <li>* Polarizer Sc</li> </ul>                         |               | L           |                                               | L               | <5                                   |                  | L<3                                     |                  | Any              |

| Minor  | Linear Defect                 | <ul> <li>Fiber and Li</li> </ul>                                                  |               | ACC.        |                                               |                 | 1                                    |                  | 1                                       |                  | Reject           |

|        |                               | material                                                                          | inear         | NO.         | 1. 1. 11                                      |                 |                                      | A/               |                                         |                  | -                |

|        |                               |                                                                                   |               | Note        |                                               |                 | -                                    |                  | he width of                             |                  |                  |

|        |                               | * Foreign mat                                                                     |               | Φ           | 00                                            |                 | 0.1<⊕ <u>&lt;</u>                    | 0.15             | 0.15<⊕ <u>&lt;</u> 0                    | .2               | <b>⊕&gt;0.2</b>  |

|        | Black Spot and                | between glass                                                                     |               | ACC.<br>NO. | 3EA<br>100m                                   | $m^2$           | 2                                    |                  | 1                                       |                  | 0                |

| Minor  | Polarizer<br>Pricked          | and glass<br>* Polarizer ho<br>protuberance h<br>external force                   | ole or        | Note        | ⊕ is t                                        | he a            | -                                    |                  | er of the de<br>fects > 10n             |                  |                  |

|        |                               | * Unobvious                                                                       |               | Φ           |                                               | Φ <u>&lt;</u> ( | 0.3                                  | 0.3              | <Φ <u>&lt;</u> 0.5                      | 0.               | . <b>5</b> <Φ    |

|        | White Spot                    | transparant for<br>material betwe                                                 | en            | ACC.<br>NO. |                                               |                 | 00mm <sup>2</sup>                    |                  | 1                                       |                  | 0                |

| Minor  | and Bubble in polarizer       | glass and glas<br>glass and pola<br>* Air protuber<br>between polari<br>and glass | rizer<br>ance | Note        |                                               |                 | •                                    |                  | er of the de<br>fects > 10n             |                  |                  |

|        |                               |                                                                                   | Ìŧ            | Φ           | ⊕ <u>&lt;</u> 0.                              |                 | 0.10<⊕ <u>-</u>                      | <u>&lt;</u> 0.20 | 0.20<Φ <u>&lt;</u>                      | <u>&lt;</u> 0.25 | <b>⊕&gt;0.25</b> |

|        |                               |                                                                                   | ]             | ACC.<br>NO. | 3EA<br>100m                                   | /<br>m²         | 2                                    |                  | 1                                       |                  | 0                |

| Minor  | Segment<br>Defect             |                                                                                   | J             |             | W is m                                        | nore            | than 1/2                             | segm             | ent width                               |                  | Reject           |

|        |                               |                                                                                   |               | Note        | $\Phi = \frac{L + W}{2}$ Distance between two |                 |                                      |                  | fact is 10m                             |                  |                  |

|        |                               |                                                                                   | ]             |             |                                               |                 |                                      |                  | 1                                       |                  | I                |

|        |                               |                                                                                   |               | Φ           | Φ <u>&lt;</u> 0.                              | 10              | 0.10<⊕ <u>·</u>                      |                  | 0.20<⊕ <u>&lt;</u>                      |                  | <b>⊕&gt;0.25</b> |

| Minor  | Protuberant<br>Segment        | w t                                                                               |               | W           | Glue                                          |                 | W <u>&lt;</u> 1/2<br>W <u>&lt;</u> 0 |                  | W <u>&lt;</u> 1/2<br>W <u>&lt;</u> 0.   |                  | Ignore           |

|        |                               | $\Phi = (L + W) / 2$                                                              | 2             | ACC.<br>NO. | 3EA<br>100m                                   | /<br>m²         | 2                                    |                  | 1                                       |                  | 0                |

|        |                               |                                                                                   |               | 1. Seg      | ment                                          |                 |                                      |                  |                                         |                  |                  |

|        |                               |                                                                                   |               | E           | 3                                             | В <u>&lt;</u>   | 0.4mm                                | 0.4<             | 3 <u>&lt;</u> 1.0mm                     | B>′              | 1.0mm            |

|        | Assembly                      |                                                                                   |               | B-          | A                                             | B-/             | A<1/2B                               | B-               | A<0.2                                   | B-A              | <0.25            |

| Minor  | Mis-alignment                 |                                                                                   | A             | Juc         | lge                                           | Acc             | ceptable                             | Acc              | ceptable                                | Acc              | eptable          |

|        |                               |                                                                                   |               | 2. Dot      | Matrix                                        |                 |                                      |                  |                                         |                  |                  |

|        |                               |                                                                                   |               | Defo        | ormatio                                       | n>2             | 0                                    |                  |                                         |                  | Reject           |

| Minor  | Stain on LCD<br>Panel Surface |                                                                                   |               | oras        | similar                                       | one             | e. Otherw                            | /ise, j          | ed lightly w<br>udged acc<br>Vhite Spot | cordin           |                  |

|        |                               |                                                                                   |               |             |                                               |                 |                                      |                  |                                         |                  |                  |

|        |                               |                                                                                   |               |             |                                               |                 |                                      |                  |                                         |                  |                  |

| NO. | ltem                       | Condition                                             | Criterion                                                                                                                |  |

|-----|----------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| 1   | High Temperature Operating | 70℃, 240Hrs                                           | No defect in cosmetic<br>and operational<br>function allowable.<br>Total current<br>Consumption should                   |  |

| 2   | Low Temperature Operating  | -20℃, 240Hrs                                          |                                                                                                                          |  |

| 3   | High Humidity              | 80℃, 90%RH, 96Hrs                                     |                                                                                                                          |  |

| 4   | High Temperature Storage   | <b>75</b> ℃, 240Hrs                                   |                                                                                                                          |  |

| 5   | Low Temperature Storage    | -25℃, 240Hrs                                          |                                                                                                                          |  |

| 6   | Vibration                  | Random wave                                           |                                                                                                                          |  |

|     |                            | 10 ~ 100Hz                                            |                                                                                                                          |  |

|     |                            | Acceleration: 2g                                      | be below double of initial value.                                                                                        |  |

|     |                            | 2 Hrs per direction(X,Y,Z)                            | _                                                                                                                        |  |

| 7   | Thermal Shock              | -30℃ to 25℃ to 80℃                                    |                                                                                                                          |  |

|     |                            | (60Min) (5Min) (60Min)                                |                                                                                                                          |  |

|     |                            | 10Cycles                                              |                                                                                                                          |  |

| 8   | ESD Testing                | Contract Discharge Voltage:<br>+1 ~ 5kV and -1 ~ -5kV | <sup>2:</sup> There will be<br>discharged ten times<br>at every discharging<br>voltage cycle. The<br>voltage gap is 1kV. |  |

|     |                            | Air Discharge Voltage:<br>+1 ~ 8kV and –1 ~ -8kV      |                                                                                                                          |  |

# Note: 1) Above conditions are suitable for GOLDENTEK standard products.2) For restrict products, the test conditions listed as above must be revised.

| MODEL | GG1306B5SAN6T | 19/22 | PRODUCT SPECIFICATIONS | REV: A |

|-------|---------------|-------|------------------------|--------|

|-------|---------------|-------|------------------------|--------|

#### **11. HANDLING PRECAUTION**

(1) Mounting Method

The panel of the LCD Module consists of two thin glass plates with polarizers which easily get damaged since the Module is fixed by utilizing fitting holes in the printed circuit board. Extreme care should be taken when handling the LCD Modules.

(2) Caution of LCD handling & cleaning

When cleaning the display surface, use soft cloth with solvent (recommended below) and wipe lightly.

- Isopropyl alcohol

- Ethyl alcohol

- Trichlorotrifloroethane

Do not wipe the display surface with dry or hard materials that will damage the polarizer surface.

Do not use the following solvent:

- Water

- Ketone

- Aromatics

- (3) Caution against static charge

The LCD Module use C-MOS LSI drivers, so we recommend that you connect any unused input terminal to VDD or VSS, do not input any signals before power is turned on. And ground your body, Work/assembly table. And assembly equipment to protect against static electricity.

(4) Packaging

- Modules use LCD elements, and must be treated as such. Avoid intense shock and falls from a height.

- To prevent modules from degradation. Do not operate or store them exposed directly to sunshine or high temperature/humidity.

- (5) Caution for operation

- It is indispensable to drive LCD's within the specified voltage limit since the higher voltage than the limit shorten LCD life. An electrochemical reaction due to direct current causes LCD deterioration, Avoid the use of direct current drive.

| MODEL GG1306B5SAN6T 20/22 PRODUCT SPECIFICATION | ONS REV: A |

|-------------------------------------------------|------------|

|-------------------------------------------------|------------|

#### **11. HANDLING PRECAUTION (Continued)**

- Response time will be extremely delayed at lower temperature than the operating temperature range and on the other hand at higher temperature LCD's show dark color in them.

However those phenomena do not mean malfunction or out of order with LCD's. Which will come back in the specified operating temperature range.