### **Preliminary**

**SP7655**

# Wide Input Voltage Range 8A, 300kHz, Buck Regulator

#### **FEATURES**

- 2.5V to 28V Step Down Achieved Using Dual Input

- Output Voltage down to 0.8V

- 8A Output Capability

- Built in Low R<sub>DSON</sub> Power Switches (15 mΩ typ)

- Highly Integrated Design, Minimal Components

- 300 kHz Fixed Frequency Operation

- UVLO Detects Both V<sub>CC</sub> and V<sub>IN</sub>

- Over Temperature Protection

- Short Circuit Protection with Auto-Restart

- Wide BW Amp Allows Type II or III Compensation

- Programmable Soft Start

- Fast Transient Response

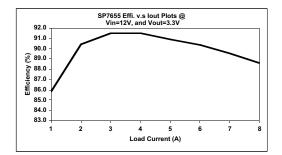

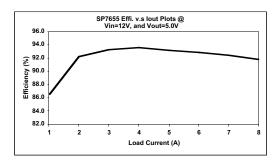

- High Efficiency: Greater than 95% Possible

- Asynchronous Start-Up into a Pre-Charged Output

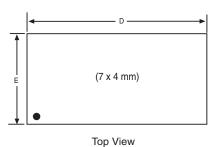

- Small 7mm x 4mm DFN Package

Now Available in Lead Free Packaging

#### DESCRIPTION

The SP7655 is a synchronous step-down switching regulator optimized for high efficiency. The part is designed to be especially attractive for dual supply, 12V or 24V distributed power systems step down with 5V used to power the controller. This lower  $V_{CC}$  voltage minimizes power dissipation in the part and is used to drive the top switch. The SP7655 is designed to provide a fully integrated buck regulator solution using a fixed 300kHz frequency, PWM voltage mode architecture. Protection features include UVLO, thermal shutdown and output short circuit protection. The SP7655 is available in the space saving DFN package.

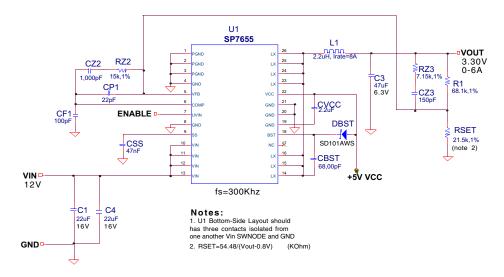

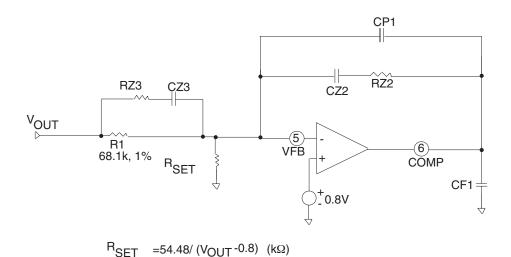

#### TYPICAL APPLICATION CIRCUIT

#### **ABSOLUTE MAXIMUM RATINGS**

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| V <sub>CC</sub>  | 7\          |

|------------------|-------------|

| V <sub>IN</sub>  | 30\         |

| l <sub>1</sub> x | 10 <i>A</i> |

| BST              |             |

| BST-SWN          | 0.3V to 7\  |

| SWN              | -1V to 30\  |

| GHGH-SWN               |                                |

|------------------------|--------------------------------|

| All other pins         | -0.3V to V <sub>CC</sub> +0.3V |

| Storage Temperature    |                                |

| Power Dissipation      | Internally Limited via OTP     |

| ESD Rating             | 2kV HBM                        |

| Thermal Resistance OJC | 5°C/W                          |

#### **ELECTRICAL SPECIFICATIONS**

Unless otherwise specified:  $-40^{\circ}\text{C} < T_{AMB} < 85^{\circ}\text{C}$ ,  $-40^{\circ}\text{C} < T_{J} < 125^{\circ}\text{C}$ ,  $4.5\text{V} < \text{V}_{CC} < 5.5\text{V}$ , 3V < Vin < 28V, BST=LX+5V, LX = GND = ZeroV, UVIN = 3.0V,  $CV_{CC} = 1\mu\text{F}$ ,  $C_{COMP} = 0.1\mu\text{F}$ ,  $C_{SS} = 50\text{nF}$ , Typical measured at  $V_{CC} = 5\text{V}$ . The  $\blacklozenge$  denotes the specifications which apply over the full temperature range, unless otherwise specified.

| PARAMETER                                              | MIN.  | TYP.  | MAX.  | UNITS |   | CONDITIONS                                                     |

|--------------------------------------------------------|-------|-------|-------|-------|---|----------------------------------------------------------------|

| QUIESCENT CURRENT                                      |       |       |       |       |   |                                                                |

| V <sub>cc</sub> Supply Current (No switching)          |       | 1.5   | 3     | mA    |   | V <sub>FB</sub> =0.9V                                          |

| V <sub>CC</sub> Supply Current (switching)             |       | 6     | 9     | mA    | * |                                                                |

| BST Supply Current (No switching)                      |       | 0.2   | 0.4   | mA    |   | V <sub>FB</sub> =0.9V                                          |

| BST Supply Current (switching)                         |       | 5     | 8     | mA    | * |                                                                |

| PROTECTION: UVLO                                       | •     | •     |       |       | - |                                                                |

| V <sub>cc</sub> UVLO Start Threshold                   | 4.00  | 4.25  | 4.5   | V     |   |                                                                |

| V <sub>cc</sub> UVLO Hysteresis                        | 100   | 200   | 300   | mV    |   |                                                                |

| UVIN Start Threshold                                   | 2.3   | 2.5   | 2.65  | V     | * |                                                                |

| UVIN Hysteresis                                        | 200   | 300   | 400   | mV    |   |                                                                |

| UVIN Input Current                                     |       |       | 1     | μΑ    |   | UVIN =3.0V                                                     |

| ERROR AMPLIFIER REFERENCE                              | -     |       |       |       |   |                                                                |

| Error Amplifier Reference                              | 0.792 | 0.800 | 0.808 | V     |   | 2X Gain Config., Measure<br>VFB; V <sub>cc</sub> =5 V, T= 25°C |

| Error Amplifier Reference<br>Over Line and Temperature | 0.788 | 0.800 | 0.812 | V     | * |                                                                |

| Error Amplifier Transconductance                       |       | 6     |       | mA/V  |   |                                                                |

| Error Amplifier Gain                                   |       | 60    |       | dB    |   | No Load                                                        |

| COMP Sink Current                                      |       | 150   |       | μΑ    |   | V <sub>FB</sub> =0.9V, COMP=0.9V                               |

| COMP Source Current                                    |       | 150   |       | μΑ    |   | V <sub>FB</sub> =0.7V, COMP=22V                                |

| V <sub>FB</sub> Input Bias Current                     |       | 50    | 200   | nA    |   | V <sub>FB</sub> =0.8V                                          |

| Internal Pole                                          |       | 4     |       | MHz   |   |                                                                |

| COMP Clamp                                             |       | 2.5   |       | V     |   | V <sub>FB</sub> =0.7V, TA=25°C                                 |

| COMP Clamp Temp. Coefficient                           |       | -2    |       | mV/ºC |   |                                                                |

Unless otherwise specified: -40°C <  $T_{AMB}$  < 85°C, -40°C < Tj< 125°C, 4.5V <  $V_{CC}$  < 5.5V, 3V < Vin< 28V, BST=LX + 5V, LX = GND = ZeroV, UVIN = 3.0V, CV<sub>CC</sub> = 1 $\mu$ F, C<sub>COMP</sub> = 0.1 $\mu$ F, C<sub>SS</sub> = 50nF, Typical measured at V<sub>CC</sub> = 5V.

The ♦ denotes the specifications which apply over the full temperature range, unless otherwise specified.

| PARAMETER                                            | MIN. | TYP. | MAX. | UNITS      |   | CONDITIONS                                                   |

|------------------------------------------------------|------|------|------|------------|---|--------------------------------------------------------------|

| CONTROL LOOP: PWM COMPARATOR, RAMP & LOOP DELAY PATH |      |      |      |            |   |                                                              |

| Ramp Amplitude                                       | 0.92 | 1.1  | 1.28 | V          |   |                                                              |

| RAMP Offset                                          |      | 1.1  |      | V          |   | T <sub>A</sub> = 25℃, RAMP COMP<br>until GH starts Switching |

| RAMP Offset Temp. Coefficient                        |      | -2   |      | mV/ºC      |   |                                                              |

| GH Minimum Pulse Width                               |      | 90   | 180  | ns         | • |                                                              |

| Maximum Controllable Duty Ratio                      | 92   | 97   |      | %          |   | Maximum Duty Ratio<br>Measured just before<br>pulsing begins |

| Maximum Duty Ratio                                   | 100  |      |      | %          |   | Valid for 20 cycles                                          |

| Internal Oscillator Ratio                            | 420  | 600  | 720  | kHz        | • |                                                              |

| TIMERS: SOFTSTART                                    |      |      |      |            |   |                                                              |

| SS Charge Current:                                   |      | 10   |      | μΑ         |   |                                                              |

| SS Discharge Current:                                | 1    |      |      | mA         | • | Fault Present, SS = 0.2V                                     |

| PROTECTION: Short Circuit & The                      | rmal |      |      |            | • |                                                              |

| Short Circuit Threshold Voltage                      | 0.2  | 0.25 | 0.3  | V          | * | Measured V <sub>REF</sub> (0.8V) - V <sub>FB</sub>           |

| Hiccup Timeout                                       |      | 200  |      | ms         |   | V <sub>FB</sub> =0.5V                                        |

| Number of Allowable Clock Cycles at 100% Duty Cycle  |      | 20   |      | Cycles     |   |                                                              |

| Minimum GL Pulse After 20 Cycles                     |      | 0.5  |      | Cycles     |   | V <sub>FB</sub> =0.7V                                        |

| Thermal Shutdown Temperature                         |      | 145  |      | °C         |   | V <sub>FB</sub> =0.7V                                        |

| Thermal Recovery Temperature                         |      | 135  |      | <b>°</b> C |   |                                                              |

| Thermal Hysteresis                                   |      | 10   |      | <b>°</b> C |   |                                                              |

| OUTPUT: POWER STAGE                                  |      |      |      |            |   |                                                              |

| High Side R <sub>DSON</sub>                          |      | 15   |      | m          |   | $V_{CC} = 5V ; I_{OUT} = 6A$<br>$T_{AMB} = 25^{\circ}C$      |

| Synchronous FET R <sub>DSON</sub>                    |      | 15   |      | m          |   | $V_{CC} = 5V ; I_{OUT} = 6A$<br>$T_{AMB} = 25^{\circ}C$      |

| Maximum Output Current                               | 6    |      |      | А          |   |                                                              |

| Pin #       | Pin Name        | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-3         | $P_{GND}$       | Ground connection for the synchronous rectifier                                                                                                                                                                                                                                                                                                                                                    |

| 4,8,19-21   | GND             | Ground Pin. The control circuitry of the IC and lower power driver are referenced to this pin. Return separately from other ground traces to the (-) terminal of Cout.                                                                                                                                                                                                                             |

| 5           | $V_{FB}$        | Feedback Voltage and Short Circuit Detection pin. It is the inverting input of the Error Amplifier and serves as the output voltage feedback point for the Buck Converter. The output voltage is sensed and can be adjusted through an external resistor divider. Whenever $V_{\rm FB}$ drops 0.25V below the positive reference, a short circuit fault is detected and the IC enters hiccup mode. |

| 6           | COMP            | Output of the Error Amplifier. It is internally connected to the inverting input of the PWM comparator. An optimal filter combination is chosen and connected to this pin and either ground or $V_{\rm FB}$ to stabilize the voltage mode loop.                                                                                                                                                    |

| 7           | UVIN            | UVLO input for Vin voltage. Connect a resistor divider between $\rm V_{IN}$ and $\rm UV_{IN}$ to set minimum operating voltage                                                                                                                                                                                                                                                                     |

| 9           | SS              | Soft Start. Connect an external capacitor between SS and GND to set the soft start rate based on the 10µA source current. The SS pin is held low via a 1mA (min) current during all fault conditions.                                                                                                                                                                                              |

| 10-13       | V <sub>IN</sub> | Input connection to the high side N-channel MOSFET. Place a decoupling capacitor between this pin and PGND.                                                                                                                                                                                                                                                                                        |

| 14-16,23-26 | LX              | Connect an inductor between this pin and V <sub>OUT</sub>                                                                                                                                                                                                                                                                                                                                          |

| 17          | NC              | No Connect                                                                                                                                                                                                                                                                                                                                                                                         |

#### THEORY OF OPERATION

#### **General Overview**

The SP7655 is a fixed frequency, voltage mode, synchronous PWM regulator optimized for high efficiency. The part has been designed to be especially attractive for high voltage applications utilizing 5V to power the controller and 2.5V to 28V for step down conversion.

The heart of the SP7655 is a wide bandwidth transconductance amplifier designed to accommodate Type II and Type III compensation schemes. A precision 0.8V reference, present on the positive terminal of the error amplifier permits the programming of the output voltage down to 0.8V via the V<sub>FB</sub> pin. The output of the error amplifier, COMP, compared to a 1.1V peak-to-peak ramp is responsible for trailing edge PWM control. This voltage ramp, and PWM control logic are governed by the internal oscillator that accurately sets the PWM frequency to 300kHz.

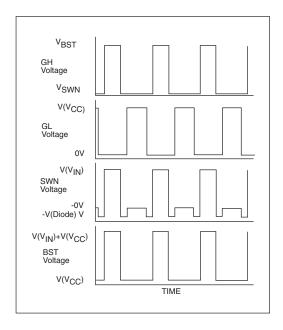

The SP7655 contains two unique control features that are very powerful in distributed applications. First, asynchronous driver control is enabled during start up, to prohibit the low side switch from pulling down the output until the high side switch has attempted to turn on. Second, a 100% duty cycle timeout ensures that the low side switch is periodically enhanced during extended periods at 100% duty cycle. This guarantees the synchronized refreshing of the BST capacitor during very large duty ratios.

The SP7655 also contains a number of valuable protection features. Programmable  $V_{\rm IN}$  UVLO allows the user to set the exact value at which the conversion voltage can safely begin down conversion, and an internal  $V_{\rm CC}$  UVLO which ensures that the controller itself has enough voltage to properly operate. Other protection fea-

tures include thermal shutdown and short-circuit detection. In the event that either a thermal, short-circuit, or UVLO fault is detected, the SP7655 is forced into an idle state where the output drivers are held off for a finite period before a restart is attempted.

#### Soft Start

"Soft Start" is achieved when a power converter ramps up the output voltage while controlling the magnitude of the input supply source current. In a modern step down converter, ramping up the positive terminal of the error amplifier controls soft start. As a result, excess source current can be defined as the current required to charge the output capacitor.

$$I_{VIN} = C_{OUT} * (DV_{OUT} / DT_{SOFT-START})$$

The SP7655 provides the user with the option to program the soft start rate by tying a capacitor from the SS pin to GND. The selection of this capacitor is based on the 10uA pull up current present at the SS pin and the 0.8V reference voltage. Therefore, the excess source can be redefined as:

$$IV_{IN} = C_{OUT} * (DV_{OUT} *10\mu A / (C_{SS} * 0.8V)$$

#### **Under Voltage Lock Out (UVLO)**

The SP7655 contains two separate UVLO comparators to monitor the bias ( $V_{CC}$ ) and conversion ( $V_{IN}$ ) voltages independently. The  $V_{CC}$  UVLO threshold is internally set to 4.25V, whereas the  $V_{IN}$  UVLO threshold is programmable through the UVIN pin. When the UVIN pin is greater than 2.5V, the SP7655 is permitted to start up pending the removal of all other faults. Both the  $V_{CC}$  and  $V_{IN}$  UVLO comparators have been designed with hysteresis to prevent noise from resetting a fault.

## Thermal and Short-Circuit Protection

Because the SP7655 is designed to drive large output current, there is a chance that the power converter will become too hot. Therefore, an internal thermal shutdown (145°C) has been included to prevent the IC from malfunctioning at extreme temperatures.

A short-circuit detection comparator has also been included in the SP7655 to protect against an accidental short at the output of the power converter. This comparator constantly monitors the positive and negative terminals of the error amplifier, and if the  $V_{FB}$  pin falls more than 250mV (typical) below the positive reference, a short-circuit fault is set. Because the SS pin overrides the internal 0.8V reference during soft start, the SP7655 is capable of detecting short-circuit faults throughout the duration of soft start as well as in regular operation.

#### **Handling of Faults:**

Upon the detection of power (UVLO), thermal, or short-circuit faults, the SP7655 is forced into an idle state where the SS and COMP pins are pulled low and both switches are held off. In the event of UVLO fault, the SP7655 remains in this idle state until the UVLO fault is removed. Upon the detection of a thermal or short-circuit fault, an internal 200ms timer is activated. In the event of a short-circuit fault, a re-start is attempted immediately after the 200ms timeout expires. Whereas, when a thermal fault is detected the 200ms delay continuously recycles and a re-start cannot be attempted until the thermal fault is removed and the timer expires.

#### **Error Amplifier and Voltage Loop**

Since the heart of the SP7655 voltage error loop is a high performance, wide bandwidth transconductance amplifier. Because of the amplifier's current limited (+/-150 $\mu A$ ) transconductance, there are many ways to compensate the voltage loop or to control the COMP pin externally. If a simple, single pole, single

zero response is desired, then compensation can be as simple as an RC to ground. If a more complex compensation is required, then the amplifier has enough bandwidth (45° at 4 MHz) and enough gain (60dB) to run Type III compensation schemes with adequate gain and phase margins at cross over frequencies greater than 50kHz.

The common mode output of the error amplifier is 0.9V to 2.2V. Therefore, the PWM voltage ramp has been set between 1.1V and 2.2V to ensure proper 0% to 100% duty cycle capability. The voltage loop also includes two other very important features. One is an asynchronous start up mode. Basically, the synchronous rectifier can not turn on unless the high side switch has attempted to turn on or the SS pin has exceeded 1.7V. This feature prevents the controller from "dragging down" the output voltage during startup or in fault modes. The second feature is a 100% duty cycle timeout that ensures synchronized refreshing of the BST capacitor at very high duty ratios. In the event that the high side NFET is on for 20 continuous clock cycles, a reset is given to the PWM flip flop half way through the 21st cycle. This forces GL to rise for the cycle, in turn refreshing the BST capacitor. The boost capacitor is used to generate a high voltage drive supply for the high side switch, which is 5V above V<sub>IN</sub>.

#### **Power MOSFETs**

The SP7655 contains a pair of integrated low resistance N-channel switches designed to drive up to 10A of output current. Care should be taken to de-rate the output current based on the thermal conditions in the system such as ambient temperature, airflow and heat sinking. Maximum output current could be limited by thermal limitations of a particular application by taking advantage of the integrated over temperature protective scheme employed in the SP7655. The SP7655 incorporates a built-in over-temperature protection to prevent internal overheating.

#### **Setting Output Voltages**

The SP7655 can be set to different output voltages. The relationship in the following formula is based on a voltage divider from the output to the feedback pin VFB, which is set to an internal reference voltage of 0.80V. Standard 1% metal film resistors of surface mount size 0603 are recommended.

Vout =

$$0.80V (R1/R2 + 1) => R2 = R1/[(Vout/0.80V) - 1]$$

Where R1 =  $68.1 \mathrm{K}\Omega$  and for Vout =  $0.80 \mathrm{V}$  setting, simply remove R2 from the board. Furthermore, one could select the value of R1 and R2 combination to meet the exact output voltage setting by restricting R1 resistance range such that  $50 \mathrm{K}\Omega < \mathrm{R1} < 100 \mathrm{K}\Omega$  for overall system loop stability.

#### **Inductor Selection**

There are many factors to consider in selecting the inductor including core material, inductance vs. frequency, current handling capability, efficiency, size and EMI. In a typical SP7655 circuit, the inductor is chosen primarily for value, saturation current and DC resistance. Increasing the inductor value will decrease output voltage ripple, but degrade transient response. Low inductor values provide the smallest size, but cause large ripple currents, poor efficiency and more output capacitance to smooth out the larger ripple current. The inductor must be able to handle the peak current at the switching frequency without saturating, and the copper resistance in the winding should be kept as low as possible to minimize resistive power loss. A good compromise between size, loss and cost is to set the inductor ripple current to be within 20% to 40% of the maximum output current.

The switching frequency and the inductor operating point determine the inductor value as follows:

$$L = \frac{V_{OUT}(V_{IN(\text{max})} - V_{OUT})}{V_{IN(\text{max})} F_S K_r I_{OUT(\text{max})}}$$

where:

$f_S$  = switching frequency

Kr = ratio of the AC inductor ripple current to the maximum output current

The peak to peak inductor ripple current is:

$$I_{PP} = \frac{V_{OUT} \left( V_{IN(\text{max})} - V_{OUT} \right)}{V_{IN(\text{max})} F_s L}$$

Once the required inductor value is selected, the proper selection of core material is based on peak inductor current and efficiency requirements. The core must be large enough not to saturate at the peak inductor current

$$I_{PEAK} = I_{OUT(\text{max})} + \frac{I_{PP}}{2}$$

and provide low core loss at the high switching frequency. Low cost powdered iron cores have a gradual saturation characteristic but can introduce considerable AC core loss, especially when the inductor value is relatively low and the ripple current is high. Ferrite materials, although more expensive, and have an abrupt saturation characteristic with the inductance dropping sharply when the peak design current is exceeded. Nevertheless, they are preferred at high switching frequencies because they present very low core loss while the designer is only required to prevent saturation. In general, ferrite or molypermalloy materials are a better choice for all but the most cost sensitive applications.

#### **Optimizing Efficiency**

The power dissipated in the inductor is equal to the sum of the core and copper losses. To minimize copper losses, the winding resistance needs to be minimized, but this usually comes at the expense of a larger inductor. Core losses have a more significant contribution at low output current where the copper losses are at a minimum, and can typically be neglected at higher output currents where the copper losses dominate. Core loss information is usually available from the magnetic vendor. Proper inductor selection can affect the resulting power supply efficiency by more than 15%!

The copper loss in the inductor can be calculated using the following equation:

$$P_{L(Cu)} = I_{L(RMS)}^2 R_{WINDING}$$

where  $I_{L(RMS)}$  is the RMS inductor current that can be calculated as follows:

$$I_{L(RMS)} = I_{OUT(max)} \sqrt{I + \frac{I}{3} \left(\frac{I_{PP}}{I_{OUT(max)}}\right)^2}$$

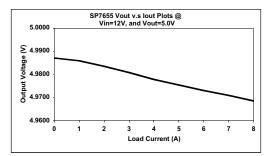

#### **Output Capacitor Selection**

The required ESR (Equivalent Series Resistance) and capacitance drive the selection of the type and quantity of the output capacitors. The ESR must be small enough that both the resistive voltage deviation due to a step change in the load current and the output ripple voltage do not exceed the tolerance limits expected on the output voltage. During an output load transient, the output capacitor must supply all the additional current demanded by the load until the SP7655 adjusts the inductor current to the new value.

In order to maintain  $V_{OUT}$ , the capacitance must be large enough so that the output voltage is helped up while the inductor current ramps to the value corresponding to the new load current. Additionally, the ESR in the output capacitor causes a step in the output voltage equal to the current. Because of the fast transient response and inherent 100%/0% duty cycle capability provided by the SP7655 when exposed to output load transient, the output capacitor is typically chosen for ESR, not for capacitance value.

The output capacitor's ESR, combined with the inductor ripple current, is typically the main contributor to output voltage ripple. The maximum allowable ESR required to maintain a specified output voltage ripple can be calculated by:

$$R_{ESR} \le \frac{\Delta V_{OUT}}{I_{PK-PK}}$$

where:

$\Delta V_{OUT}$  = Peak to Peak Output Voltage Ripple  $I_{PK-PK}$  = Peak to Peak Inductor Ripple Current

The total output ripple is a combination of the ESR and the output capacitance value and can be calculated as follows:

$$\Delta V_{OUT} = \sqrt{\frac{\left(I_{PP} (1 - D)}{C_{OUT} F_S}\right)^2 + (I_{PP} R_{ESR})^2}$$

$F_S$  = Switching Frequency

D = Duty Cycle

C<sub>OUT</sub> = Output Capacitance Value

#### **Input Capacitor Selection**

The input capacitor should be selected for ripple current rating, capacitance and voltage rating. The input capacitor must meet the ripple current requirement imposed by the switching current. In continuous conduction mode, the source current of the high-side MOSFET is approximately a square wave of duty cycle  $V_{OUT}/V_{IN}$ . More accurately the current wave form is trapezoidal, given a finite turn-on and turn-off, switch transition slope. Most of this current is supplied by the input bypass capacitors. The RMS current handling capability of the input capacitors is determined at maximum output current and under the assumption that the peak

to peak inductor ripple current is low, it is given by:

$$I_{CIN(RMS)} = I_{OUT(max)} \sqrt{D(1 - D)}$$

The worse case occurs when the duty cycle D is 50% and gives an RMS current value equal to  $I_{OUT}/2$ .

Select input capacitors with adequate ripple current rating to ensure reliable operation.

The power dissipated in the input capacitor is:

$$P_{CIN} = I_{CIN(rms)}^2 R_{ESR(CIN)}$$

This can become a significant part of power losses in a converter and hurt the overall energy transfer efficiency. The input voltage ripple primarily depends on the input capacitor ESR and capacitance. Ignoring the inductor ripple current, the input voltage ripple can be determined by:

$$\Delta V_{IN} = I_{out(\text{max})} \ R_{ESR(CIN)} + \frac{I_{OUT(MAX)} V_{OUT} (V_{IN} - V_{OUT})}{F_{\text{c}} C_{IN} V_{IN}^{2}}$$

The capacitor type suitable for the output capacitors can also be used for the input capacitors.

However, exercise extra caution when tantalum capacitors are used. Tantalum capacitors are known for catastrophic failure when exposed to surge current, and input capacitors are prone to such surge current when power supplies are connected "live" to low impedance power sources. Although tantalum capacitors have been successfully employed at the input, it is generally not recommended.

#### **Loop Compensation Design**

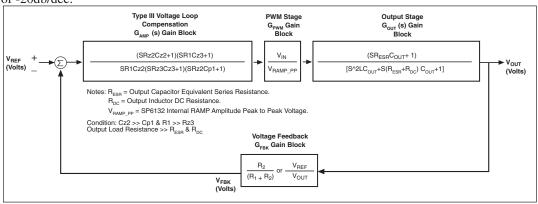

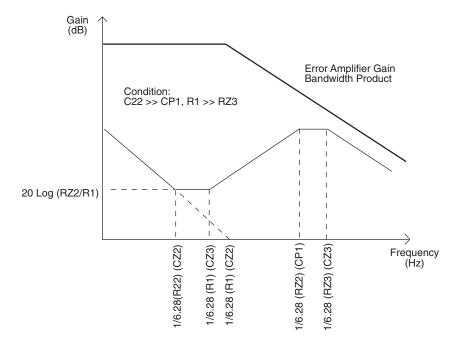

The open loop gain of the whole system can be divided into the gain of the error amplifier, PWM modulator, buck converter output stage, and feedback resistor divider. In order to cross over at the desired frequency cut-off (FCO), the gain of the error amplifier has to compensate for the attenuation caused by the rest of the loop at this frequency. The goal of loop compensation is to manipulate loop frequency response such that its cross-over gain at 0db, results in a slope of -20db/dec.

The first step of compensation design is to pick the loop cross over frequency. High cross over frequency is desirable for fast transient response, but often jeopardizes the power supply stability. Cross over frequency should be higher than the ESR zero but less than 1/5 of the switching frequency or 60kHz. The ESR zero is contributed by the ESR associated with the output capacitors and can be determined by:

$$f_{\rm Z(ESR)} = \frac{1}{2\pi \, C_{\rm OUT} \, R_{\rm ESR}}$$

The next step is to calculate the complex conjugate poles contributed by the LC output filter,

$$f_{\text{P(LC)}} = \frac{1}{2\pi \sqrt{\text{L C}_{\text{OUT}}}}$$

When the output capacitors are of a Ceramic Type, the SP7655 Evaluation Board requires a Type III compensation circuit to give a phase boost of 180° in order to counteract the effects of an under damped resonance of the output filter at the double pole frequency.

SP7655 Voltage Mode Control Loop with Loop Dynamic

**Definitions:**

$R_{ESR}$  = Output Capacitor Equivalent Series Resistance

$R_{DC}$  = Output Inductor DC Resistance

$R_{RAMP\ PP}$  = SP7655 internal RAMP Amplitude Peak to Peak Voltage

Conditions:

$C_Z 2 >> Cp1$  and R1 >> Rz3

Output Load Resistance >>  $R_{ESR}$  and  $R_{DC}$

Bode Plot of Type III Error Amplifier Compensation.

Type III Error Amplifier Compensation Circuit

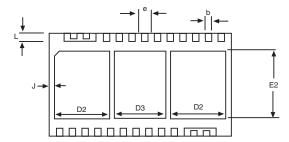

| 26 Pin DFN |           |       |       |  |

|------------|-----------|-------|-------|--|

| SYMBOL     | MIN       | NOM   | MAX   |  |

| Α          | 0.800     | 0.850 | 0.900 |  |

| A1         | 0.000     | -     | 0.050 |  |

| A3         | 0.178     | 0.203 | 0.228 |  |

| b          | 0.170     | 0.220 | 0.270 |  |

| D          | 6.950     | 7.000 | 7.050 |  |

| D2         | 2.000     | 2.050 | 2.100 |  |

| D3         | 1.780     | 1.830 | 1.880 |  |

| е          | 0.500 BSC |       |       |  |

| E          | 3.950     | 4.000 | 4.050 |  |

| E2         | 2.730     | 2.780 | 2.830 |  |

| J          | 0.200     | 0.250 | 0.300 |  |

| K          | 0.340     | 0.390 | 0.440 |  |

| L          | 0.350     | 0.400 | 0.450 |  |

Note: Dimensions in (mm) Controlling Dimension

| 26 Pin DFN |            |        |        |  |

|------------|------------|--------|--------|--|

| SYMBOL     | MIN        | NOM    | MAX    |  |

| Α          | 0.0315     | 0.0335 | 0.0355 |  |

| A1         | 0.0000     | -      | 0.0020 |  |

| A3         | 0.0067     | 0.0079 | 0.0087 |  |

| b          | 0.0067     | 0.0087 | 0.0107 |  |

| D          | 0.2737     | 0.2756 | 0.2776 |  |

| D2         | 0.0788     | 0.0808 | 0.0827 |  |

| D3         | 0.0701     | 0.0721 | 0.0741 |  |

| е          | 0.0197 BSC |        |        |  |

| Е          | 0.1556     | 0.1575 | 0.1595 |  |

| E2         | 0.1075     | 0.1095 | 0.1115 |  |

| J          | 0.0079     | 0.0099 | 0.0119 |  |

| K          | 0.0134     | 0.0154 | 0.0174 |  |

| L          | 0.0138     | 0.0158 | 0.0178 |  |

Note: Dimensions in (inches)

Conversion Factor: 1 Inch = 25.40 mm

A3

A1

Side View

**Bottom View**

#### ORDERING INFORMATION

| Part Number                                     | Temperature   | Package                      |

|-------------------------------------------------|---------------|------------------------------|

| SP7655ER/TR                                     | 40°C to +85°C | 26 Pin 7 X 4 DFN             |

| SP7655ER-L/TR                                   | 40°C to +85°C | (Lead Free) 26 Pin 7 X 4 DFN |

| /TR = Tape and Reel Pack quantity is 3,000 DFN. |               |                              |

→ CLICK HERE TO ORDER SAMPLES

**ANALOG EXCELLENCE**

Sipex Corporation

Headquarters and Sales Office 233 South Hillview Drive Milpitas, CA 95035 TEL: (408) 934-7500 FAX: (408) 935-7600

Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.