# AVERAGE MODELING, ANALYSIS AND SIMULATION OF CURRENT SHARED DC-DC CONVERTERS

Isaac Zafrany and Sam Ben-Yaakov\*

Power Electronics Laboratory

Department of Electrical and Computer Engineering

Ben-Gurion University of the Negev

P. O. Box 653, Beer-Sheva 84105

ISRAEL

Tel: +972-7-6461561; Fax: +972-7-6472949; Email: sby@bguee.ee.bgu.ac.il

Abstract - A practical, 'user-friendly' methodology is developed to study the behavior of current-shared converters. It applies average modeling, analysis and simulation to examine the static conditions and small-signal stability of converters that operate in Average Current Sharing (ACS) mode. Simple expressions for stability criterion were developed and applied to assess the influence of the number of paralleled modules on the stability and dynamics of the converters system.

#### I. INTRODUCTION

Paralleling of DC-DC converters has many desirable features: increased reliability, expandability and on-site repair when hot plug-in capability is incorporated. However, the analysis and design of parallel converters are far from being simple due to the fact that they are no longer of the single-input single-output type [1-6]. For increased reliability, paralleled converters require a Current Sharing (CS) mechanism to ensure distribution of currents and stresses between the modules. Unfortunately, the CS control introduces additional feedback loops that might render the paralleled system unstable even if each module by itself is stable [3-6].

The objective of this study was to develop a simple, 'user friendly' methodology for the analysis of current shared converter systems. The approach applies average behavioral modeling and general purpose circuit simulation programs such as PSPICE (MicroSim Inc.) to simplify the mathematical treatment. The key idea is to leave the (often messy) derivation of basic small signal transfer functions to the simulator while treating the global problem in an analytical form. The proposed method was applied to derive simple expressions that can be used to examine the effect of the CS circuitry and number of paralleled modules on the system's load-sharing stability and dynamics. Although demonstrated by considering voltage mode Buck converters operating in 'average CS' configuration [1,3-4], the proposed analytical methodology can be extended to any kind of converter modules (topologies, current or voltage mode control) with any type of CS scheme.

# II. PARALLELED CONVERTER MODULES WITH AVERAGE CURRENT SHARING

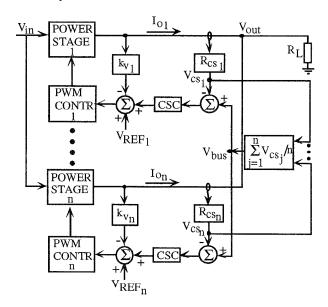

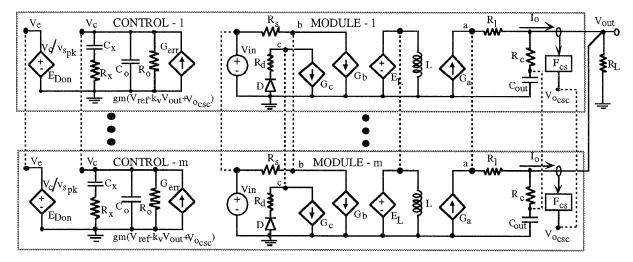

The proposed methodology will be detailed by considering a system of n paralleled DC-DC converters with Average Current Sharing (ACS) and load resistance RL. In the ACS scheme (Fig. 1) a single shared bus interconnects all the modules. The signal (normally voltage) of this common line (Vbus) represents the average load-current contribution of all units. The shared bus signal (Vbus) is compared to the output current  $I_0$  of the individual module (after translation to a voltage signal  $V_{\rm CS}$ ) and the difference adjusts by current sharing control (CSC) the reference of the voltage amplifier that senses the output voltage (scaled by  $k_{\rm V}$ ) until load current equalization is achieved.

Fig. 1 Block diagram of n paralleled converters with Average Current Sharing (ACS).

<sup>\*</sup> Corresponding author

#### III. MODELING A SINGLE CONVERTER MODULE

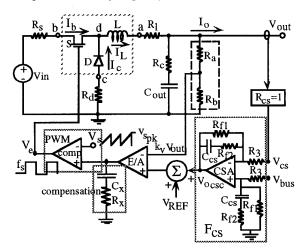

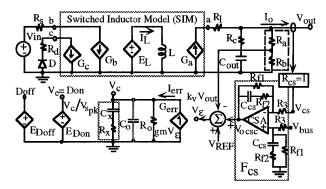

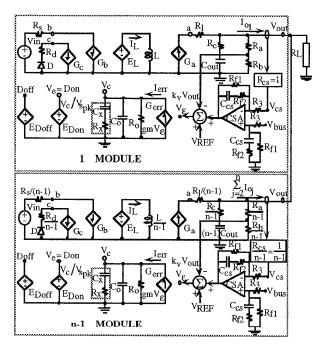

The circuit diagram of a single voltage-mode (transconductance error amplifier) controlled Buck converter module with an ACS interface (F<sub>CS</sub>) is shown in Fig. 2 and its average model based on the Switched Inductor Model (SIM) is given in Fig. 3 [7-9]. The average modeling of single converter module is shown in Fig. 3. The model is based on the Switched Inductor Model (SIM) presented in [8-9]. This model is based on the observation that by applying the average voltage across an inductor (L) one gets the average current (I<sub>L</sub>) flowing through it. This current can then be incorporated as dependent current sources to emulate the average currents of the other two ports of the switched inductor. The expressions of the dependent sources for the average model of Fig. 3 are thus as follows:

$$G_{a} = \frac{D_{0n} I_{\underline{L}}}{D_{0n} + D_{0ff}}$$

(1)

$$G_b = \frac{D_{off} I_L}{D_{on} + D_{off}}$$

(2)

$$G_{C} = I_{L}$$

(3)

$$E_{L} = V_{ac} D_{on} + V_{bc} D_{off}$$

(4)

where Don is the duty-cycle and

$$D_{off} = \frac{2 \ I_L \ L \ f_S}{V_{ac} \ D_{on}} - D_{on} \ \ \text{for Discontinuous Conduction Mode}$$

or  $D_{off} = 1 - D_{on}$  for Continuous Conduction Mode (5)

where  $f_S$  is the switching frequency.

Fig. 2. Circuit diagram of a single voltage-mode controlled Buck converter module with ACS interface.

Fig. 3. Average Switched Inductor Model (SIM) of the Buck converter module shown in Fig. 2.

In Fig.3  $G_C$  represents the average current feeding the steering diode D (Fig.2),  $E_L$  is the average voltage across the inductor (4),  $G_b$  is the average current of the input port (b) and  $G_a$  is the average current fed to the load (a). The voltage error amplifier (Fig.2) is represented in Fig. 3 as transconductance dependent source ( $G_{err}$ ).  $E_{Don}$  and  $E_{Doff}$  in Fig. 3 are dependent sources that generate the voltage coded  $D_{on}$  and  $D_{off}$  as a function of PWM generator ( $V_c/V_{spk}$ ) (Fig. 2). The Current Sharing Amplifier (CSA) in Fig. 2 is implemented in Fig. 3 by voltage dependent source with gain of  $10^5$ .

## IV. STATIC ANALYSIS OF N PARALLELED MODULES

Assuming that the combined error voltage  $V_{\epsilon} \rightarrow 0$  (high gain E/A), the reference voltage of an arbitrary X-th converter module  $(V_{REF_X})$  (Figs. 2,3) is related to other relevant parameters by the relationship:

$$V_{REF_x} = k_{V_x} V_{OUT} + k_{CS_x} (I_{O_x} - V_{BUS})$$

(6)

where  $k_{CS_X}=R_{f1}/R_3$  is the DC gain of  $F_{CS_X}$  (Figs. 2,3) and all other parameters in this equation refer to steady-state values.

The bus voltage is a function of output currents of all converter modules:

$$V_{BUS} = \frac{\sum_{j=1}^{n} I_{O_j}}{n}$$

(7)

We assume that  $k_{v_1} = ... = k_{v_n} = k_v$ . The output voltage is then derived from (6):

$$V_{OUT} = \frac{V_{REF_{av}}}{k_v}$$

(8)

where

$$V_{REF_{av}} = \frac{\sum_{j=1}^{n} V_{REF_{j}}}{n}$$

(9)

When  $V_{REF_X} \neq V_{REF_y}$  and  $k_{CS_1} = ... = k_{CS_n} = k_{CS}$ , the output current distribution of any two converter modules is found to be:

$$I_{O_X} - I_{O_Y} = \frac{V_{REF_X} - V_{REF_Y}}{k_{CS}}$$

(10)

The last equation implies that the current distribution between any two converter modules with different reference voltage (VREF) will exhibit smaller imbalance when k<sub>CS</sub> is large enough.

## V. DYNAMIC ANALYSIS OF N PARALLELED MODULES

The analysis of n paralleled modules system now proceeds under the assumption that all modules are identical. The small signal model of a single converter module is based on the average model of Fig. 3. Two transfer functions for this module are defined for a given j-th module:

$$H_{j} = \frac{i_{0j}}{v_{e_{j}}} \qquad \qquad F_{j} = \frac{v_{e_{j}}}{v_{\varepsilon_{j}}}$$

(11)

$H_j$  describes the converter's small signal transfer function from the error voltage  $v_{\boldsymbol{e}_j}$  to the converter's output current  $i_{0_j}$ , and  $F_j$  is the feedback small signal from the combined error voltage  $v_{\boldsymbol{e}_j}$  to the error voltage  $v_{\boldsymbol{e}_j}$  (Fig. 3). The H and F transfer functions can be derived analytically [8] or evaluated by simulation [7-9]. The latter method, which is of course much easier to execute, is less prone to errors but yet provides all the necessary information for a thorough analysis of a CS converter system. This 'mixed mode' (simulation-analytical) approach is applied here. In the followings, 'measured' means obtained by simulation.

The combined error voltage  $v_{\varepsilon}$  includes four components:

$$V_{\varepsilon} = F_{cs} v_{bus} - F_{cs} i_{o} + v_{ref} - k_{v} v_{out}$$

(12)

where  $F_{CS}$  describes the small signal transfer function of CS loop  $(Vo_{CSC}/(v_{bus} - i_0))$  (Figs. 2,3). Setting  $v_{ref}$  to zero (because it does not affect small-signal stability), the following expression for an arbitrary X-th module was obtained:

$$v_{\varepsilon_{\mathbf{X}}} = -i_{O_{\mathbf{X}}} \left( \frac{n-1}{n} F_{CS} + k_{V} R_{L} \right) + \left( \sum_{j=1}^{n} i_{O_{j}} - i_{O_{\mathbf{X}}} \right) \left( \frac{F_{CS}}{n} - k_{V} R_{L} \right)$$

(13)

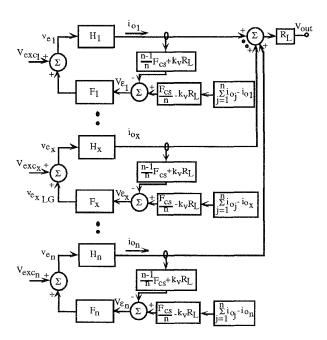

Fig. 4. Small signal block diagram for n parallel modules with ACS driving a load  $R_L$ .

Following the above procedure, the small signal output current of any given X-th module was found to be:

$$i_{O_{X}} = \left[ -i_{O_{X}} \left( \frac{n-1}{n} F_{CS} + k_{V} R_{L} \right) + \left( \sum_{j=1}^{n} i_{O_{j}} -i_{O_{X}} \right) \left( \frac{F_{CS}}{n} - k_{V} R_{L} \right) \right] F_{X} H_{X}$$

(14)

Since the location of the single AC voltage source excitation is in the X-th module (Fig. 4) it will influence the measured (by simulation) transfer function  $H_X$ . That is  $H_X \neq H$  where H is the measured transfer function of all modules except the X-th. Hence,  $i_{0_X} \neq i_0$  where  $i_0$  is the output current of all modules except the X-th. However, the measured transfer function  $F_j$  of all identical modules including X-th is the same, i.e.  $F_i = F$ .

The output current of each module except the X-th is related to the output current of the X-th module by following equation:

$$i_{O} = \frac{\left(\frac{F_{CS}}{n} - k_{V}R_{L}\right)FH}{1 + \left(\frac{F_{CS}}{n} - (n-1)k_{V}R_{L}\right)FH}i_{O_{X}}$$

(15)

The loop-gain for 'single excitation' of X-th module  $((L.G)_X)$  is obtained from (14) and (15):

$$(L.G)_{X} = \left\{ \left( \frac{n-1}{n} F_{CS} + k_{V} R_{L} \right) - \frac{(n-1) \left( \frac{F_{CS}}{n} - k_{V} R_{L} \right)^{2} FH}{1 + \left( \frac{F_{CS}}{n} - (n-1) k_{V} R_{L} \right) FH} \right\} FH_{X}$$

(16)

Although (16) is theoretically correct, it is extremely hard to apply in practical cases. One reason for that is the fact, that the transfer functions H represent the transfer function  $i_0/v_e$  of any given module while loaded by  $R_L$  in parallel with the parallel output impedances of (n-1) modules. To overcome this difficulty we purpose to use average simulation to obtain the key dynamic parameters of the systems. Three tests are proposed: a global stability test, the common mode response and current sharing (differential) response.

#### Global stability test

The stability and dynamic performance of the system can now be evaluated by singling out one converter (to be labeled 'X') and performing a traditional loop gain analysis around this unit. To this end, an external independent AC voltage source excitation should be placed in series with the dutycycle  $E_{Don}$  dependent source (Fig. 3) [10]. The excitation is included only in the X-th module,  $V_{exc_x}=1[Vac]$  while in the other modules  $V_{exc_j}=0$  (Fig. 4). The loop-gain and phasemargin can now be obtained by examining  $Ve_{xL_G}/Ve_x$ . Since the sample module X is arbitrarily chosen, the derived loop gain is in fact the loop gain of the system, since it describes the dynamic response of the any module to a

#### Common mode response

disturbance.

To test the inner-loops control of the system (voltage loop in voltage-mode or current and voltage loops in current-mode), a common AC voltage source excitation should be applied to all paralleled converter modules (Fig. 4)  $V_{exc_1} = V_{exc_x} = .... = V_{exc_n} = 1[Vac].$  It induces equal output currents  $i_{o_1} = i_{o_x} = .... = i_{o_n} = i_o \text{ and } v_{bus} = i_o \text{ and therefore eqs.}$  (12) and (13) reduce in this case to:

$$v_{\varepsilon} = -k_{v} v_{out} = -k_{v} n i_{o} R_{L}$$

(17)

Hence, the loop-gain of any given module is found to be:

$$L.G_C = -k_V n R_L H_C F_C$$

(18)

where the transfer functions  $H_C$ ,  $F_C$  for the common excitation case have the same basic definitions of (11). The total feedback loop ( $\beta_C$ ) transfer function reduces to:

$$\beta_{\rm C} = k_{\rm V} \, n \, R_{\rm L} \, F_{\rm C} \tag{19}$$

where the feedback loop  $\beta_C$  can be obtained by measuring  $Ve_{XLG}/i_{0_X}$  (Fig. 4). However,  $H_C$  differs from H and  $H_X$ , due to the otherwise loading. It should be noted, that  $H_C$  can be easily obtained by simulation or analytically and the control voltage loop ( $F_C$ ) now can be independently designed. Indeed, loop-gain  $LG_C$  (18) offers the ability to examine the stability of n paralleled converters loaded by  $R_L$  without the influences of current-sharing loop. Applying (18) the loop-gain and the phase-margin of each module are obtained. It means that, this case examines only the dynamic response of a common (or identical) perturbation in all the modules.

#### The differential response

To examine the influence of current-sharing loop (outer-loop) on the stability of the system we apply now a differential AC voltage source excitation. In this case, we examine arbitrarily the X-th module by applying  $V_{exc_X}=1[Vac]$  into the X-th module (Fig. 4) and  $V_{exc_1}=...=V_{exc_n}=-1/(n-1)[Vac]$  into the other modules. Since all modules are identical, it induces  $i_{01}=...=i_{0n}=i_{0=}-i_{0_X}/(n-1)$ , which implies  $v_{bus}=0$  and  $v_{out}=0$ . It also follows that the load current is zero:

$${}^{i}R_{L} = {}^{i}O_{1} + ... + {}^{i}O_{X} + ... + {}^{i}O_{n} = (n-1){}^{i}O_{1} + {}^{i}O_{X} = 0,$$

and therefore eqs. (12) and (13) reduce to:

$$v_{\mathcal{E}_{\mathbf{X}}} = -F_{\mathbf{CS}_{\mathbf{X}}} i_{\mathbf{O}_{\mathbf{X}}}$$

(20)

Thus, the loop-gain of arbitrary X-th module for differential excitation is given by:

$$(L.G_d)_{\mathbf{x}} = -F_{\mathbf{c}\mathbf{s}_{\mathbf{x}}} H_{\mathbf{d}_{\mathbf{x}}} F_{\mathbf{d}_{\mathbf{x}}}$$

(21)

where the transfer functions  $H_{d_X}$  and  $F_{d_X}$  for the differential excitation case have the same basic definitions as shown in (11). The total feedback loop transfer function from (21) can be expressed as:

$$\beta_{\mathbf{d_x}} = \mathbf{F_{CS_x}} \, \mathbf{F_{d_x}} \tag{22}$$

where  $\beta_{d_X}$  can be obtained by measuring  $Ve_{XLG}/i_{0_X}$  (Fig. 4). Indeed, this case examines the sample module X when it is loaded only by the other (n-1) modules, because the total current load perturbations are zero and the load  $R_L$  has thus no effect, which means that  $H_{d_X}$  differs from  $H_C$  and H. The importance of eq. (21) is its ability to examine or even design the current-sharing control loop without the effects of the voltage control loop. Consequently, this case explores the dynamic response of differential perturbations between the modules.

The observation of the general expressions (16), (18), (19), (21) and (22) can be practiced as follows. For a given  $H_C$  (analytically or by simulation) the  $LG_C$  (18) and (19) can

Fig. 5. The current and voltage properties of paralleled brunch in identical converter modules.

be used to design the inner loop  $F_C$  ( $F=F_C=F_d$ ). Now,  $H_d$  can be obtained by simulation and through  $LG_d$  (21) and (22) the outer loop  $F_{CS}$  can be designed. This procedure grants the ability to predict by simulations the influence of the transfer functions H, F, load resistance  $R_L$  and number of modules  $R_L$  no the loop-gain ( $R_L$ ). Consequently, these relationships can be used in a simple manner to stabilize the system and/or improve the system's phase-margin as follows:

- Design and stabilize the inner loops according of the procedure of 'common mode response'.

- Design and stabilize the outer-loop (CS loop) according of the procedure of 'differential response'.

- 3. Determine the phase-margin of the overall system by 'single excitation'.

#### VI. THE FOLDED MODEL

The procedures suggested above involve simulation of systems with n modules. In some cases m modules are identical and parallel connected to the load. To simplify and cut simulation time we can 'fold' m parallel connected units into a single unit. This is justified by the fact that all node voltages of identical units are equal and hence can be connected (Fig. 5). By doing this the system of m parallel units is reduced to a single unit. However, some 'folding rules' have to be observed:

- Control circuitry is left as is. The reason is that the small signal response of a single circuit or m parallel connected control circuits are the same.

- In case when m power stages feed a load, the impedances have to be reduced by m. This is needed to correctly represent the lower output impedance of m parallel connected power stage units.

Following these 'folding rules' n current shared modules can be represent as a basic module in parallel to an (n-1) folded unit (Fig. 6).

Fig. 6. The folded model that includes one original module with n-1 folded modules.

#### VII. SIMULATION RESULTS

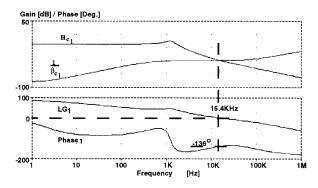

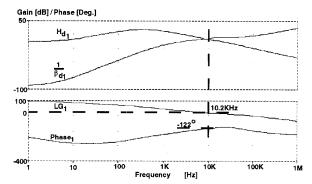

To illustrate the above proposed procedures for testing parallel ACS system, Bode plots of loop-gain (gain and phase) and transients output voltage and currents were simulated by PSPICE (V. 7.1, MicroSim Inc.) for three paralleled modules similar to Fig 3 by applying the folded model of Fig. 6.

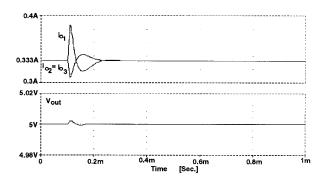

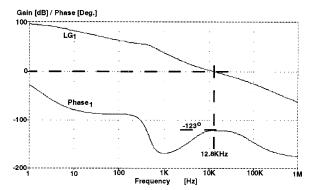

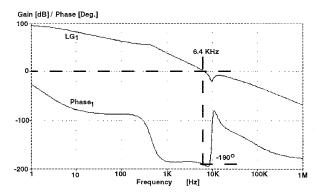

The parameters of the three converters were as follows: common load R<sub>L</sub>= $5\Omega$ , power stage:  $V_{in}=12V$ , L= $75\mu$ H,  $C_{out}=220\mu F$ ,  $R_c=0.07\Omega$ ,  $R_s=0.1\Omega$ ,  $R_d=0.1\Omega$ ,  $R_l=0.1\Omega$ ,  $R_a=R_b=10K\Omega$ . voltage control loop:  $V_{REF}=2.5V$ , gm=3.21[mA/V],  $R_0$ =3M $\Omega$ ,  $C_0$ =177pF,  $R_X$ =12.3K $\Omega$ ,  $C_x=25.9$ nF,  $V_{S_{DK}}=2.5$ V. current-sharing loop:  $R_{CS}=1\Omega$ ,  $R_3=10k\Omega$ ,  $R_{f1}=100K\Omega$ ,  $C_{cs}=145nF$  and  $R_{f2}=250\Omega$  and later R<sub>f2</sub>=0. Analysis and design techniques were verified by running two sets of simulations. All sets were done on the complete parallel system as a function of Rf2. The resulting Bode plots of  $H_C$ ,  $1/\beta_C$ ,  $LG_C$  and phase under common excitation Vexc<sub>1</sub>=Vexc<sub>2.3</sub>=1[Vac] (Fig.4) are shown in Fig. 7. The crossover phase is -136°, indicating stable operation with phase-margin (PM) of 44°. Note that CS loop (or Rf2) does not influence upon LG<sub>C</sub>. We now examine the Bode plot (Fig. 8) of  $H_d$ ,  $1/\beta_d$ ,  $LG_d$  and phase for the arbitrary 1-th module under differential-mode excitation Vexc<sub>1</sub>=1[Vac] and Vexc<sub>2.3</sub>=-1/2[Vac]. The crossover phase is -122<sup>0</sup>, indicating stable operation with phase-margin of 58°. The transient response of three parallel converters is simulated by 10mV, pulse 10[µSec] excitation injected into voltage error amplifier (E/A) of the 1-th module. Fig. 9 shows the resulting response of the three converter output currents, which quickly decay down, indicating reasonable stability. Fig. 10 shows the Bode plot of the overall LG (eq. 16) and phase for 1-th module under single excitation Vexc<sub>1</sub>=1[Vac] and Vexc<sub>2.3</sub>=0 to confirm the stability for the combination of the common and differential modes PM=570.

Fig. 7. Bode plots of three identical paralleled modules with ACS under common excitation.

Fig. 8. Bode plots of three identical paralleled modules with ACS under differential excitation, with  $R_{f2}$ =250 $\Omega$ .

Fig. 9. Transient simulations of output currents and output voltage of three identical paralleled modules, with  $R_{f2}$ =250 $\Omega$ , when the pulse excitation is injected into the first module.

Fig. 10. Bode plots of ACS system with three identical modules under single excitation, with  $R_{f2}$ =250 $\Omega$ .

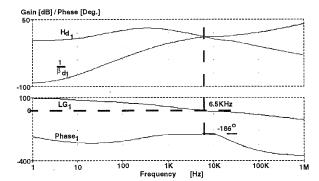

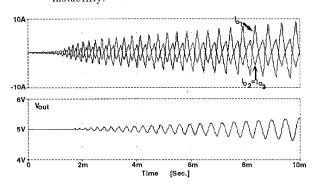

Next,  $R_{f2}$  was set to zero. The Bode plot under differential-mode is shown in Fig. 11, where the crossover phase is  $^{-186^{\circ}}$ , indicating instability, with phase-margin of  $^{-6^{\circ}}$ . The simulated transient response is shown in Fig. 12, where the amplitude of the output current of the three modules is increasing, as expected. Bode plot under single module excitation in Fig. 13 verify instability again PM= $^{-10^{\circ}}$ .

Fig. 11. Bode plots of three identical paralleled modules under differential excitation, with  $R_{f2}=0$ , indicating instability.

Fig. 12. Transient simulations of output currents and output voltage of three identical paralleled modules, with R<sub>f2</sub>=0, when the pulse excitation is injected into the first module.

Fig. 13. Bode plots of ACS system with three identical paralleled modules under single excitation, with  $R_{\rm f2}$ =0.

#### VIII. DISCUSSION AND CONCLUSIONS

Results of this study clearly show that stability conditions of a paralleled ACS converter system can be readily analyzed by applying the methodology proposed in this investigation. The methodology is based on frequency

domain loop gain response which is conveniently obtained by average simulation. The LG expressions (16), (18), (21) developed for an ACS system of n paralleled identical modules were found efficient to correctly predict the system's behavior. These relationships can thus be used in the design phase of a ACS converter system. The theoretical implications of (16), (18), (21) are discussed and used in representative example. To illustrate and design n identical converter modules, we developed a folded model that can simplify the simulations based methodology proposed in this investigation. The present study considered a voltage mode Buck module but the results are general and apply to any topology and any control method (e.g. Boost in peak current mode) as long as the pertinent transfer functions H and F can be derived or obtained by average simulation. Applying the general 'mixed mode' methodology proposed here, other CS scheme can be analyzed for their static and dynamic behavior.

#### REFERENCES

- [1] M. Jordan, "UC3907 load share IC simplifies parallel power supply design", *Unitrode Application Note U-129. Product & Application Handbook*, pp. 9-296 9-305, 1993-1994.

- [2] J. S. Glaser and A. F. Witulski, "Output plane analysis of load-sharing in multiple-module converter system," *IEEE Trans. on Power Electronics*, vol. 9, pp. 43-50, Jan. 1994.

- [3] V. J. Thottuvelil and G. C. Verghese, "Stability analysis of paralleled DC/DC converters with active current-sharing," *IEEE Trans. PESC Rec.*, pp. 1080-1086, 1996.

- [4] V. J. Thottuvelil and G. C. Verghese, "Analysis and control design paralleled DC-DC converters with current-sharing," *IEEE Trans. APEC Rec.*, pp. 638-646, 1997.

- [5] Y. Panov, J. Rajagopalan, and F. C. Lee, "Analysis and design of N paralleled DC-DC converters with master-slave current-sharing control," *IEEE Trans. APEC Rec.*, pp. 436-442, 1997.

- [6] J. Rajagopalan, K. Xing, Y. Guo, and F. C. Lee, "Modeling and dynamic analysis of paralleled DC/DC converters with master/slave current sharing control," *IEEE Trans. APEC Rec.*, pp. 674-684, 1996.

- [7] S. Ben-Yaakov, "SPICE simulation of PWM DC-DC converter systems: Voltage feedback, continuous inductor conduction mode," *IEE Electronics Letters*, Vol. 25, No. 16, 1989, pp. 1061-1063.

- [8] S. Ben-Yaakov and D. Adar, "Average models as tools for studying the dynamics of switch mode DC-DC converters," *IEEE Trans. PESC Rec.*, pp. 1218-1225, Taipei, 1994.

- [9] S. Ben-Yaakov, "Average simulation of PWM converters by direct implementation of behavioral relationships," *Int. J. Electronics*, Vol. 77, No. 5, pp. 731-746, 1994.

- [10] P. W. Tuinenga, SPICE: A guide to circuit simulation and analysis using Pspice, Prentice-Hall, New-Jersey, 1992.