THIS DRAFT SPECIFICATION DOCUMENT IS PROVIDED TO YOU "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE. THE USB-IF AND USB 2.0 PROMOTERS DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTS, RELATING TO USE OF INFORMATION IN THIS DRAFT SPECIFICATION. THE PROVISION OF THIS DRAFT SPECIFICATION TO YOU DOES NOT PROVIDE YOU WITH ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS. THIS DOCUMENT IS AN INTERMEDIATE DRAFT AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

**Note on USB 2.0 Bit Rate:** This specification draft calls out a data rate of 480Mb/s. This is the target rate for which the Electrical Working Group is designing and prototyping; this rate needs to be confirmed with completed validation of prototype IC's operating on test boards.

# Chapter 5 USB Data Flow Model

This chapter presents information about how data is moved across the USB. The information in this chapter affects all implementers. The information presented is at a level above the signaling and protocol definitions of the system. Consult Chapter 7 and Chapter 8 for more details about their respective parts of the USB system. This chapter provides framework information that is further expanded in Chapters 9 through 11. All implementers should read this chapter so they understand the key concepts of the USB.

#### 5.1 Implementer Viewpoints

The USB provides communication services between a host and attached USB devices. However, the simple view an end user sees of attaching one or more USB devices to a host, as in Figure 5-1, is in fact a little more complicated to implement than is indicated by the figure. Different views of the system are required to explain specific USB requirements from the perspective of different implementers. Several important concepts and features must be supported to provide the end user with the reliable operation demanded from today's personal computers. The USB is presented in a layered fashion to ease explanation and allow implementers of particular USB products to focus on the details related to their product.

Figure 5-1. Simple USB Host/Device View

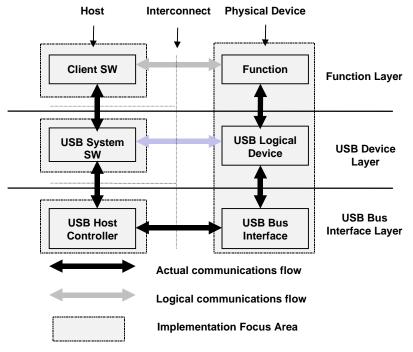

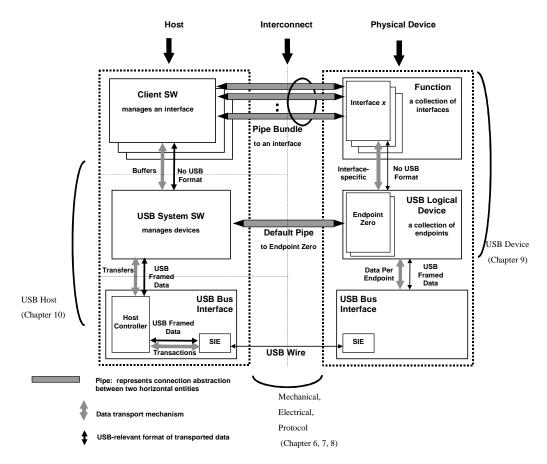

Figure 5-2 shows a deeper overview of the USB, identifying the different layers of the system that will be described in more detail in the remainder of the specification. In particular, there are four focus implementation areas:

- USB Physical Device: A piece of hardware on the end of a USB cable that performs some useful end user function.

- Client Software: Software that executes on the host, corresponding to a USB device. This client software is typically supplied with the operating system or provided along with the USB device.

- USB System Software: Software that supports the USB in a particular operating system. The USB System Software is typically supplied with the operating system, independently of particular USB devices or client software.

• USB Host Controller (Host Side Bus Interface): The hardware and software that allows USB devices to be attached to a host.

There are shared rights and responsibilities between the four USB system components. The remainder of this specification describes the details required to support robust, reliable communication flows between a function and its client.

Figure 5-2. USB Implementation Areas

As shown in Figure 5-2, the simple connection of a host to a device requires interaction between a number of layers and entities. The USB Bus Interface layer provides physical/signaling/packet connectivity between the host and a device. The USB Device Layer is the view the USB System Software has for performing generic USB operations with a device. The Function Layer provides additional capabilities to the host via an appropriate matched client software layer. The USB Device and Function layers each have a view of logical communication within their layer that actually uses the USB Bus Interface Layer to accomplish data transfer.

The physical view of USB communication as described in Chapters 6, 7, and 8 is related to the logical communication view presented in Chapters 9 and 10. This chapter describes those key concepts that affect USB implementers and should be read by all before proceeding to the remainder of the specification to find those details most relevant to their product.

To describe and manage USB communication, the following concepts are important:

- Bus Topology: Section 5.2 presents the primary physical and logical components of the USB and how they interrelate.

- Communication Flow Models: Sections 5.3 through 5.8 describe how communication flows between the host and devices through the USB and defines the four USB transfer types.

- Bus Access Management: Section 5.11 describes how bus access is managed within the host to support a broad range of communication flows by USB devices.

• Special Consideration for Isochronous Transfers: Section 5.12 presents features of the USB specific to devices requiring isochronous data transfers. Device implementers for non-isochronous devices do not need to read Section 5.12.

#### 5.2 Bus Topology

There are four main parts to USB topology:

- Host and Devices: The primary components of a USB system.

- Physical Topology: How USB elements are connected.

- Logical Topology: The roles and responsibilities of the various USB elements and how the USB appears from the perspective of the host and a device.

- Client Software-to-function Relationships: How client software and its related function interfaces on a USB device view each other.

#### 5.2.1 USB Host

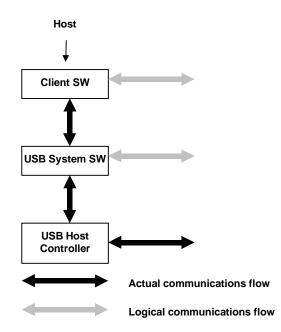

The host's logical composition is shown in Figure 5-3, and includes the following:

- USB Host Controller

- Aggregate USB System Software (USB Driver, Host Controller Driver, and host software)

- Client.

Figure 5-3. Host Composition

The USB host occupies a unique position as the coordinating entity for the USB. In addition to its special physical position, the host has specific responsibilities with regard to the USB and its attached devices. The host controls all access to the USB. A USB device gains access to the bus only by being granted access by the host. The host is also responsible for monitoring the topology of the USB.

For a complete discussion of the host and its duties, refer to Chapter 10.

### 5.2.2 USB Devices

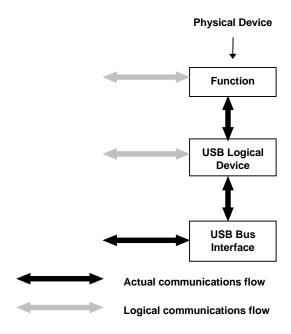

A USB physical device's logical composition is shown in Figure 5-4, and includes the following:

- USB bus interface

- USB logical device

- Function.

USB physical devices provide additional functionality to the host. The types of functionality provided by USB devices vary widely. However, all USB logical devices present the same basic interface to the host. This allows the host to manage the USB-relevant aspects of different USB devices in the same manner.

To assist the host in identifying and configuring USB devices, each device carries and reports configuration-related information. Some of the information reported is common among all logical devices. Other information is specific to the functionality provided by the device. The detailed format of this information varies, depending on the device class of the device.

For a complete discussion of USB devices, refer to Chapter 9.

Figure 5-4. Physical Device Composition

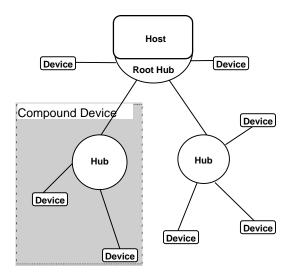

### 5.2.3 Physical Bus Topology

Devices on the USB are physically connected to the host via a tiered star topology, as illustrated in Figure 5-5. USB attachment points are provided by a special class of USB device known as a hub. The additional attachment points provided by a hub are called ports. A host includes an embedded hub called the root hub. The host provides one or more attachment points via the root hub. USB devices that provide additional functionality to the host are known as functions. To prevent circular attachments, a tiered ordering is imposed on the star topology of the USB. This results in the tree-like configuration illustrated in Figure 5-5.

Figure 5-5. USB Physical Bus Topology

Multiple functions may be packaged together in what appears to be a single physical device. For example, a keyboard and a trackball might be combined in a single package. Inside the package, the individual functions are permanently attached to a hub and it is the internal hub that is connected to the USB. When multiple functions are combined with a hub in a single package, they are referred to as a compound device. From the host's perspective, a compound device is the same as a separate hub with multiple functions attached. Figure 5-5 also illustrates a compound device.

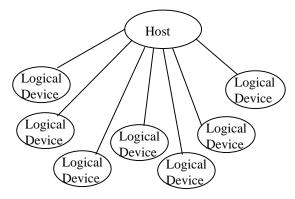

### 5.2.4 Logical Bus Topology

While devices physically attach to the USB in a tiered, star topology, the host communicates with each logical device as if it were directly connected to the root port. This creates the logical view illustrated in Figure 5-6 that corresponds to the physical topology shown in Figure 5-5. Hubs are logical devices also, but are not shown in Figure 5-6 to simplify the picture. Even though most host/logical device activities use this logical perspective, the host maintains an awareness of the physical topology to support processing the removal of hubs. When a hub is removed, all of the devices attached to the hub must be removed from the host's view of the logical topology. A more complete discussion of hubs can be found in Chapter 11.

Figure 5-6. USB Logical Bus Topology

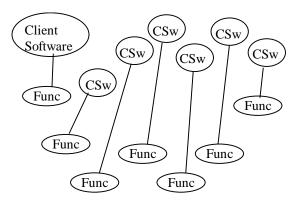

#### 5.2.5 Client Software-to-function Relationship

Even though the physical and logical topology of the USB reflects the shared nature of the bus, client software (CSw) manipulating a USB function interface is presented with the view that it deals only with its interface(s) of interest. Client software for USB functions must use USB software programming interfaces to manipulate their functions as opposed to directly manipulating their functions via memory or I/O accesses as with other buses (e.g., PCI, EISA, PCMCIA, etc.). During operation, client software should be independent of other devices that may be connected to the USB. This allows the designer of the device and client software to focus on the hardware/software interaction design details. Figure 5-7 illustrates a device designer's perspective of the relationships of client software and USB functions with respect to the USB logical topology of Figure 5-6.

Figure 5-7. Client Software-to-function Relationships

### 5.3 USB Communication Flow

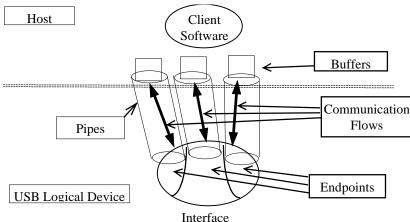

The USB provides a communication service between software on the host and its USB function. Functions can have different communication flow requirements for different client-to-function interactions. The USB provides better overall bus utilization by allowing the separation of the different communication flows to a USB function. Each communication flow makes use of some bus access to accomplish communication between client and function. Each communication flow is terminated at an endpoint on a device. Device endpoints are used to identify aspects of each communication flow.

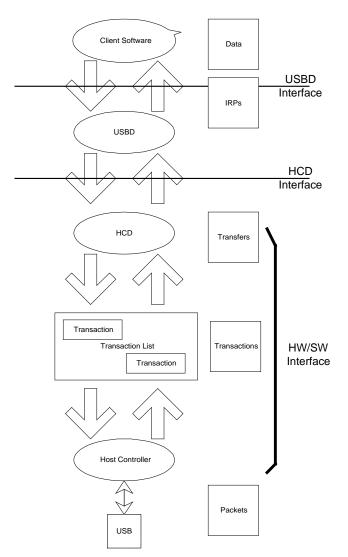

Figure 5-8 shows a more detailed view of Figure 5-2. The complete definition of the actual communication flows of Figure 5-2 supports the logical device and function layer communication flows. These actual communication flows cross several interface boundaries. Chapters 6 through 8 describe the mechanical, electrical, and protocol interface definitions of the USB "wire." Chapter 9 describes the USB device programming interface that allows a USB device to be manipulated from the host side of the wire. Chapter 10 describes two host side software interfaces:

- Host Controller Driver (HCD): The software interface between the USB Host Controller and USB System Software. This interface allows a range of Host Controller implementations without requiring all host software to be dependent on any particular implementation. One USB Driver can support different Host Controllers without requiring specific knowledge of a Host Controller implementation. A Host Controller implementer provides an HCD implementation that supports the Host Controller.

- USB Driver (USBD): The interface between the USB System Software and the client software. This interface provides clients with convenient functions for manipulating USB devices.

Figure 5-8. USB Host/Device Detailed View

A USB logical device appears to the USB system as a collection of endpoints. Endpoints are grouped into endpoint sets that implement an interface. Interfaces are views to the function. The USB System Software manages the device using the Default Control Pipe. Client software manages an interface using pipe bundles (associated with an endpoint set). Client software requests that data be moved across the USB between a buffer on the host and an endpoint on the USB device. The Host Controller (or USB device, depending on transfer direction) packetizes the data to move it over the USB. The Host Controller also coordinates when bus access is used to move the packet of data over the USB.

Figure 5-9 illustrates how communication flows are carried over pipes between endpoints and host side memory buffers. The following sections describe endpoints, pipes, and communication flows in more detail.

Figure 5-9. USB Communication Flow

Software on the host communicates with a logical device via a set of communication flows. The set of communication flows are selected by the device software/hardware designer(s) to efficiently match the communication requirements of the device to the transfer characteristics provided by the USB.

### 5.3.1 Device Endpoints

An endpoint is a uniquely identifiable portion of a USB device that is the terminus of a communication flow between the host and device. Each USB logical device is composed of a collection of independent endpoints. Each logical device has a unique address assigned by the system at device attachment time. Each endpoint on a device is given at design time a unique device-determined identifier called the endpoint number. Each endpoint has a device-determined direction of data flow. The combination of the device address, endpoint number, and direction allows each endpoint to be uniquely referenced. Each endpoint is a simplex connection that supports data flow in one direction: either input (from device to host) or output (from host to device).

An endpoint has characteristics that determine the type of transfer service required between the endpoint and the client software. Endpoints describe themselves by:

- Their bus access frequency/latency requirements •

- Their bandwidth requirements .

- Their endpoint number

- The error handling behavior requirements •

- Maximum packet size that the endpoint is capable of sending or receiving •

- The transfer type for the endpoint (refer to Section 5.4 for details) •

• The direction data is transferred between the endpoint and the host.

Endpoints other than those with endpoint number zero are in an unknown state before being configured and may not be accessed by the host before being configured.

### 5.3.1.1 Endpoint Zero Requirements

All USB devices are required to implement a default control method that uses both the input and output endpoints with endpoint number zero. The USB System Software uses this default control method to initialize and generically manipulate the logical device (e.g., to configure the logical device) as the Default Control Pipe (see Section 5.3.2). The Default Control Pipe provides access to the device's configuration information and allows generic USB status and control access. The Default Control Pipe supports control transfers as defined in Section 5.5. The endpoints with endpoint number zero are always accessible once a device is attached, powered, and has received a bus reset.

<u>A USB device that is capable of operating at high-speed must have a minimum level of support for</u> operating at full-speed. When the device is attached to a hub operating in full-speed, the device must:

- Be able to reset successfully at full-speed.

- Respond successfully to standard requests: set\_address, set\_configuration, get\_descriptor for device and configuration descriptors; and return appropriate information.

The high-speed device may or may not be able to support its intended functionality when operating at fullspeed.

### 5.3.1.2 Non-endpoint Zero Requirements

Functions can have additional endpoints as required for their implementation. Low-speed functions are limited to two optional endpoints beyond the two required to implement the Default Control Pipe. Full-speed devices can have additional endpoints only limited by the protocol definition (i.e., a maximum of 15 additional input endpoints and 15 additional output endpoints).

Endpoints other than those for the Default Control Pipe cannot be used until the device is configured as a normal part of the device configuration process (refer to Chapter 9).

#### 5.3.2 Pipes

A USB pipe is an association between an endpoint on a device and software on the host. Pipes represent the ability to move data between software on the host via a memory buffer and an endpoint on a device. There are two different, mutually exclusive, pipe communication modes:

- Stream: Data moving through a pipe has no USB-defined structure

- Message: Data moving through a pipe has some USB-defined structure.

The USB does not interpret the content of data it delivers through a pipe. Even though a message pipe requires that data be structured according to USB definitions, the content of the data is not interpreted by the USB.

Additionally, pipes have the following associated with them:

- A claim on USB bus access and bandwidth usage.

- A transfer type.

- The associated endpoint's characteristics, such as directionality and maximum data payload sizes. The data payload is the data that is carried in the data field of a data packet within a bus transaction (as defined in Chapter 8).

The pipe that consists of the two endpoints with endpoint number zero is called the Default Control Pipe. This pipe is always available once a device is powered and has received a bus reset. Other pipes come into existence when a USB device is configured. The Default Control Pipe is used by the USB System Software to determine device identification and configuration requirements, and to configure the device. The Default Control Pipe can also be used by device-specific software after the device is configured. The USB System Software retains "ownership" of the Default Control Pipe and mediates use of the pipe by other client software.

A software client normally requests data transfers via I/O Request Packets (IRPs) to a pipe and then either waits or is notified when they are completed. Details about IRPs are defined in an operating system-specific manner. This specification uses the term to simply refer to an identifiable request by a software client to move data between itself (on the host) and an endpoint of a device in an appropriate direction. A software client can cause a pipe to return all outstanding IRPs if it desires. The software client is notified that an IRP has completed when the bus transactions associated with it have completed either successfully or due to errors.

If there are no IRPs pending or in progress for a pipe, the pipe is idle and the Host Controller will take no action with regard to the pipe; i.e., the endpoint for such a pipe will not see any bus transactions directed to it. The only time bus activity is present for a pipe is when IRPs are pending for that pipe.

If a non-isochronous pipe encounters a condition that causes it to send a STALL to the host (refer to Chapter 8) or three bus errors are encountered on any packet of an IRP, the IRP is aborted/retired, all outstanding IRPs are also retired, and no further IRPs are accepted until the software client recovers from the condition (in an implementation-dependent way) and acknowledges the halt or error condition via a USBD call. An appropriate status informs the software client of the specific IRP result for error versus halt (refer to Chapter 10). Isochronous pipe behavior is described in Section 5.6.

An IRP may require multiple data payloads to move the client data over the bus. The data payloads for such a multiple data payload IRP are expected to be of the maximum packet size until the last data payload that contains the remainder of the overall IRP. See the description of each transfer type for more details. For such an IRP, short packets (i.e., less than maximum-sized data payloads) on input that do not completely fill an IRP data buffer can have one of two possible meanings, depending upon the expectations of a client:

- A client can expect a variable-sized amount of data in an IRP. In this case, a short packet that does not fill an IRP data buffer can be used simply as an in-band delimiter to indicate "end of unit of data." The IRP should be retired without error and the Host Controller should advance to the next IRP.

- A client can expect a specific-sized amount of data. In this case, a short packet that does not fill an IRP data buffer is an indication of an error. The IRP should be retired, the pipe should be stalled, and any pending IRPs associated with the pipe should also be retired.

Because the Host Controller must behave differently in the two cases and cannot know on its own which way to behave for a given IRP, it is possible to indicate per IRP which behavior the client desires.

An endpoint can inform the host that it is busy by responding with NAK. NAKs are not used as a retire condition for returning an IRP to a software client. Any number of NAKs can be encountered during the processing of a given IRP. A NAK response to a transaction does not constitute an error and is not counted as one of the three errors described above.

### 5.3.2.1 Stream Pipes

Stream pipes deliver data in the data packet portion of bus transactions with no USB-required structure on the data content. Data flows in at one end of a stream pipe and out the other end in the same order. Stream pipes are always uni-directional in their communication flow.

Data flowing through a stream pipe is expected to interact with what the USB believes is a single client. The USB System Software is not required to provide synchronization between multiple clients that may be using the same stream pipe. Data presented to a stream pipe is moved through the pipe in sequential order: first-in, first-out.

A stream pipe to a device is bound to a single device endpoint number in the appropriate direction (i.e., corresponding to an IN or OUT token as defined by the protocol layer). The device endpoint number for the opposite direction can be used for some other stream pipe to the device.

Stream pipes support bulk, isochronous, and interrupt transfer types, which are explained in later sections.

#### 5.3.2.2 Message Pipes

Message pipes interact with the endpoint in a different manner than stream pipes. First, a request is sent to the USB device from the host. This request is followed by data transfer(s) in the appropriate direction. Finally, a Status stage follows at some later time. In order to accommodate the request/data/status paradigm, message pipes impose a structure on the communication flow that allows commands to be reliably identified and communicated. Message pipes allow communication flow in both directions, although the communication flow may be predominately one-way. The Default Control Pipe is always a message pipe.

The USB System Software ensures that multiple requests are not sent to a message pipe concurrently. A device is required to service only a single message request at a time per message pipe. Multiple software clients on the host can make requests via the Default Control Pipe, but they are sent to the device in a first-in, first-out order. A device can control the flow of information during the Data and Status stages based on its ability to respond to the host transactions (refer to Chapter 8 for more details).

A message pipe will not normally be sent the next message from the host until the current message's processing at the device has been completed. However, there are error conditions whereby a message transfer can be aborted by the host and the message pipe can be sent a new message transfer prematurely (from the device's perspective). From the perspective of the software manipulating a message pipe, an error on some part of an IRP retires the current IRP and all queued IRPs. The software client that requested the IRP is notified of the IRP completion with an appropriate error indication.

A message pipe to a device requires a single device endpoint number in both directions (IN and OUT tokens). The USB does not allow a message pipe to be associated with different endpoint numbers for each direction.

Message pipes support the control transfer type, which is explained in Section 5.5.

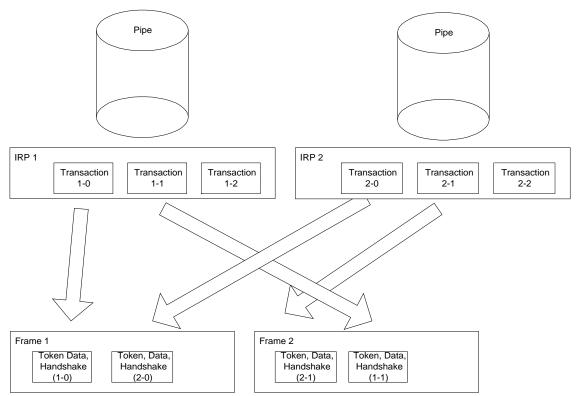

### 5.3.3 Frames and Microframes

USB establishes a 1 millisecond time base called a frame on a full-/low- speed bus and a 125µs time base called a microframe on a high-speed bus. A (micro)frame can contain several transactions. Transactions for different endpoints are allowed during a (micro)frame. Isochronous and interrupt endpoints are given opportunities to the bus every N (micro)frames. The values of N and other details about isochronous and interrupt transfers are described in Sections 5.6 and 5.7.

#### 5.4 Transfer Types

The USB transports data through a pipe between a memory buffer associated with a software client on the host and an endpoint on the USB device. Data transported by message pipes is carried in a USB-defined structure, but the USB allows device-specific structured data to be transported within the USB-defined message data payload. The USB also defines that data moved over the bus is packetized for any pipe (stream or message), but ultimately the formatting and interpretation of the data transported in the data payload of a bus transaction is the responsibility of the client software and function using the pipe. However, the USB provides different transfer types that are optimized to more closely match the service requirements of the client software and function using the pipe. An IRP uses one or more bus transactions to move information between a software client and its function.

Each transfer type determines various characteristics of the communication flow including the following:

- Data format imposed by the USB

- Direction of communication flow

- Packet size constraints

- Bus access constraints

- Latency constraints

- Required data sequences

- Error handling.

The designers of a USB device choose the capabilities for the device's endpoints. When a pipe is established for an endpoint, most of the pipe's transfer characteristics are determined and remain fixed for the lifetime of the pipe. Transfer characteristics that can be modified are described for each transfer type.

The USB defines four transfer types:

- Control Transfers: Bursty, non-periodic, host software-initiated request/response communication, typically used for command/status operations.

- Isochronous Transfers: Periodic, continuous communication between host and device, typically used for time-relevant information. This transfer type also preserves the concept of time encapsulated in the data. This does not imply, however, that the delivery needs of such data is always time-critical.

- Interrupt Transfers: Small-data, low-frequency, bounded-latency communication.

- Bulk Transfers: Non-periodic, large-packet bursty communication, typically used for data that can use any available bandwidth and can also be delayed until bandwidth is available.

Each transfer type is described in detail in the following four major sections. The data for any IRP is carried by the data field of the data packet as described in Section 8.4.3. Chapter 8 also describes details of the protocol that are affected by use of each particular transfer type.

### 5.5 Control Transfers

Control transfers allow access to different parts of a device. Control transfers are intended to support configuration/command/status type communication flows between client software and its function. A control transfer is composed of a Setup bus transaction moving request information from host to function, zero or more Data transactions sending data in the direction indicated by the Setup transaction, and a Status transaction returning status information from function to host. The Status transaction returns "success" when the endpoint has successfully completed processing the requested operation. Section 8.5.2 describes the details of what packets, bus transactions, and transaction sequences are used to accomplish a control transfer. Chapter 9 describes the details of the defined USB command codes.

Each USB device is required to implement the Default Control Pipe as a message pipe. This pipe is used by the USB System Software. The Default Control Pipe provides access to the USB device's configuration, status, and control information. A function can, but is not required to, provide endpoints for additional control pipes for its own implementation needs.

The USB device framework (refer to Chapter 9) defines standard, device class, or vendor-specific requests that can be used to manipulate a device's state. Descriptors are also defined that can be used to contain different information on the device. Control transfers provide the transport mechanism to access device descriptors and make requests of a device to manipulate its behavior.

Control transfers are carried only through message pipes. Consequently, data flows using control transfers must adhere to USB data structure definitions as described in Section 5.5.1.

The USB system will make a "best effort" to support delivery of control transfers between the host and devices. A function and its client software cannot request specific bus access frequency or bandwidth for control transfers. The USB System Software may restrict the bus access and bandwidth that a device may desire for control transfers. These restrictions are defined in Section 5.5.3 and Section 5.5.4.

### 5.5.1 Control Transfer Data Format

The Setup packet has a USB-defined structure that accommodates the minimum set of commands required to enable communication between the host and a device. The structure definition allows vendor-specific extensions for device specific commands. The Data transactions following Setup have a USB-defined structure except when carrying vendor-specific information. The Status transaction also has a USB-defined structure. Specific control transfer Setup/Data definitions are described in Section 8.5.2 and Chapter 9.

### 5.5.2 Control Transfer Direction

Control transfers are supported via bi-directional communication flow over message pipes. As a consequence, when a control pipe is configured, it uses both the input and output endpoint with the specified endpoint number.

### 5.5.3 Control Transfer Packet Size Constraints

An endpoint for control transfers specifies the maximum data payload size that the endpoint can accept from or transmit to the bus. The USB defines the allowable maximum control data payload sizes for full-speed devices to be<del>either</del> 8, 16, 32, or 64 bytes. <u>The only allowable maximum control data payload size for high-speed devices is 64 bytes</u>. Low-speed devices are limited to only an <u>eight byte8-byte</u> maximum data payload size. This maximum applies to the data payloads of the Data packets following a Setup; i.e., the size specified is for the data field of the packet as defined in Chapter 8, not including other information that is required by the protocol. A Setup packet is always eight bytes. A control pipe (including the Default Control Pipe) always uses its *wMaxPacketSize* value for data payloads.

An endpoint reports in its configuration information the value for its maximum data payload size. The USB does not require that data payloads transmitted be exactly the maximum size; i.e., if a data payload is less than the maximum, it does not need to be padded to the maximum size.

All Host Controllers are required to have support for 8-, 16-, 32-, and 64-byte maximum data payload sizes for full-speed control endpoints and only eight byteendpoints, only 8-byte maximum data payload sizes for low-speed control endpoints, and only 64-byte maximum data payload size for high-speed control endpoints. No Host Controller is required to support larger or smaller maximum data payload sizes.

In order to determine the maximum packet size for the Default Control Pipe, the USB System Software reads the device descriptor. The host will read the first eight bytes of the device descriptor. The device always responds with at least these initial bytes in a single packet. After the host reads the initial part of the device descriptor, it is guaranteed to have read this default pipe's *wMaxPacketSize* field (byte 7 of the device descriptor). It will then allow the correct size for all subsequent transactions. For all other control endpoints, the maximum data payload size is known after configuration so that the USB System Software can ensure that no data payload will be sent to the endpoint that is larger than the supported size. The host will always use a maximum data payload size of at least eight bytes.

An endpoint must always transmit data payloads with a data field less than or equal to the endpoint's *wMaxPacketSize* (refer to Chapter 9). When a control transfer involves more data than can fit in one data payload of the currently established maximum size, all data payloads are required to be maximum-sized except for the last data payload, which will contain the remaining data.

The Data stage of a control transfer from an endpoint to the host is complete when the endpoint does one of the following:

• Has transferred exactly the amount of data specified during the Setup stage

• Transfers a packet with a payload size less than *wMaxPacketSize* or transfers a zero-length packet.

When a Data stage is complete, the Host Controller advances to the Status stage instead of continuing on with another data transaction. If the Host Controller does not advance to the Status stage when the Data stage is complete, the endpoint halts the pipe as was outlined in Section 5.3.2. If a larger-than-expected data payload is received from the endpoint, the IRP for the control transfer will be aborted/retired.

The Data stage of a control transfer from the host to an endpoint is complete when all of the data has been transferred. If the endpoint receives a larger-than-expected data payload from the host, it halts the pipe.

### 5.5.4 Control Transfer Bus Access Constraints

Control transfers can be used by high-speed, full-speed and low-speed USB devices.

An endpoint has no way to indicate a desired bus access frequency for a control pipe. The USB balances the bus access requirements of all control pipes and the specific IRPs that are pending to provide "best effort" delivery of data between client software and functions.

The USB requires that part of each <u>(micro-)</u>frame be reserved to be available for use by control transfers as follows:

- If the control transfers that are attempted (in an implementation-dependent fashion) consume less than 10% of the frame time for low-speed/full-speed endpoints or less than 20% of a microframe for high-speed endpoints, the remaining time can be used to support bulk transfers (refer to Section 5.8).

- A control transfer that has been attempted and needs to be retried can be retried in the current or a future frame; i.e., it is not required to be retried in the same frame.

- If there are more control transfers than reserved time, but there is additional frame time that is not being used for isochronous or interrupt transfers, a Host Controller may move additional control transfers as they are available.

- If there are too many pending control transfers for the available frame time, control transfers are selected to be moved over the bus as appropriate.

- If there are control transfers pending for multiple endpoints, control transfers for the different endpoints are selected according to a fair access policy that is Host Controller implementation-dependent.

- A transaction of a control transfer that is frequently being retried should not be expected to consume an unfair share of the bus time.

These requirements allow control transfers between host and devices to be regularly moved over the bus with "best effort."

<u>The USB System Software Thecan, at its discretion, vary the</u> rate of control transfers to a particular endpoint can be varied by the USB System Software endpoint. at its discretion. An endpoint and its client software cannot assume a specific rate of service for control transfers. A control endpoint may see zero or more transfers in a single frame. Bus time made available to a software client and its endpoint can be changed as other devices are inserted into and removed from the system or also as control transfers are requested for other device endpoints.

The bus frequency and (micro-)frame timing limit the maximum number of successful control transfers within a (micro-)frame for any USB system. For full/low-speed buses, the number of successful control transfers per frame is limited to less than 29 full-speed eight-byte data payloads or less than four low-speed eight-byte data payloads. For high-speed buses, the number of control transfers is limited to less than 20 high-speed 64-byte data payloads per microframe. Table 5-1 lists information about different-sized full-speed control transfers and the maximum number of transfers possible in a frame. This table was generated assuming that there is one Data stage transaction and that the Data stage has a zero-length status phase. The table illustrates the possible power of two data payloads less than or equal to the allowable maximum data payload sizes. The table does not include the overhead associated with bit stuffing.

|   | Protocol        | Overhead (45 bytes)             |                                       | Setup data byt   | 6 Endpoint + C<br>es, and a 7-byte |                            |

|---|-----------------|---------------------------------|---------------------------------------|------------------|------------------------------------|----------------------------|

|   | Data<br>Payload | Max Bandwidth<br>(bytes/second) | Frame<br>Bandwidth<br>per<br>Transfer | Max<br>Transfers | Bytes<br>Remaining                 | Bytes/Frame<br>Useful Data |

|   | 1               | 32000                           | 3%                                    | 32               | 23                                 | 32                         |

|   | 2               | 62000                           | 3%                                    | 31               | 43                                 | 62                         |

|   | 4               | 120000                          | 3%                                    | 30               | 30                                 | 120                        |

|   | 8               | 224000                          | 4%                                    | 28               | 16                                 | 224                        |

|   | 16              | 384000                          | 4%                                    | 24               | 36                                 | 384                        |

|   | 32              | 608000                          | 5%                                    | 19               | 37                                 | 608                        |

|   | 64              | 832000                          | 7%                                    | 13               | 83                                 | 832                        |

| x |                 | 1500000                         |                                       |                  |                                    | 1500                       |

| Table 5-1. Full-speed Control Transfer L |

|------------------------------------------|

|------------------------------------------|

The 10% frame reservation for non-periodic transfers means that in a system with bus time fully allocated, all full-speed control transfers in the system contend for a nominal three control transfers per frame. Because the USB system uses control transfers for configuration purposes in addition to whatever other control transfers other client software may be requesting, a given software client and its function should not expect to be able to make use of this full bandwidth for its own control purposes. Host Controllers are also free to determine how the individual bus transactions for specific control transfers are moved over the bus within and across frames. An endpoint could see all bus transactions for a control transfer within the same frame or spread across several noncontiguous frames. A Host Controller, for various implementation reasons, may not be able to provide the theoretical maximum number of control transfers per frame.

For high-speed endpoints, the 20% microframe reservation for non-periodic transfers means that all high speed control transfers are contending for nominally eight control transfers per microframe. High-speed control transfers contend for microframe time along with split-transactions (see Section <11.TBD>> for more information about split transactions) for full- and low- speed control transfers. Both full-speed and low-speed control transfers contend for the same available frame time. However, high-speed control transfers can occur simultaneously with full- and low-speed control transfers. Low-speed control transfers simply take longer to transfer. Table 5-2 lists information about different-sized low-speed packets and the maximum number of packets possible in a frame. The table does not include the overhead associated with bit stuffing. For both speeds, because a control transfer is composed of several packets, the packets can be spread over several frames to spread the bus time required across several frames.

| Protocol        | Overhead (46 byte              | s)                                 |                  |                    |                            |

|-----------------|--------------------------------|------------------------------------|------------------|--------------------|----------------------------|

| Data<br>Payload | Max Bandwidth<br>(Approximate) | Frame<br>Bandwidth<br>per Transfer | Max<br>Transfers | Bytes<br>Remaining | Bytes/Frame<br>Useful Data |

| 1               | 3000                           | 25%                                | 3                | 46                 | 3                          |

| 2               | 6000                           | 26%                                | 3                | 43                 | 6                          |

| 4               | 12000                          | 27%                                | 3                | 37                 | 12                         |

| 8               | 24000                          | 29%                                | 3                | 25                 | 24                         |

|                 | 187500                         |                                    |                  |                    | 187                        |

**Error! Reference source not found.** <u>lists information about different-sized high-speed control transfers</u> and the maximum number of transfers possible in a microframe. This table was generated assuming that there is one Data stage transaction and that the Data stage has a zero-length status stage. The table illustrates the possible power of two data payloads less than or equal to the allowable maximum data payload sizes. The table does not include the overhead associated with bit stuffing.

Table 5-3. High-speed Control Transfer Limits

Protocol Overhead <<Based on 480Mb/s and 80 bit bus gap, 640 bit bus turnaround, 16 bit sync, 8 bit EOP: 9 PID bytes, 6 endpoint+CRC5 bytes, 6 CRC16 bytes, 8 SETUP data bytes, 64 request bytes, 9\*(2+1) sync/eop bytes, 3\*10 gap bytes, 3\*80 bus turn bytes>>

|     | <u>Data</u><br>Payload | <u>Max Bandwidth</u><br>(Approximate) | <u>Frame</u><br><u>Bandwidth</u><br>per Transfer | <u>Max</u><br><u>Transfers</u> | <u>Bytes</u><br><u>Remaining</u> | <u>Bytes/Frame</u><br><u>Useful Data</u> |

|-----|------------------------|---------------------------------------|--------------------------------------------------|--------------------------------|----------------------------------|------------------------------------------|

|     | <u>1</u>               |                                       |                                                  |                                |                                  |                                          |

|     | <u>16</u>              |                                       |                                                  |                                |                                  |                                          |

|     | <u>32</u>              |                                       |                                                  |                                |                                  |                                          |

| _   | <u>64</u>              |                                       |                                                  | <u>20</u>                      |                                  |                                          |

| Max |                        |                                       |                                                  |                                |                                  |                                          |

<u>High-speed control OUT endpoints must support the PING flow control protocol.</u> The details of this protocol are described in Section 8.5.1.

# 5.5.5 Control Transfer Data Sequences

Control transfers require that a Setup bus transaction be sent from the host to a device to describe the type of control access that the device should perform. The Setup transaction is followed by zero or more control Data transactions that carry the specific information for the requested access. Finally, a Status transaction

completes the control transfer and allows the endpoint to return the status of the control transfer to the client software. After the Status transaction for a control transfer is completed, the host can advance to the next control transfer for the endpoint. As described in Section 5.5.4, each control transaction and the next control transfer will be moved over the bus at some Host Controller implementation-defined time.

The endpoint can be busy for a device-specific time during the Data and Status transactions of the control transfer. During these times when the endpoint indicates it is busy (refer to Chapter 8 and Chapter 9 for details), the host will retry the transaction at a later time.

If a Setup transaction is received by an endpoint before a previously initiated control transfer is completed, the device must abort the current transfer/operation and handle the new control Setup transaction. A Setup transaction should not normally be sent before the completion of a previous control transfer. However, if a transfer is aborted, for example, due to errors on the bus, the host can send the next Setup transaction prematurely from the endpoint's perspective.

After a halt condition is encountered or an error is detected by the host, a control endpoint is allowed to recover by accepting the next Setup PID; i.e., recovery actions via some other pipe are not required for control endpoints. For the Default Control Pipe, a device reset will ultimately be required to clear the halt or error condition if the next Setup PID is not accepted.

The USB provides robust error detection and recovery/retransmission for errors that occur during control transfers. Transmitters and receivers can remain synchronized with regard to where they are in a control transfer and recover with minimum effort. Retransmission of Data and Status packets can be detected by a receiver via data retry indicators in the packet. A transmitter can reliably determine that its corresponding receiver has successfully accepted a transmitted packet by information returned in a handshake to the packet. The protocol allows for distinguishing a retransmitted packet from its original packet except for a control Setup packet. Setup packets may be retransmitted due to a transmission error; however, Setup packets cannot indicate that a packet is an original or a retried transmission.

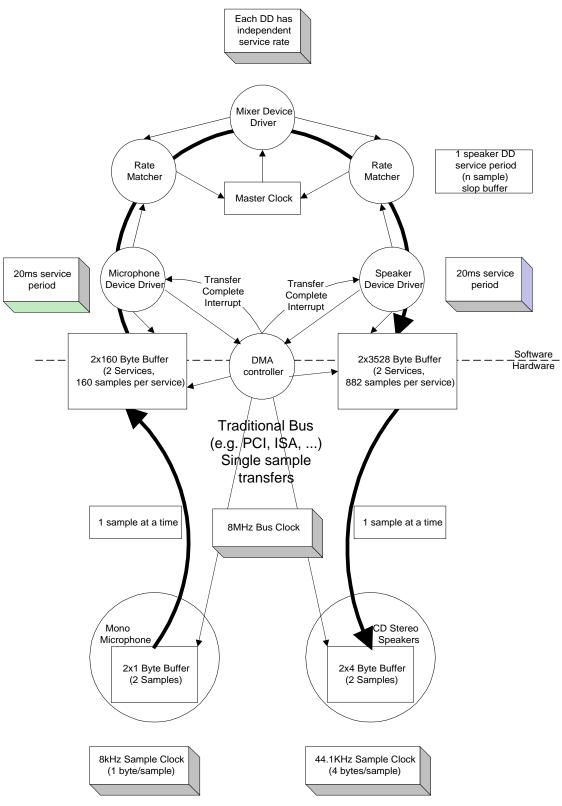

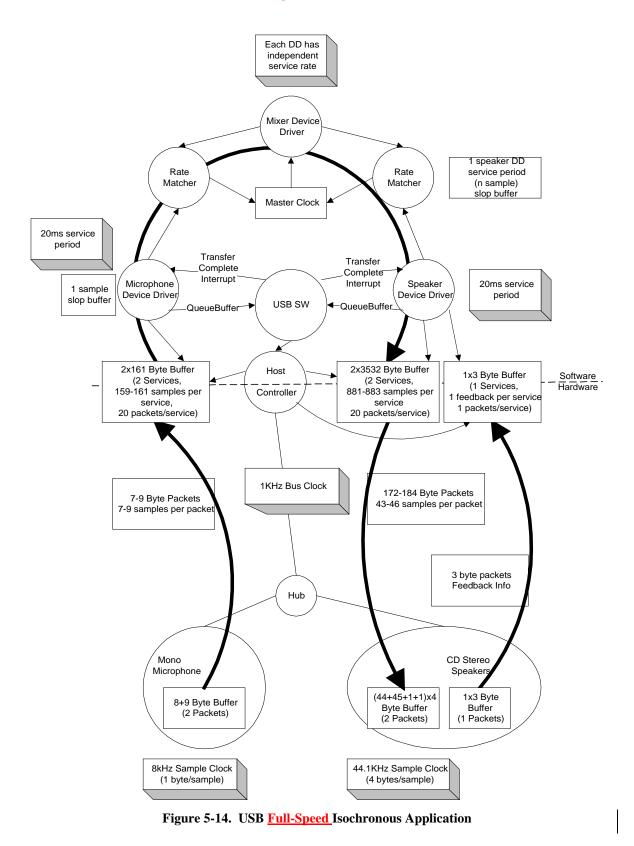

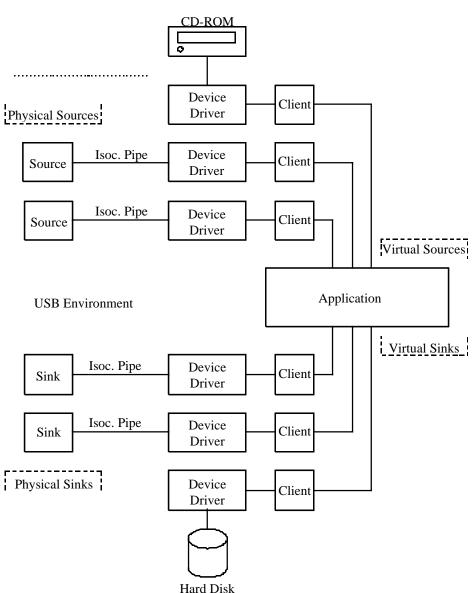

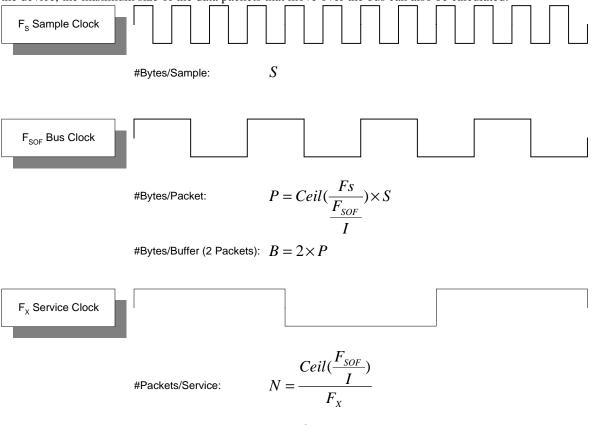

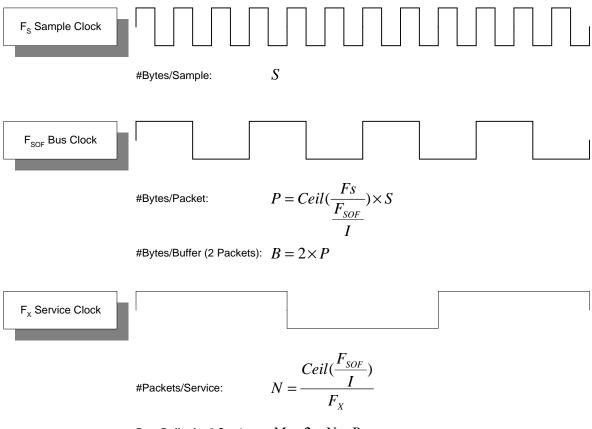

#### 5.6 Isochronous Transfers

In non-USB environments, isochronous transfers have the general implication of constant-rate, errortolerant transfers. In the USB environment, requesting an isochronous transfer type provides the requester with the following:

- Guaranteed access to USB bandwidth with bounded latency

- Guaranteed constant data rate through the pipe as long as data is provided to the pipe

- In the case of a delivery failure due to error, no retrying of the attempt to deliver the data.

While the USB isochronous transfer type is designed to support isochronous sources and destinations, it is not required that software using this transfer type actually be isochronous in order to use the transfer type. Section 5.12 presents more detail on special considerations for handling isochronous data on the USB.

### 5.6.1 Isochronous Transfer Data Format

The USB imposes no data content structure on communication flows for isochronous pipes.

### 5.6.2 Isochronous Transfer Direction

An isochronous pipe is a stream pipe and is, therefore, always uni-directional. An endpoint description identifies whether a given isochronous pipe's communication flow is into or out of the host. If a device requires bi-directional isochronous communication flow, two isochronous pipes must be used, one in each direction.

### 5.6.3 Isochronous Transfer Packet Size Constraints

An endpoint in a given configuration for an isochronous pipe specifies the maximum size data payload that it can transmit or receive. The USB System Software uses this information during configuration to ensure that there is sufficient bus time to accommodate this maximum data payload in each (micro-) frame. If there is sufficient bus time for the maximum data payload, the configuration is established; if not, the configuration is not established. The USB System Software does not adjust the maximum data payload size for an isochronous pipe as is the case for a control pipe. An isochronous pipe can simply either be supported or not supported in a given USB system configuration.

The USB limits the maximum data payload size to 1,023 bytes for each <u>full-speed</u> isochronous <u>pipe.endpoint</u>. <u>High-speed endpoints are allowed up to 1024-byte data payloads</u>. <u>High-speed</u>, <u>high</u> <u>bandwidth endpoints are allowed up to three transactions per microframe</u>. Table 5-1 lists information about different-sized <u>full-speed</u> isochronous transactions and the maximum number of transactions possible in a frame. The table does not include the overhead associated with bit stuffing.

| P | Protocol        | Overhead (9 bytes) | (2 SYNC bytes, bytes, and a 1-b    |                  |                    | C bytes, 2 CRC             |

|---|-----------------|--------------------|------------------------------------|------------------|--------------------|----------------------------|

| F | Data<br>Payload | Max<br>Bandwidth   | Frame<br>Bandwidth<br>per Transfer | Max<br>Transfers | Bytes<br>Remaining | Bytes/Frame<br>Useful Data |

|   | 1               | 150000             | 1%                                 | 150              | 0                  | 150                        |

|   | 2               | 272000             | 1%                                 | 136              | 4                  | 272                        |

|   | 4               | 460000             | 1%                                 | 115              | 5                  | 460                        |

|   | 8               | 704000             | 1%                                 | 88               | 4                  | 704                        |

|   | 16              | 960000             | 2%                                 | 60               | 0                  | 960                        |

|   | 32              | 1152000            | 3%                                 | 36               | 24                 | 1152                       |

|   | 64              | 1280000            | 5%                                 | 20               | 40                 | 1280                       |

|   | 128             | 1280000            | 9%                                 | 10               | 130                | 1280                       |

|   | 256             | 1280000            | 18%                                | 5                | 175                | 1280                       |

|   | 512             | 1024000            | 35%                                | 2                | 458                | 1024                       |

|   | 1023            | 1023000            | 69%                                | 1                | 468                | 1023                       |

|   |                 | 1500000            |                                    |                  |                    | 1500                       |

**Error! Reference source not found.** <u>lists information about different-sized high-speed isochronous</u> transactions and the maximum number of transactions possible in a microframe. The table does not include the overhead associated with bit stuffing.

|             | Protocol               | <u>Overhead</u>         | < <based 480mb="" 640="" 80="" and="" bit="" bus="" bus<br="" gap,="" on="" s="">turnaround, 16 bit sync, 8 bit EOP, 80% of 7500 byte<br/>microframe: 2 PID bytes, 2 endpoint+CRC5 bytes, 2<br/>bytes, 1 data byte, 2*(2+1) sync/eop bytes, 2*10 gap<br/>bus turn bytes&gt;&gt;</based> |                                | <u>00 byte</u><br>bytes, 2 CRC16 |                                          |

|-------------|------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------|------------------------------------------|

|             | <u>Data</u><br>Payload | <u>Max</u><br>Bandwidth | <u>Frame</u><br><u>Bandwidth</u><br>per Transfer                                                                                                                                                                                                                                        | <u>Max</u><br><u>Transfers</u> | <u>Bytes</u><br><u>Remaining</u> | <u>Bytes/Frame</u><br><u>Useful Data</u> |

|             | 1                      |                         |                                                                                                                                                                                                                                                                                         | <u>182</u>                     |                                  |                                          |

|             |                        |                         |                                                                                                                                                                                                                                                                                         |                                |                                  |                                          |

|             |                        |                         |                                                                                                                                                                                                                                                                                         |                                |                                  |                                          |

|             |                        |                         |                                                                                                                                                                                                                                                                                         |                                |                                  |                                          |

|             |                        |                         |                                                                                                                                                                                                                                                                                         |                                |                                  |                                          |

|             |                        |                         |                                                                                                                                                                                                                                                                                         |                                |                                  |                                          |

|             |                        |                         |                                                                                                                                                                                                                                                                                         |                                |                                  |                                          |

|             |                        |                         |                                                                                                                                                                                                                                                                                         |                                |                                  |                                          |

|             |                        |                         |                                                                                                                                                                                                                                                                                         |                                |                                  |                                          |

| <u>/lax</u> |                        |                         |                                                                                                                                                                                                                                                                                         |                                |                                  |                                          |

#### Table 5-3. Isochronous Transaction Limits for High-speed Endpoints

Any given transaction for an isochronous pipe need not be exactly the maximum size specified for the endpoint. The size of a data payload is determined by the transmitter (client software or function) and can vary as required from transaction to transaction. The USB ensures that whatever size is presented to the Host Controller is delivered on the bus. The actual size of a data payload is determined by the data transmitter and may be less than the prenegotiated maximum size. Bus errors can change the actual packet size seen by the receiver. However, these errors can be detected by either CRC on the data or by knowledge the receiver has about the expected size for any transaction.

A high-speed device must have its default configuration specify any iosochronous endpoints as requiring a zero data payload size via *wMaxPacketSize*. Alternate configurations (or interface settings) may specify non-zero data payload sizes. If the isochronous endpoints have a large data payload size, it is recommended that additional alternate configurations or interface settings be used to specify a range of data payload sizes. This increases the chances that the device can be used successfully in combination with other USB devices.

# 5.6.4 Isochronous Transfer Bus Access Constraints

Isochronous transfers can be used <u>by</u> only<del>by</del> full-speed <u>and high-speed</u> devices.

The USB requires that no more than 90% of any frame be allocated for periodic (isochronous and interrupt) transfers for full-speed endpoints. High-speed endpoints can allocate only 80% of a microframe for periodic transfers.

An isochronous endpoint must specify its required bus access period. High-speed endpoints can specify a desired period between  $1x125\mu$ s to  $(2^N)x125\mu$ s, where N is less than or equal to 16 << TBD >>. This allows high-speed isochronous transfers to have rates slower than one transaction per microframe. However, an isochronous endpoint must be prepared to handle poll rates higher than the one specified. It must return a zero-length packet whenever data is requested at a different interval than the specified interval. This allows a high-speed endpoint to move up to 3072 bytes per microframe (or 192Mb/s). A high-speed endpoint that requires more than 1024 bytes per microframe must specify a period of 1 (e.g. a *bInterval* value of 0). See Section 5.9 for more information about the details of multiple transactions per microframe for high bandwidth high-speed endpoints.

An endpoint for an isochronous pipe does not include information about bus access frequency. All isochronous pipes normally move exactly one data packet each frame (i.e., every 1ms). Errors on the bus or delays in operating system scheduling of client software can result in no packet being transferred for a frame. (micro-)frame. An error indication should be returned as status to the client software in such a case. A device can also detect this situation by tracking SOF tokens and noticing two SOF tokens without an intervening data packet for an isochronous endpoint. a disturbance in the specified bus access period pattern.

The bus frequency and frame timing limit the maximum number of successful isochronous transactions within a <u>(micro-)</u>frame for any USB system to less than 151 full-speed one-byte data <u>payloads and less than</u> 182 high-speed one-byte data payloads. A Host Controller, for various implementation reasons, may not be able to provide the theoretical maximum number of isochronous transactions per <u>(micro-)</u>frame.

#### 5.6.5 Isochronous Transfer Data Sequences

Isochronous transfers do not support data retransmission in response to errors on the bus. A receiver can determine that a transmission error occurred. The low-level USB protocol does not allow handshakes to be returned to the transmitter of an isochronous pipe. Normally, handshakes would be returned to tell the transmitter whether a packet was successfully received or not. For isochronous transfers, timeliness is more important than correctness/retransmission, and given the low error rates expected on the bus, the protocol is optimized by assuming transfers normally succeed. Isochronous receivers can determine whether they missed data during a (micro-) frame. Also, a receiver can determine how much data was lost. Section 5.12 describes these USB mechanisms in more detail.

An endpoint for isochronous transfers never halts because there is no handshake to report a halt condition. Errors are reported as status associated with the IRP for an isochronous transfer, but the isochronous pipe is not halted in an error case. If an error is detected, the host continues to process the data associated with the next (<u>micro-</u>)frame of the transfer. <u>LimitedOnly limited</u> error detection is possible because the protocol for isochronous transactions does not allow per-transaction handshakes.

#### 5.7 Interrupt Transfers

The interrupt transfer type is designed to support those devices that need to send or receive small amounts of data infrequently, but with bounded service periods. Requesting a pipe with an interrupt transfer type provides the requester with the following:

- Guaranteed maximum service period for the pipe

- Retry of transfer attempts at the next period, in the case of occasional delivery failure due to error on the bus.

#### 5.7.1 Interrupt Transfer Data Format

The USB imposes no data content structure on communication flows for interrupt pipes.

### 5.7.2 Interrupt Transfer Direction

An interrupt pipe is a stream pipe and is therefore always uni-directional. An endpoint description identifies whether a given interrupt pipe's communication flow is into or out of the host.

### 5.7.3 Interrupt Transfer Packet Size Constraints

An endpoint for an interrupt pipe specifies the maximum size data payload that it will transmit or receive. The maximum allowable interrupt data payload size is 64 bytes or less for full-speed. <u>High-speed endpoints</u> are allowed maximum data payload sizes up to 1024 bytes. A high speed, high bandwidth endpoint specifies whether it requires two or three transactions per microframe. Low-Low-speed devices are limited to eight bytes or less maximum data payload size. This maximum applies to the data payloads of the data packets; i.e., the size specified is for the data field of the packet as defined in Chapter 8, not including other protocol-required information. The USB does not require that data packets be exactly the maximum size; i.e., if a data packet is less than the maximum, it does not need to be padded to the maximum size.

All Host Controllers are required to have support for up to 64-byte maximum data payload sizes for fullspeed interrupt <u>endpoints and endpoints</u>, eight bytes or less maximum data payload sizes for low-speed interrupt <u>endpoints</u>, and three 1024 byte data payloads or less for high-speed interrupt endpoints. See Section 5.9 for more information about the details of multiple transactions per microframe for high <u>bandwidth high-speed</u> endpoints. No Host Controller is required to support larger maximum data payload sizes.

The USB System Software determines the maximum data payload size that will be used for a interrupt pipe during device configuration. This size remains constant for the lifetime of a device's configuration. The USB System Software uses the maximum data payload size determined during configuration to ensure that there is sufficient bus time to accommodate this maximum data payload in its assigned period. If there is sufficient bus time, the pipe is established; if not, the pipe is not established. The USB System Software does not adjust the bus time made available to an interrupt pipe as is the case for a control pipe. An interrupt pipe can simply either be supported or not supported in a given USB system configuration. However, the actual size of a data payload is still determined by the data transmitter and may be less than the maximum size.

An endpoint must always transmit data payloads with a data field less than or equal to the endpoint's *wMaxPacketSize* value. A device can move data via an interrupt pipe that is larger than *wMaxPacketSize*. A software client can accept this data via an IRP for the interrupt transfer that requires multiple bus transactions without requiring an IRP-complete notification per transaction. This can be achieved by specifying a buffer that can hold the desired data size. The size of the buffer is a multiple of *wMaxPacketSize* with some remainder. The endpoint must transfer each transaction except the last as *wMaxPacketSize* and the last transaction is the remainder. The multiple data transactions are moved over the bus at the period established for the pipe.

When an interrupt transfer involves more data than can fit in one data payload of the currently established maximum size, all data payloads are required to be maximum-sized except for the last data payload, which will contain the remaining data. An interrupt transfer is complete when the endpoint does one of the following:

- Has transferred exactly the amount of data expected

- Transfers a packet with a payload size less than *wMaxPacketSize* or transfers a zero-length packet.

When an interrupt transfer is complete, the Host Controller retires the current IRP and advances to the next IRP. If a data payload is received that is larger than expected, the interrupt IRP will be aborted/retired and the pipe will stall future IRPs until the condition is corrected and acknowledged.

<u>A high-speed device must have its default configuration specify any interrupt endpoints as requiring a zero data payload size via *wMaxPacketSize*. Alternate configurations (or interface settings) may specify non-zero data payload sizes. If the interrupt endpoints have a large data payload size, it is recommended that</u>

additional alternate configurations or interface settings be used to specify a range of data payload sizes. This increases the chances that the device can be used sucessfully in combination with other USB devices.

### 5.7.4 Interrupt Transfer Bus Access Constraints

Interrupt transfers can be used by full speed and low speed<u>full-speed</u>, low-speed, and high-speed devices. <u>High-speed endpoints must not require more than 80% of a microframe for periodic transfers</u>.

The USB requires that no more than 90% of any frame be allocated for periodic (isochronous and interrupt) <u>full/low-speed</u> transfers.

The bus frequency and <u>(micro-)</u>frame timing limit the maximum number of successful interrupt transactions within a <u>(micro-)</u>frame for any USB system to less than 108 full-speed one-byte data payloads or 14 low-speed one-byte data <u>payloads or to less than 62 high-speed one-byte data</u> payloads. A Host Controller, for various implementation reasons, may not be able to provide the above maximum number of interrupt transactions per <u>(micro-)</u>frame.

Table 5-4 lists information about different sized full speedhigh-speed interrupt transactions and the maximum number of transactions possible in a frame. <u>Table 5-5 lists similar information for full-speed</u> interrupt transactions. Table 5-6 lists similar information for low-speed interrupt transactions. The tables do not include the overhead associated with bit stuffing.

### Table 5-4. High-speed Interrupt Transaction Limits

|           | Protocol               | <u>Overhead</u>         | turnaround, 16<br>microframe: 3                  | <u>bit sync, 8 bit</u><br>PID bytes, 2 (<br>1 data byte, 3 |                                  | <u>500 byte</u><br>bytes, 2              |

|-----------|------------------------|-------------------------|--------------------------------------------------|------------------------------------------------------------|----------------------------------|------------------------------------------|

|           | <u>Data</u><br>Payload | <u>Max</u><br>Bandwidth | <u>Frame</u><br><u>Bandwidth</u><br>per Transfer | <u>Max</u><br><u>Transfers</u>                             | <u>Bytes</u><br><u>Remaining</u> | <u>Bytes/Frame</u><br><u>Useful Data</u> |

|           | <u>1</u>               |                         |                                                  | <u>62</u>                                                  |                                  |                                          |

|           |                        |                         |                                                  |                                                            |                                  |                                          |

|           |                        |                         |                                                  |                                                            |                                  |                                          |

|           |                        |                         |                                                  |                                                            |                                  |                                          |

|           |                        |                         |                                                  |                                                            |                                  |                                          |

|           |                        |                         |                                                  |                                                            |                                  |                                          |

|           |                        |                         |                                                  |                                                            |                                  |                                          |

| <u>ax</u> |                        |                         |                                                  |                                                            |                                  |                                          |

Ma

| Protocol        | Overhead (13 bytes) | (3 SYNC bytes<br>CRC bytes, and    |                  | 2 Endpoint + C<br>erpacket delay) | RC bytes, 2                |

|-----------------|---------------------|------------------------------------|------------------|-----------------------------------|----------------------------|

| Data<br>Payload | Max<br>Bandwidth    | Frame<br>Bandwidth<br>per Transfer | Max<br>Transfers | Bytes<br>Remaining                | Bytes/Frame<br>Useful Data |

| 1               | 107000              | 1%                                 | 107              | 2                                 | 107                        |

| 2               | 200000              | 1%                                 | 100              | 0                                 | 200                        |

| 4               | 352000              | 1%                                 | 88               | 4                                 | 352                        |

| 8               | 568000              | 1%                                 | 71               | 9                                 | 568                        |

| 16              | 816000              | 2%                                 | 51               | 21                                | 816                        |

| 32              | 1056000             | 3%                                 | 33               | 15                                | 1056                       |

| 64              | 1216000             | 5%                                 | 19               | 37                                | 1216                       |

|                 | 1500000             |                                    |                  |                                   | 1500                       |

#### 4<u>Table 5-5</u>. Full-speed Interrupt Transaction Limits

An endpoint for an interrupt pipe specifies its desired bus access period. A full-speed endpoint can specify a desired period from 1ms to 255ms. Low-speed endpoints are limited to specifying only 10ms to 255ms. High-speed endpoints can specify a desired period from 1x125µs to (2^N)x125µs, where N is less than or equal to 16. The USB System Software will use this information during configuration to determine a period that can be sustained. The period provided by the system may be shorter than that desired by the device up to the shortest period defined by the USB (1ms).(125µs microframe or 1ms frame). The client software and device can depend only on the fact that the host will ensure that the time duration between two transaction attempts with the endpoint will be no longer than the desired period. Note that errors on the bus can prevent an interrupt transaction from being successfully delivered over the bus and consequently exceed the desired period. Also, the endpoint is only polled when the software client has an IRP for an interrupt transfer pending. If the bus time for performing an interrupt transfer arrives and there is no IRP pending, the endpoint will not be given an opportunity to transfer data at that time. Once an IRP is available, its data will be transferred at the next allocated period.

| Protocol        | Overhead (13 byte              | s)                                 |                  |                    |                            |

|-----------------|--------------------------------|------------------------------------|------------------|--------------------|----------------------------|

| Data<br>Payload | Max Bandwidth<br>(Approximate) | Frame<br>Bandwidth<br>per Transfer | Max<br>Transfers | Bytes<br>Remaining | Bytes/Frame<br>Useful Data |

| 1               | 13000                          | 7%                                 | 13               | 5                  | 13                         |

| 2               | 24000                          | 8%                                 | 12               | 7                  | 24                         |

| 4               | 44000                          | 9%                                 | 11               | 0                  | 44                         |