# PCI2040 EVM Hardware Guide

# User's Guide

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

### **Preface**

# **Read This First**

#### About This Manual

This manual is provided to assist the developer in designing the PCI2040 in a system which incorporates a DSP-PCI bridge controller.

#### How to Use This Manual

This document contains the following chapters:

Chapter 1, *Introduction*, lists the key features of the PCI2040 evaluation module (EVM) and provides functional overviews of the EVM hardware and software.

Chapter 2, *Getting Started*, explains how to get started using the EVM. It provides step-by-step hardware and software installation instructions.

Chapter 3, *Running the Board Confidence Test*, explains how to run the board Confidence Test included with the PCI2040 EVM board.

Chapter 4, *PCI2040 EVM Hardware*, describes the EVM hardware, its key components and how they operate, and its various interfaces. Detailed programmer interface information such as memory maps, register definitions, and interrupt usage are also provided.

Chapter 5, *EVM Confidence Test*, describes the automated command line utility that enables the user to verify proper installation and operation of the board.

Chapter 6, *Host CPLD Registers*, describes the five host CPLD registers that are mapped into the PCI2040's GP bus address space.

Chapter 7, DSP CPLD Registers, describes the eight DSP CPLD registers that are mapped into the DSP's lower I/O address space.

Chapter 8, *Jumper Definitions*, describes the pinout information for connectors J4 through J10.

### Related Documentation From Texas Instruments

PCI2040 DSP-PCI Bridge Controller Data Manual

PCI2040 EVM Software Guide

### Trademarks

TI is a trademark of Texas Instruments Incorporated.

<sup>†</sup> Texas Instruments Customer Response Center

# **Contents**

| 1 | Introd | duction                                      | 1-1  |

|---|--------|----------------------------------------------|------|

|   | 1.1    | Key Features                                 | 1-2  |

|   |        | 1.1.1 User Control and Indicators            | 1-2  |

|   |        | 1.1.2 External Interfaces                    | 1-3  |

|   | 1.2    | The PCI2040 EVM Board                        | 1-4  |

|   | 1.3    | Hardware Functional Overview                 | 1-5  |

|   | 1.4    | Software Functional Overview                 | 1-7  |

| 2 | Gettir | ng Started                                   | 2-1  |

|   | 2.1    | Before Starting the Installation Process     |      |

|   |        | 2.1.1 Controlling Static Electricity         |      |

|   |        | 2.1.2 Avoiding Obstructions to the EVM Board |      |

|   | 2.2    | EVM Hardware Installation                    | 2-3  |

|   | 2.3    | EVM Software Installation                    | 2-4  |

| 3 | Runn   | ing the Board Confidence Test                | 3-1  |

|   | 3.1    | About the Board Confidence Test              | 3-2  |

|   | 3.2    | Verifying the EVM Installation               | 3-3  |

| 4 | PCI20  | 040 EVM Hardware                             | 4-1  |

|   | 4.1    | PCI Interface                                | 4-2  |

|   | 4.2    | Clocks                                       | 4-5  |

|   | 4.3    | Logic                                        | 4-7  |

|   | 4.4    | JTAG Emulation                               | 4-9  |

|   | 4.5    | Digital Signal Processor                     | 1-10 |

|   | 4.6    | External Memory                              | 1-12 |

|   | 4.7    | Stereo Audio Interface                       | 1-13 |

|   | 4.8    | Expansion Interfaces                         | 1-15 |

|   | 4.8.1  | Expansion Memory Interface                   | 1-15 |

|   | 4.8.2  | Expansion Peripheral Interface               | 1-16 |

|   | 4.8.3  | Daughterboard                                | 1-17 |

|   | 4.8.4  | Compatibility with C6x EVM Daughterboards    | 1-18 |

|   | 4.9    | Power Supplies                               |      |

|   | 4.10   | User Options and Indicators                  | 1-22 |

| 5 | EVM    | Confidence Test                              | 5-1  |

|   | 5.1    | EVM Confidence Test                          | 5-2  |

|     |                                                  | 0.4 |

|-----|--------------------------------------------------|-----|

|     | lost CPLD Registers                              |     |

| 6.  | 3 (                                              |     |

| 6.  | .2 Host STAT Register (Offset 0x84)              |     |

| 6.  | .3 Host REV Register (Offset 0x88)               | 6-5 |

| 6.  | .4 Host SEM0 Register (Offset 0x8C)              | 6-6 |

| 6.  | .5 Host SEM1 Register (Offset 0x90)              | 6-7 |

| 7 D | PSP CPLD Registers                               | 7-1 |

|     | .1 DSP CNTL Register (I/O Address 0)             |     |

| 7.  | .2 DSP STAT Register (I/O Address 1)             | 7-4 |

| 7.  | .3 DSP DMCTRL Register (I/O Address 2)           |     |

| 7.  | .4 DSP DBIO Register (I/O Address 3)             |     |

| 7.  | .5 DSP CCTRL Register (I/O Address 4)            |     |

| 7.  | .6 DSP CCLK Control Register (I/O Address 5)     | 7-9 |

| 7.  | .7 DSP SEM0 Register (I/O Address 6)             |     |

| 7.  | .8 DSP SEM1 Register (I/O Address 7)             |     |

| 8 C | Connector Definitions                            | 8-1 |

| 8.  |                                                  |     |

| 8.  | .2 CPLD ISR Header Connector (J5)                |     |

| 8.  | .3 Mictor Logic Analyzer Header Connector (J6)   |     |

| 8.  | .4 Expansion Memory Interface Connector (J7)     |     |

| 8.  | .5 Expansion Peripheral Interface Connector (J8) |     |

| 8.  | .6 DSP JTAG Emulation Header Connector (J9)      |     |

| 8.  | .7 External Power Connector (J10)                |     |

# **Figures**

| 1–1 | PCI2040 EVM Block Diagram                      | 1-5  |

|-----|------------------------------------------------|------|

|     | EVM Host Software Block Diagram                |      |

|     | PCI2040 Interfaces on EVM                      |      |

| 4–2 | EVM Clocks                                     | 4-5  |

| 4–3 | Daughterboard Envelopes and Connections on EVM | 4-18 |

| 4–4 | External Power Connector                       | 4-21 |

# **Tables**

| 4–1  | EVM PCI Memory-Mapped Regions                      | . 4-4 |

|------|----------------------------------------------------|-------|

| 4–2  | DSPs McBSP Allocation on EVM                       | 4-10  |

| 4–3  | DSPs Interrupt Allocation                          | 4-11  |

| 4–4  | Daughterboard Access Address Ranges                | 4-15  |

| 4–5  | User Option DIP Switches                           | 4-22  |

| 4–6  | Clock Mode Switch Selections                       | 4-22  |

| 4–7  | EVM Jumper Options                                 | 4-23  |

| 4–8  | EVM User Indicators                                | 4-23  |

| 5–1  | Board Confidence Test Utility Command Parameters   | . 5-2 |

| 6–1  | Host CPLD Register Definitions                     | . 6-2 |

| 6–2  | Host CNTL Register Bit Definitions                 | . 6-3 |

| 6–3  | Host STAT Register Bit Definitions                 | . 6-4 |

| 6–4  | Host REV Register Bit Definitions                  | . 6-5 |

| 6–5  | Host SEM0 Register Bit Definitions                 | . 6-6 |

| 6–6  | Host SEM1 Register Bit Definitions                 | . 6-7 |

| 7–1  | DSP CPLD Register Definitions                      | . 7-2 |

| 7–2  | DSP CNTL Register Bit Definitions                  | . 7-3 |

| 7–3  | DSP STAT Register Bit Definitions                  | . 7-4 |

| 7–4  | DSP DMCTRL Register Bit Definitions                | . 7-6 |

| 7–5  | DSP DBIO Register Bit Definitions                  | . 7-7 |

| 7–6  | DSP CCTRL Register Bit Definitions                 | . 7-8 |

| 7–7  | Codec De-Emphasis Selection                        | . 7-8 |

| 7–8  | DSP CCLK Register Bit Definitions                  | . 7-9 |

| 7–9  | Codec Sample Rate Selection                        | 7-10  |

| 7–10 | DSP SEM0 Register Bit Definitions                  | 7-11  |

| 7–11 | DSP SEM1 Register Bit Definitions                  | 7-12  |

| 8–1  | Codec Digital Interface Connector J4 Pinout        | . 8-2 |

| 8–2  | CPLD ISR Connector J5 Pinout                       | . 8-3 |

| 8–3  | Mictor Logic Analyzer Header Connector J6 Pinout   | . 8-4 |

| 8–4  | Expansion Memory Interface Connector J7 Pinout     | . 8-6 |

| 8–5  | Expansion Peripheral Interface Connector J8 Pinout |       |

| 8–6  | DSP JTAG Emulation Header Connector J9 Pinout      | 8-10  |

| 8–7  | External Power Connector J10 Pinout                | 8-11  |

|      |                                                    |       |

# **Chapter 1**

# Introduction

This chapter lists the key features of the PCI2040 evaluation module (EVM) and provides functional overviews of the EVM hardware and software.

The PCI2040 EVM is a low-cost, general-purpose platform for the evaluation of the PCI2040 PCI-to-DSP bridge and the development, analysis, and testing of C54x digital signal processor (DSP) algorithms and applications. The EVM allows you to develop applications that interface with the PCI2040 that run on both a host PC and the C54x DSP to determine if they meet your application requirements. The EVM hardware design information and software application programming interfaces (APIs) also provide a reference design that facilitates your own PCI2040 hardware and software development.

The EVM is bundled with software support software that includes a debugger, Windows 95/98 and NT 4.0 device drivers, host PC and DSP software APIs, example applications with source code, and various utility applications. This hardware/software bundle provides an integrated package that allows you to quickly evaluate the PCI2040 and C54x DSP devices and develop applications.

| -   | С                            | Page                                                                                                            |

|-----|------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 1.1 | Key Features                 | 1-2                                                                                                             |

| 1.2 | The PCI2040 EVM Board        | 1-4                                                                                                             |

| 1.3 | Hardware Functional Overview | 1-5                                                                                                             |

| 1.4 | Software Functional Overview | 1-7                                                                                                             |

|     | 1.2<br>1.3                   | 1.1 Key Features  1.2 The PCI2040 EVM Board  1.3 Hardware Functional Overview  1.4 Software Functional Overview |

# 1.1 Key Features

|       | Th               | e PCI2040 EVM bundle has the following key features:                    |

|-------|------------------|-------------------------------------------------------------------------|

|       |                  | PCI2040 PCI-to-DSP bridge                                               |

|       |                  | 3.3-V/5-V, PCI Local Bus Specification Revision 2.2-Compliant Interface |

|       |                  | 100 MHz TMS320VC5410 DSP (100 MIPS)                                     |

|       |                  | 64 kW Internal SRAM                                                     |

|       |                  | 64 kW Program SRAM                                                      |

|       |                  | 64 kW Data SRAM                                                         |

|       |                  | Stereo 8-96 kHz, 16-bit Audio (TI's TLC320AD77C)                        |

|       |                  | Microphone & Line In/Out Interfaces                                     |

|       |                  | JTAG Debugging via PCI Bus or XDS510 Emulator                           |

|       |                  | Memory & Peripheral Expansion Connectors                                |

|       |                  | Support for 32-bit C6x Daughterboards                                   |

|       |                  | PCI Status and User-Defined LEDs                                        |

|       |                  | Code Composer Studio Debugging Support (driver provided)                |

|       |                  | Windows and DSP Drivers, APIs, and Utilities                            |

|       |                  | Plug and Play Device                                                    |

|       |                  | PCI2040 PCI-to-DSP Reference Design                                     |

| 1.1.1 | User Control and | d Indicators                                                            |

|       | Th               | e PCI2040 EVM has the following user controls and indicators:           |

|       |                  | JTAG Emulation (embedded or external)                                   |

|       |                  | Clock Mode Selection (CLKMD1-3)                                         |

|       |                  | Microprocessor/Microcomputer Mode Selection (MP/MC)                     |

|       |                  | Hot Swap Insert/Eject Control                                           |

|       |                  | HPI/Daughterboard Boot Selection                                        |

|       |                  | Two User-Defined Switches                                               |

|       |                  | Line Input Level Selection (1-V/2-Vrms)                                 |

|       |                  | Line Output Filtering Selection                                         |

|       |                  | Manual Reset                                                            |

|       | П                | Power-On LED                                                            |

|       |                   | D3 Status LED                                                                           |

|-------|-------------------|-----------------------------------------------------------------------------------------|

|       |                   | Power Management Event (PME) Status LED                                                 |

|       |                   | ENUM Status LED                                                                         |

|       |                   | Hot Swap Status LED                                                                     |

|       |                   | User-Defined LED                                                                        |

| 1.1.2 | External Interfac | ces                                                                                     |

|       | Th                | e PCI2040 C54x EVM has the following external interfaces:                               |

|       |                   | PCI Local Bus Specification Revision 2.2-Compliant Interface (3.3-V/5-V 32-bit, 33 MHz) |

|       |                   | 14-pin External JTAG Header                                                             |

|       |                   | Three 3.5-mm Audio Jacks (line in, line out, and microphone)                            |

|       |                   | Two Low-Profile 80-pin (0.050-inch) Daughterboard Connectors                            |

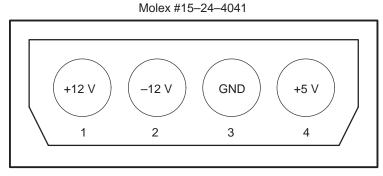

|       |                   | Molex 4-pin External Power Connector (5V, 12V, -12V, and GND)                           |

### 1.2 The PCI2040 EVM Board

The EVM is a short PCI board with approximate dimensions of 4.2 inches wide, 8.66 inches long, and 0.45 inch high. The EVM is intended for use in a PCI expansion slot on your computer's motherboard. The EVM can be operated stand-alone on a desktop with the use of an external power supply and XDS510 or XDS510WS emulator. The power supply and emulator required for stand-alone operation are not included since this board is intended for PCI evaluation purposes.

#### Note:

Make sure that there is an unobstructed slot open for the PCI card. See Section 2.1.2, *Avoiding Obstructions to the EVM Board*, for more information.

The EVM has a 5410 DSP onboard that enables full-speed verification of C54x code with the included source debugger. The EVM provides a PCI interface, external memory, an audio codec, and embedded JTAG emulation support. Connectors on the EVM provide the DSP's external memory interfaces and peripheral signals that enable its functionality to be expanded with custom or third-party daughterboards.

The EVM provides a PCI2040 hardware reference design that can assist you in the development of your own PCI2040-based products. In addition to providing a reference for interfacing the PCI2040 to various devices, it also provides a reference for interfacing the 5410 DSP to other devices.

#### 1.3 Hardware Functional Overview

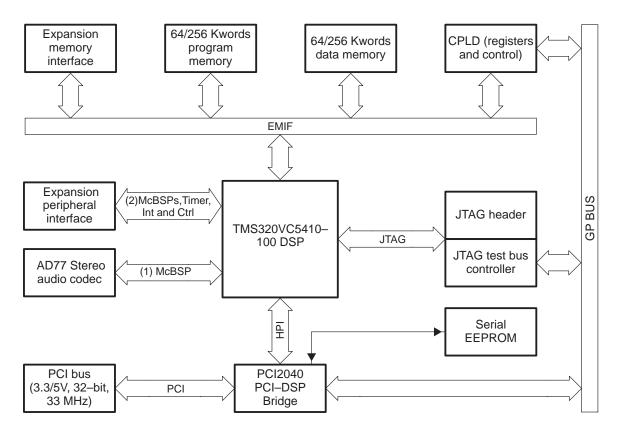

Figure 1–1 shows the basic functional block diagram of the EVM.

Figure 1–1. PCI2040 EVM Block Diagram

The EVM hardware can be divided into ten functional areas. This section provides an overview of each of these ten areas. Detailed descriptions are provided in Chapter 4, *PCI2040 EVM Hardware*.

- □ PCI Interface. The EVM is a PCI target device that is compliant with PCI Local Bus Specification, Revision 2.2. The PCI interface is provided by the PCI2040 PCI-to-DSP bridge which provides a glueless interface to the DSP's host port interface (HPI), JTAG test bus controller (TBC), and programmable logic. The PCI interface is target-only, meaning that all communications are initiated by a PCI bus master. For more information, see Section 4.1, PCI Interface.

- ☐ Clocks. The EVM provides onboard clocks for the JTAG TBC, DSP, CPLD, and audio codec. For more information, see Section 4.2, *Clocks*.

- ☐ Logic. The EVM provides logic for user control over the board from both the host and DSP. For more information, see Section 4.3, *Logic*.

- JTAG Emulation. The EVM provides embedded JTAG emulation using an onboard JTAG TBC, as well as a header to support an XDS510 JTAG emulator. This allows source debugging over the PCI bus without requiring

### 1.4 Software Functional Overview

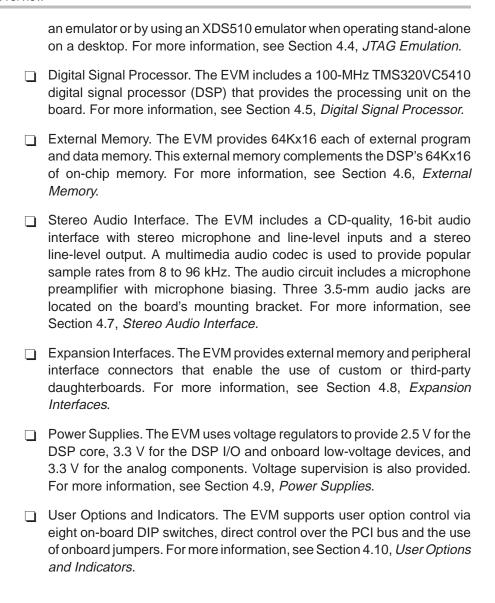

The EVM software support consists of host support software and DSP support software. The host software supplied with the EVM includes the following host utilities and libraries:

| C source debugger (emu54x.exe). The debugger software tools help you debug 'C54x software on the board.                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EVM board reset utility (evmrst.exe). This utility resets the board.                                                                                                                                                                                     |

| EVM confidence test utility (evmtest.exe). This utility tests the basic operation of the board.                                                                                                                                                          |

| EVM board control utility (evmctrl.exe). This utility performs various control and status operations with the board.                                                                                                                                     |

| EVM COFF loader utility (evmload.exe). This utility loads and executes 'C54x software on the board.                                                                                                                                                      |

| EVM Win32 DLL (pci2040.dll). The Win32 host libraries consist of a user-mode dynamic linked library (DLL) that supports Windows 95, Windows 98, and Windows NT. This DLL provides user software access for control and communication with the EVM board. |

| Example source code. Example code that illustrates how to use the Win32 DLL functions is provided with the PCI2040 EVM.                                                                                                                                  |

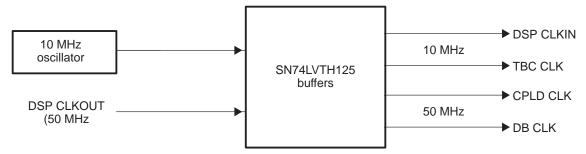

The host software supplied with an EVM board provides utilities to configure the board, to debug PCI2040 'C54x software on the board, to load and execute 'C54x software on the board, and to test the basic operation of the board. Also supplied with the EVM board is a Win32 dynamic link library (DLL) that provides user software access for control and communication with the EVM board. The host utilities and host libraries run on an Intel PC under either Windows 95, Windows 98, or Windows NT 4.0. Figure 1–2 provides a block diagram of the EVM host software components and their relationships.

The far left side of the figure shows the components involved in the C source debugger support. The TI C source debugger makes calls to the debugger SCIF component. The SCIF component calls the JTAG TBC API functions to perform emulation functions. The JTAG TBC API calls the low-level (Ring 0) Win 95 and NT drivers to access the JTAG TBC device on the EVM board.

The remainder of the figure shows the Win32 host utilities and the components they use to access the hardware. The Win32 applications call the Windows 95, Windows 98, or Windows NT DLL that implement a consistent Ring 3 API. These DLLs make calls to the Ring 0 drivers which provide access to the hardware.

Figure 1-2. EVM Host Software Block Diagram

The DSP support software developed for the EVM board includes the following components:

- ☐ Board support library (board.c and board.h). This library provides 'C54x board specific routines for EVM configuration and control.

- Codec library (codec.c and board.h). This library is a collection of routines that configures and controls the operation of the AD77 audio codec device.

- ☐ Example source code. Code examples are provided to demonstrate the use of the codec and board support functions.

# Chapter 2

# **Getting Started**

This chapter explains how to get started using the EVM. It provides step-by-step hardware and software installation instructions.

| Topic |     | age                                      |     |

|-------|-----|------------------------------------------|-----|

|       | 2.1 | Before Starting the Installation Process | 2-2 |

|       | 2.2 | EVM Hardware Installation                | 2-3 |

|       | 2.3 | EVM Software Installation                | 2-4 |

### 2.1 Before Starting the Installation Process

### 2.1.1 Controlling Static Electricity

To help avoid equipment damage, read and follow the instructions in the following sections for controlling static electricity and avoiding obstructions that could prevent you from installing your EVM.

Store the board in its anti-static bag until you are ready to use it.

Keep the anti-static bag for storing or transferring the board between computers.

☐ Wear a properly connected ground strap at all times when handling the EVM.

### 2.1.2 Avoiding Obstructions to the EVM Board

Before installing the EVM, make sure that your PC has an available PCI slot that does not have obstructions. In some computers, the location or height of the central processing unit (CPU) or the location of the PCI-bus slot may prevent you from installing the EVM. Possible obstructions include memory modules, processor fans, power supply circuits, and cable connections. Failure to avoid obstructions when installing the EVM could permanently damage the card.

### 2.2 EVM Hardware Installation

To install the EVM board into your PC, follow these steps:

- 1) Turn off your PC's power and unplug the power cord.

- 2) Remove the cover from your PC.

- 3) Locate an existing unused PCI slot. Make sure that this slot will allow the installation of the EVM card. If the slot is a shared ISA/PCI slot that shares mechanical space, then make sure that an ISA card is not already installed.

- 4) If installed, remove the PCI slot's cover from the back of the computer by unscrewing it from the chassis.

- 5) Remove the EVM from the anti-static bag.

- 6) Insert the EVM board into the empty PCI slot and secure its mounting bracket to the chassis with the previously removed screw. There are no jumpers or switches on the board that have to be set for PCI operation.

- 7) Replace the PC cover.

- 8) Connect the 3.5-mm audio cables to the EVM's microphone, line in, and line out connectors as needed. The connectors are labeled with the MIC IN, LINE IN, and LINE OUT designations. MIC IN is closest to the status LED at the top, LINE IN is in the middle, and LINE OUT is at the bottom.

- 9) Plug in the PC's power cord and turn on the power.

If your operating system is Windows NT, then the hardware installation is finished. Proceed to Section 2.3, *EVM Software Installation*. If your operating system is Windows 95 or 98, then please read the following information.

During system startup, the PC's PCI BIOS will automatically detect the presence of the EVM and Windows will prompt you for a driver disk. Insert the EVM support software CD-ROM and follow the instructions on the screen. After the driver is installed, reboot the PC. To install the EVM support software, proceed to Section 2.3, *EVM Software Installation*.

#### 2.3 EVM Software Installation

On most Windows 95 or NT 4.0 systems, setup will automatically start when the **PCI2040 Software** CD is loaded. However, if AutoPlay is not enabled on your system, then you will need to explicitly run the program setup.exe in the top-level directory of the CD. For example, you may do this in the following way:

- 1) Insert the PCI2040 Software CD in your CD-ROM drive.

- 2) Choose "Run..." from the Start Menu.

- 3) In the "Open:" box, type d:\setup, where d is the letter assigned to your CD-ROM drive.

- 4) Click OK and follow the instructions on the screen.

PATH=c:\pci2040;%path%

In Windows 95, this is set up in the autoexec.bat file.

In Windows NT, this is set up in the registry under:

HKEY\_CURRENT\_USER\ENVIRONMENT

If you choose not to have the installation program modify your environment, then you will need to modify it yourself. In addition to this modification of the PATH variable, you may wish to set up or modify other environment variables for your convenience in accessing files, setting code generation options, etc.

After you have completed installation of the EVM hardware and software, you should run the EVM confidence test to verify correct installation of the EVM hardware and software. This test is described in Section 5.1, *EVM Confidence Test*.

# Chapter 3

# Running the Board Confidence Test

This chapter explains how to run the board confidence test included with the PCI2040 EVM board. This test can only be run after the EVM board hardware and software has been successfully installed. Refer to Chapter 2 for installation instructions.

| Горіс |                                 | age |

|-------|---------------------------------|-----|

| 3.1   | About the Board Confidence Test | 3-2 |

| 3.2   | Verifying the EVM Installation  | 3-3 |

## 3.1 About the Board Confidence Test

|     | M board and its support software and displays board configuration prmation. The EVM hardware components tested include:                                                                                                                          |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Memory                                                                                                                                                                                                                                           |

|     | C54x interrupts                                                                                                                                                                                                                                  |

|     | Audio codec                                                                                                                                                                                                                                      |

|     | CPLD semaphores                                                                                                                                                                                                                                  |

|     | PCI controller and board LEDs                                                                                                                                                                                                                    |

|     | JTAG                                                                                                                                                                                                                                             |

| The | e installation of these EVM software components are tested:                                                                                                                                                                                      |

|     | Win32 DLL                                                                                                                                                                                                                                        |

|     | Host low-level board driver                                                                                                                                                                                                                      |

| ver | e following section explains how to run the board confidence test utility to ify that the board and software have been installed properly. For additional ormation about the confidence test utility, see Section 5.1, <i>EVM Confidence</i> st. |

The confidence test verifies proper operation of the major components of the

# 3.2 Verifying the EVM Installation

| lo     | in the board confidence test utility, follow these steps:                                                                                                                                                                                             |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | nstall the PCI2040 EVM board and software as described in Chapter 2 Getting Started.                                                                                                                                                                  |

|        | Open a command window and change directory to the conftest subdirectory of the EVM installation directory. This directory is created during the nstall process and contains additional files needed for the execution of the confidence test utility. |

|        | Execute the confidence test utility in a command window by entering the command line:                                                                                                                                                                 |

|        | evmtest test.log                                                                                                                                                                                                                                      |

|        | This command starts the confidence test utility for the first EVM boar<br>and logs the test results to the file test.log.                                                                                                                             |

| $\Box$ | The output from the confidence test will look similar to that below                                                                                                                                                                                   |

```

C:>evmtst test.log

PCI2040 'C54x EVM Confidence Test, Version 1.00

04:20:25 PM May 12, 1999

Board Index

Board Type

: PCI2040 'C54x EVM, Rev 0

Beginning Confidence Test ...

Testing Win32 DLL and Low-Level Driver access......PASSED.

CPLD Dump....

_____

CPLD Revision

Board Voltage

: GOOD

Board Reset

: NO

TBC Reset

: NO

DSPINT3

: NOT SET

NMI

: NOT SET

HINT2

: NOT PENDING

: SET

User Switch 1

User Switch 2

: SET

User LED

: OFF

DSP mode

: MICROCONTROLLER

Daughter board

: ABSENT

: NOT OWNED

User semaphore 0

: NOT OWNED

User semaphore 1

_____

***** PCI2040 Confidence Tests.

Observe the following PCI2040 LEDs

_____

PME LED......PASSED.

Toggle dip switch 6 to observe the Hot Swap Enum LED.....PASSED.

Hot Swap LED......PASSED.

***** JTAG Confidence Tests.

JTAG Test.....PASSED.

**** EVM Clock Confidence Tests.

**** EVM LED Confidence Tests.

DSP 0: Observe the user LED on the bracket blinking.....PASSED.

***** DSP Semaphore Confidence Tests.

DSP 0: Semaphore Test......PASSED.

***** DSP Interrupt Confidence Tests.

DSP 0: DSP-to-HOST Interrupt Tests......PASSED.

**** Memory Tests.

DSP 0: A5 Test Test: page 1: addr 0x8000: len 0x8000..PASSED.

DSP 0: WALK Test Test: page 1: addr 0x8000: len 0x8000..PASSED. DSP 0: ADDR Test Test: page 1: addr 0x8000: len 0x8000..PASSED.

DSP 0: PULSE Test Test: page 1: addr 0x8000: len 0x8000..PASSED.

DSP 0: A5 Test Test: page 2: addr 0x8000: len 0x8000..PASSED.

DSP 0: WALK Test Test: page 2: addr 0x8000: len 0x8000..PASSED.

DSP 0: ADDR Test Test: page 2: addr 0x8000: len 0x8000..PASSED.

DSP 0: PULSE Test Test: page 2: addr 0x8000: len 0x8000..PASSED.

***** Codec Confidence Tests.

DSP 0: Codec Right Channel Tone Test......PASSED.

DSP 0: Codec Left/Right Channel Tone Test......PASSED.

DSP 0: Codec Line In Loopback Test......PASSED.

DSP 0: Codec Mic In Loopback Test......PASSED.

***** PCI2040 'C54x EVM Confidence Test Complete......No Errors.

C:>

```

# Chapter 4

# PCI2040 EVM Hardware

This chapter describes the EVM hardware, its key components and how they operate, and its various interfaces. Detailed programmer interface information such as memory maps, register definitions, and interrupt usage are also provided.

The hardware can be divided into ten functional areas. Each of these functional areas is discussed in this chapter.

| Topic Pag |                             |      |

|-----------|-----------------------------|------|

| 4.1       | PCI Interface               | 4-2  |

| 4.2       | Clocks                      | 4-5  |

| 4.3       | Logic                       | 4-7  |

| 4.4       | JTAG Emulation              | 4-9  |

| 4.5       | Digital Signal Processor    | 4-10 |

| 4.6       | External Memory             | 4-12 |

| 4.7       | Stereo Audio Interface      | 4-13 |

| 4.8       | Expansion Interfaces        | 4-15 |

| 4.9       | Power Supplies              | 4-21 |

| 4.10      | User Options and Indicators | 4-22 |

### 4.1 PCI Interface

The EVM has a 3.3-V/5-V, 32-bit universal card edge connector which allows it to be used in PCI slots that use either 3.3-V or 5-V signaling. The PCI2040 PCI-to-DSP bridge controller provides a *PCI Local Bus Specification*, Revision 2.2 compliant interface on the EVM.

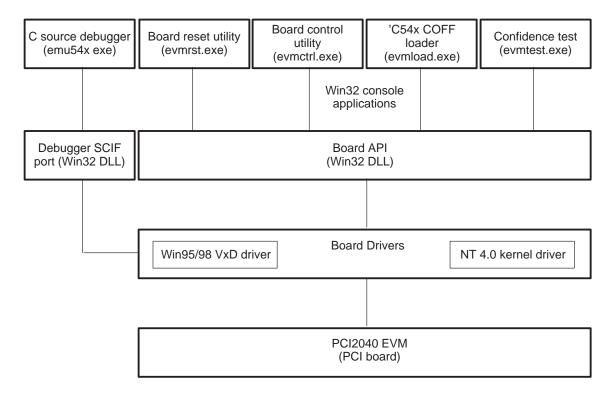

Figure 4–1 shows the interfaces of the PCI2040 on the EVM.

Figure 4-1. PCI2040 Interfaces on EVM

In addition to providing a direct interface to the PCI bus, the PCI2040 also interfaces to the following devices on the EVM board:

- ☐ Glueless connection to the DSP's 8-bit host port interface (HPI) that supports data transfers and host-DSP interrupt capabilities. Although the PCI2040 supports up to four DSPs, only one DSP is on the EVM board.

- Complex programmable logic device (CPLD) that provides EVM and board control and status features.

- JTAG test bus controller (TBC) to provide embedded JTAG debugging of the DSP.

- ☐ Serial EEPROM device that stores the PCI configuration of the EVM board such as subsystem vendor and ID.

- Hot swap switch and LEDs

The PCI2040 interfaces to the CPLD and TBC devices via its 16-bit general-purpose I/O (GPIO) bus that supports a memory space of up to 64

addresses. The serial EEPROM interface uses 2 of the PCI2040's GPIO signals (GPIO1 and GPIO0) that are used for the serial clock and data. The PCI2040 provides a dedicated input for a hot swap switch (cPCI ejector handle) and two outputs for status (HSENUM and HSLED) that connect to LEDs for display.

A 512-byte serial EEPROM (AT24C04N) is used on the EVM. The PCI2040 controller only requires the first 32 bytes, so 480 bytes are available for manufacturer and user data.

The PCI2040 controller supports up to four DSPs, but only one DSP is supported on the EVM board. The HPI control signals for the three unused DSP ports are not used (inputs are pulled high). However, the unused reset outputs (HRST3–HRST1) and the unused GPIO3 signal support JTAG programming of the onboard CPLD over the PCI bus. This enables customer and field upgrades of the board without special programming software and hardware.

The PCI2040 controller provides hot-swap capabilities that are intended for use on a CompactPCI platform. The PC's PCI support does not currently provide hot swap. However, the EVM provides control and monitoring of these capabilities through the use of a switch input and LED output. This enables the EVM to be used for evaluation of the PCI2040's hot swap capabilities in a PCI environment.

The PCI2040 controller is also compliant with the latest *PCI Bus Power Management Interface Specification*. The PCI2040 provides several low-power features that reduce power consumption. The EVM supports the PME (power management event) signal, but it is not connected to the PCI bus by default. The EVM does provide LED indications of the PME and D3 power states to support evaluation of the PCI2040's power management capabilities.

The EVM provides 0-ohm resistors and two-pin jumper headers to support current measurements of the PCI2040's core voltage and PCI/HPI clamping voltages.

The PCI2040 controller presents four memory-mapped regions to the EVM software as shown in Table 4–1. Software interacts with the EVM by dealing with these four memory regions. There are no I/O-mapped regions on the EVM board.

The GP bus region on the EVM is divided into 2 halves, with the lower 32 doubleword addresses dedicated to the JTAG TBC, and the upper 32 doubleword addresses dedicated to the CPLD. Each GP bus access must be a 16-bit WORD access, but on a doubleword boundary. The CPLD only uses the lower 8 bits, so they should be masked appropriately on reads.

The support software for the EVM handles all of the memory accessing, so most users do not need to deal with it directly. The 32-kbyte control space is divided into four 8-kbyte regions to address up to four DSPs. Since only one DSP is supported on the EVM, only the lower 4-kbyte region accesses the DSP's HPIA, HPIC, HPID, and HPID with address autoincrementing. Further details about the four memory regions are provided in the *PCI2040 Data Manual*.

Table 4-1. EVM PCI Memory-Mapped Regions

| Memory Region                 | Size (Bytes) |

|-------------------------------|--------------|

| PCI configuration registers   | 256          |

| HPI CSR registers             | 4 K          |

| Control space (HPI registers) | 32 K         |

| GP bus (TBC and CPLD)         | 256          |

The PCI2040 can interrupt the host PC using INTA whenever certain events occur including HPI error, GP Bus error, GPIO2 interrupt, JTAG TBC interrupt, or a DSP-to-host interrupt generated by with the DSP's HINT output. The EVM's software support provides interrupt masking and handling capabilities. The host can interrupt the DSP by writing setting the DSPINT bit in the DSP's HPI control register (HPIC).

The PCI2040 HPI and GP bus interfaces are brought out to an AMP Mictor (2-767004-2) connector for observation. Note that this connector is not installed on the production EVM board. Additionally, the GPIO signals are provided on a jumper header, with an option for selecting their levels on another jumper header. Note that these two jumper headers are not installed on the production EVM board.

#### 4.2 Clocks

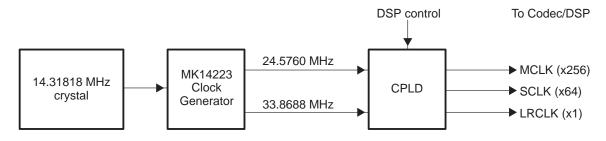

The PCI2040 controller gets its clock directly from the PCI bus, but the audio codec, JTAG TBC, DSP, and CPLD clocks are provided on the EVM. Figure 4–2 summarizes the clock generation and distribution on the EVM.

Figure 4–2. EVM Clocks

#### CODEC CLOCKS

#### OTHER CLOCKS

The audio codec requires 3 different clocks including a master clock (MCLK) that runs at 256 times the sample rate, a serial clock (SCLK) that runs at 64 times the sample rate, and a left/right clock that runs at the sample rate. MCLK is used internal to the codec for filtering and oversampling. SCLK is used by both the codec and DSP to transmit and receive the serial data streams between the 2 devices. Data is transmitted on the rising edge and sampled on the falling edge of SCLK. The LRCLK is the frame sync signal that indicates when the first bit of the serial data streams is valid. It is active high for one SCLK period.

In order to support the range of common multimedia audio sample rates, two different source clocks are needed. The MK14223 clock generator device is designed specifically for this task. It accepts a common 14.31818 MHz crystal input and produces the 24.576 and 33.688 MHz clocks that are required as audio codec source clocks. Under DSP control, the CPLD generates the MCLK, SCLK, and LRCLK signals by selecting the appropriate source clock and dividing it down as necessary.

A single 10 MHz oscillator is used as the source clock for the DSP and TBC, and indirectly for the CPLD and expansion peripheral (daughterboard) interface. An SN74LVTH125 quad buffer provides 5-V to 3.3-V translation and provide an acceptable edge rate. The DSP and TBC are provided with 10 MHz buffered clocks. The DSP's on-chip PLL can select a DSP operating clock rate in the range of 2.5 to 150 MHz. Since a 100 MHz DSP is used, the software defaults the DSP's internal clock to 100 MHz by setting the on-chip PLL to x10 mode. The JTAG TBC runs at 10 MHz, so the JTAG serial data is transmitted and received at 10 Mbps.

The DSP's CLKOUT signal is buffered by the other two SN74LVTH125 buffers to provide buffered clocks to the CPLD and daughterboard. The CPLD does not currently use this clock, but it is available for future use. The clock is made available to daughterboards for synchronization to the DSP bus rate. This can be useful for state machine clocks and the generation of hardware wait states. The 5410 DSP can generate a CLKOUT signal at a rate of 1, 1/2, 1/3, or 1/4 of its internal clock rate. By default, the EVM support software selects a 1/2-rate CLKOUT signal, so at 100 MHz, the clocks to the CPLD and daughterboard are 50 MHz.

### 4.3 Logic

The EVM uses fast, discrete TTL logic and a CPLD to provide memory decoding and glue logic functions on the board.

An SN74LVC32A quad-OR device provides fast memory decoding for the TBC and external memory. The PCI2040 controller can directly interface to the TBC device with no logic required. However, since the PCI2040's GP bus is shared between the TBC and the CPLD, minimal logic is required to decode between TBC and CPLD accesses. Simple decoding is performed based on the most-significant address bit on the GP Bus (GPA5). TBC accesses occur whenever a read or write occurs when GPA5 is low. CPLD accesses occur whenever a read or write occurs when GPA5 is high. Two of the four OR gates provide qualified RD/WR strobes to the TBC. The other two OR gates generate memory read and write enables for the daughterboard interface that are compatible with the C6x DSP.

A low-voltage Cypress CY37128VP CPLD provides the following functions on the EVM:

|          | Reset generation to DSP, daughterboard, and JTAG TBC      |

|----------|-----------------------------------------------------------|

|          | Host, DSP, and daughterboard interrupt control and status |

|          | Host registers mapped in PC's memory space                |

|          | DSP registers mapped in DSP's I/O space                   |

|          | Daughterboard data transceivers control                   |

|          | Daughterboard control signal generation                   |

| <b>-</b> | Codec clock generation                                    |

Reset signals can come from multiple sources including the PCI2040 controller, reset pushbutton, voltage supervisor, and under host and DSP software control. Logic manages all of these reset inputs and resets the appropriate devices.

There are also multiple interrupt sources from the host, DSP, and daughterboard that must be managed. Software can generate, enable, select, and poll various interrupts on the board by accessing CPLD registers.

The CPLD provides five, 8-bit registers that are mapped into the host's memory space starting at offset 0x80 of the GP bus memory region. The registers are aligned on 32-bit (doubleword) address boundaries (0x80, 0x84, ... 0x90). These registers provide board control and status, CPLD revision information, and two hardware semaphores that can be used for resource sharing or synchronization between the host and the DSP. Chapter 6, *Host CPLD Registers*, provides details on the CPLD's host registers.

The CPLD provides eight, 8-bit registers that are mapped into the DSP's I/O space from 0x00 to 0x07. These registers provide board control and status, data memory control, daughterboard general-purpose I/O, codec control and

clock selection, and two hardware semaphores shared with the host. Chapter 7, *DSP CPLD Registers*, provides details on the CPLD's DSP registers.

The CPLD controls the daughterboard interface including the generation of data transceiver enables and strobes and memory interface control signals. In order for the expansion memory interface to be compatible with existing daughterboards designed for the C6x, differences between C54x and C6x memory interface signals have to be resolved. The CPLD and logic mentioned earlier combine to handle this resolution. A registered transceiver is used on the upper 16 data lines of the expansion memory interface, so the CPLD controls the 16-to-32-bit and 32-to-16-bit conversions required for memory accesses to 32-bit daughterboards.

The CPLD also generates the clocks required by the audio codec and DSP to run the codec device and pass data between them. The CPLD includes multiple clock divisor circuits that provide 50% duty cycle clocks required for codec operation. Refer to the register definitions in Chapter 7, *DSP CPLD Registers*, for details on how the CPLD clocks are generated under DSP control.

### 4.4 JTAG Emulation

The EVM provides embedded JTAG emulation that is accessible via the PCI bus, as well as support for an external XDS510 emulator. The selected JTAG method is user-configurable via the DIP switches when the board is operated outside the PC, or via the software switches when it is in the PC.

The TI SN74ACT8990 JTAG test bus controller (TBC) provides memory-mapped control of the DSP's JTAG interface. This allows the C source debugger to be used with the EVM without an external emulator.

The EVMs embedded emulation support provides several benefits:

| _ | consumption of user resources.                                                                                    |

|---|-------------------------------------------------------------------------------------------------------------------|

|   | Easy access to the DSP supports high-level language (HLL) debuggers, factory testing, and field diagnostics.      |

|   | System boot ROMs are not needed. The host can download all necessary program and data through the emulation port. |

Emulation is supported without external cabling monitor software or

The TBC is presented to the PC host software as 24 memory-mapped registers. Each register is mapped at 32-bit (doubleword) address boundaries, but only the lower 16 bits of data words are connected to the 16-bit TBC device. The PCI2040 controller's GP bus accesses the TBC device's 24 registers in the lower half of the 256-byte GP bus memory region (0x00, 0x04, ... 0x5C).

A 14-pin (2 rows of 7 pins) header is included on the EVM to support an external XDS510 or XDS510WS emulator connection. This connection is required to use the EVM outside the PCI and may be used for debugging the EVM in the PC with the XDS510. Two TI CBT quad 2:1 multiplexer devices (SN74CBT3257) provide the +5-V to +3.3-V translation required from the TBC to the DSP, and the selection between internal and external JTAG emulation.

### 4.5 Digital Signal Processor

The 100 MHz TMS320VC5410 DSP is the processor used on the EVM. The 5410 provides a set of enhanced peripherals and functionality that were not available on previous members of the 54x family. The following is a list of key features of the 5410 DSP that differentiate it from previous 54x DSPs:

64K x 16-bit on-chip RAM

Enhanced HPI-8 with support for host access to all on-chip memory

Three multichannel buffered serial ports (McBSPs)

Six-channel direct memory access (DMA)

CLKOUT selection of 1, 1/2, 1/3, or 1/4 of the internal clock rate

Extended addressing of up to 8M x 16-bit memory

The 5410's ability to address a large address space and its three McBSP serial ports make it an ideal processor for this EVM since it can be compatible with C6x daughterboards.

The DSP can run in a variety of modes. The EVM hardware and software support provides you with the ability to use them. DIP switches can select the clock mode (CLKMD) and boot mode (MP/MC). A jumper is provided to select between booting from the HPI or from a daughterboard. DSP software library support provides software control over various operating parameters such as clock speed, bus rate, wait states, and memory map.

The PCI2040 controller interfaces directly to the DSP's HPI for data transfers and interrupt control. The host has access to all of the DSP's on-chip memory via the HPI. The DSP's JTAG interface can be connected directly to an XDS510 emulator or to the onboard JTAG TBC under user control for debugging.

The DSP's three McBSPs are allocated on the EVM as indicated in Table 4–2. The 5410 bootloader supports McBSP bootloading through McBSPs 0 and 2, so McBSP 1 was selected as the dedicated serial port for the audio codec.

Table 4–2. DSPs McBSP Allocation on EVM

| McBSP No. | Function                                |

|-----------|-----------------------------------------|

| 0         | Expansion peripheral interface (McBSP0) |

| 1         | AD77 audio codec                        |

| 2         | Expansion peripheral interface (McBSP1) |

The DSP has four external maskable interrupts (INT3-INT0) and one non-maskable interrupt (NMI). INT2 is used at boot time to indicate whether HPI booting should be performed. If INT2 is connected to HINT at boot time, then HPI boot is selected. A jumper is provided to make this selection. INT0 and INT1 are routed to the expansion peripheral interface, so a daughterboard can interrupt the DSP with these two interrupts. INT3 can be generated by

either the host or the daughterboard under DSP software selection. A  $\overline{\text{NMI}}$  interrupt can be generated by the host to the DSP. The DSP can mask this interrupt inside of the CPLD (it is not maskable in the DSP). Table 4–3 summarizes the DSP interrupt allocation.

Table 4–3. DSPs Interrupt Allocation

| Interrupt | Allocation                                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------|

| NMI       | Host-generated, DSP-maskable in CPLD                                                                  |

| ĪNT3      | Host or daughterboard-generated, DSP selects source in CPLD. Both sources can also be polled in CPLD. |

| INT2      | HPI boot select or daughterboard-generated (if not in HPI boot mode)                                  |

| INT1      | Daughterboard-generated                                                                               |

| INT0      | Daughterboard-generated                                                                               |

The DSPs HOLD and HOLDA are not used on the EVM. HOLD is pulled high.

The DSPs CLKIN is provided by a buffered 10 MHz oscillator. Software can control the frequency of the internal DSP (CPU) clock using the on-chip, programmable PLL to obtain internal clock rates from 2.5 to 150 MHz. The DSP's CLKOUT can be selected by the DSP software to be 1, 1/2, 1/3, or 1/4 of the internal DSP clock. All external memory accesses are relative to the CLKOUT frequency. The CLKOUT signal is provided to the CPLD and the expansion peripheral interface for daughterboard usage.

The DSPs timer output TOUT, and general-purpose input (BIO) and output (XF) are routed to the expansion peripheral connector for daughterboard usage.

### 4.6 External Memory

The EVM extends the 5410's 64k x 16 on-chip RAM with external memory consisting of 64k x 16 program memory and 64k x 16 data memory. Both of these memories could be upgraded to 256k x 16-bit devices since the layout supports them. The memories are 10-ns devices which support consecutive (CONSEC/=0) 50 MHz accesses and nonconsecutive 100 MHz accesses at 100 MHz with 0 wait states.

Page 0 of the external program memory can be mapped into the DSP's program memory space from 0x0000–0xBFFF if the DSP's OVLY bit is set to 0. If OVLY = 1, then external memory in Page 0 is only available from 0x8000–0xBFFF. The DSP's 16K x 16 ROM is always resident in the program memory space from 0xC000 to 0xFFFF. Extended pages of program memory access the external program memory in 64K-word pages if OVLY = 0 or 32K-word pages if OVLY = 1. Refer to the TMS320VC5410 data sheet for detailed memory maps. Onboard external program memory is accessed only when A22 is low. The daughterboard external program memory space is accessed when A22 is high.

The 5410 addresses external data memory only when the DSPs DROM bit is 0. External data memory is accessible only in a 32K x 16 window in data memory from 0x8000x–0xFFFF since the DSP does not have built-in extended data memory page support. However, the EVM's CPLD provides a data memory page selection register that supports extension of the data memory space to thirty-two 32K x 16 windows, for a total address space of 1M data memory words. Each window resides at 0x8000 in the data memory space. The EVM ships with a 64K x 16 memory device, so there are two external data memory pages available. The CPLD provides an additional data memory select (DMSEL) bit that determines if external data memory accesses are intended for the onboard memory or the daughterboard. When DMSEL = 0, onboard memory is accessed. When DMSEL = 1, daughterboard memory is accessed. The CPLD defaults DMSEL to 1 to support daughterboard parallel booting at reset.

#### 4.7 Stereo Audio Interface

The EVM includes a stereo audio interface that has the following characteristics:

☐ 16-bit stereo audio codec with sample rates from 8 kHz to 96 kHz

Support for stereo electric microphones with voltage bias

☐ Stereo line-level input

Stereo line-level output

☐ Three 3.5-mm (1/8-inch) stereo audio jacks

The TI TLC320AD77C stereo audio codec is a 24-bit codec which operates in 16-bit DSP mode. It is a delta-sigma codec that is designed for consumer applications that demand excellent audio performance. It is typically used in applications such a mini-disk players, audio/video receivers, musical instruments and other end-equipment requiring high-performance digital audio conversion.

The AD77 codec requires three clocks to be provided to it consisting of MCLK (x256), SCLK (x64) and LRCLK (x1), as described in detail in Section 4.2, *Clocks*. The conversion rate is defined by MCLK, the serial port shift clock is defined by SCLK, and the left/right frame synchronization is defined by LRCLK. As discussed earlier, the CPLD provides the necessary clocks to the codec. Additionally, the DSP software can enable and disable both the codec clocks and the codec itself with CPLD register bits.

The EVM provides support for the following popular sample rates (in kHz):

| 8.000   | 9.600  | 11.025 | 12.000 | 13.230 | 16.000 |

|---------|--------|--------|--------|--------|--------|

| 16.5375 | 22.050 | 24.000 | 32.000 | 33.075 | 44.100 |

| 48.000  | 66.150 | 96,000 |        |        |        |

The AD77 codec is connected to the DSP's McBSP1. Since clocks are provided by the DSP, the McBSP should be initialized for external clocks and frame syncs, with a data delay of 1. EVM support software provides DSP library functions that initialize and control the codec.

The industry-standard 3.5-mm stereo audio jacks are located on the board's mounting bracket. The tip of each jack is the left audio channel and the ring of each jack is the right audio channel. Mono connections only use the left channel.

TI TLV2462C op amps are used for the microphone preamplifier and filtering. A voltage bias is provided to support the use of battery-powered and electric microphones. Passive filtering is included on the EVM between the audio jacks and the codec for increased performance. Ferrite beads and capacitors are used on all audio interfaces to reduce noise coupling.

The microphone input is designed for electric microphones that require a bias voltage. A dynamic microphone can be used if capacitors block the bias

voltage. The maximum allowable signal level from the microphone is 500 mV (350 mVrms). There is a 10-dB preamplifier gain on the EVM.

The line input signal level can be a maximum of 6 Vpp (2 Vrms). The line input signal is attenuated 9 dB before it is presented to the codec. A jumper option can disable the 9 dB attenuation for maximum dynamic range with 1 Vrms or less signals.

The line output signal level can be a maximum of 1.9 Vpp (0.67 Vrms). The line output is designed to drive 10-kohm loads, not low-impedance headphones or speakers.

The DSP software can select either the microphone or line-level input for each of the channels (left/right) by controlling bits in a CPLD register. There are additional control bits to enable codec de-emphasis for 32, 44.1, and 48 kHz sample rates and the codec speed mode for greater than 48 kHz sample rates. Refer to Section 7.5 for details on the codec control register bits.

Additional filtering is required for 8 kHz operation due to the nature of the AD77's DAC output at this lower sample rate. The AD77 is specified to operate from 16 to 96 kHz. However, if the additional external filtering is enabled using a jumper option, then 8 kHz operation can be used without added noise from the DAC.

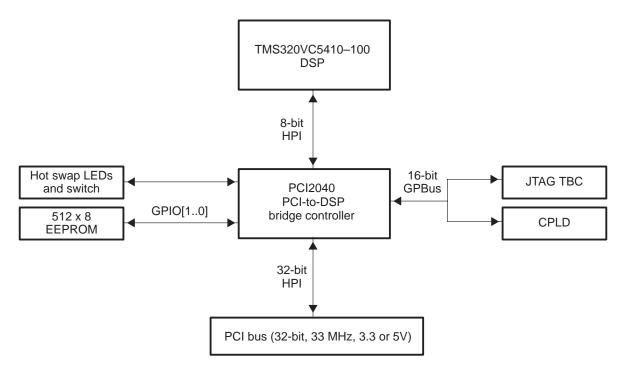

#### 4.8 Expansion Interfaces

The EVM provides two expansion connectors that allow a daughterboard to be connected to extend the capabilities of the board. Daughterboards can extend the capabilities of the EVM and provide custom and application-specific I/O. One expansion connector provides the DSP's memory interface and the other provides access to the DSPs peripherals and control/status signals. Both connectors also provide power to the daughterboard.

Most of the expansion connector signals are buffered so that the daughterboard cannot directly influence the operation of the EVM board. The use of TI 'LVTH and 'CBT interface devices allows the use of either 5- or 3.3-V devices to be used on the daughterboard.

Mating connectors for the 80-pin connectors on the EVM are available in four different heights; all of which meet the PCI height requirement. The recommended mating connector provides 0.465" spacing allowing sufficient space for components.

The expansion memory interface connector has a reference designator on the EVM of J7. The expansion peripheral interface connector is J8. Refer to Chapter 8 for the pinouts of the expansion connectors.

#### 4.8.1 Expansion Memory Interface

The expansion memory interface provides the DSP's memory interface signals to a daughterboard. External asynchronous memories and memory-mapped devices can be added to the EVM, including nonvolatile memory that can be used to boot the EVM upon reset.

The expansion memory interface includes:

□ Twenty-two external address signals (X\_A21-X\_A0). All of the DSPs external address signals, except A22, are available on the expansion memory interface, allowing up to 4M words of external program memory to be addressed. A22 is not provided since daughterboard program memory accesses are only valid when A22 is high. Similarly, daughterboard I/O accesses are only valid when A15 is high (1M I/O addresses), and data memory accesses are only valid when DMSEL is high (1M addresses). Table 4-4 summarizes the address ranges for daughterboard accesses from the DSP.

Table 4–4. Daughterboard Access Address Ranges

| Access  | Address Range       | Conditions                                        |

|---------|---------------------|---------------------------------------------------|

| Program | 0x400000 – 0x7FFFFF | A22 is high, DSPs XPC selects page                |

| Data    | 0x8000 – 0xFFFF     | DMSEL=1, DM_PG[40] selects 1 of 32, 32k pages     |

| I/O     | 0x8000 – 0xFFFF     | A15 is high, DM_PG[40] selects 1 of 32, 32k pages |

|                 |       | Thirty-two external data signals (X_D31-X_D0). All of the DSP's 16 external data signals, plus 16 additional data signals for 32-bit daughterboard compatibility, are available on the expansion memory interface.                                                                                                                                                                                                                               |

|-----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |       | Data memory space enable $(\overline{X}\_\overline{DS})$ . The DSP's data memory space enable is asserted only when DMSEL = 1 and the DSP asserts $\overline{DS}$ . This qualifies daughterboard data memory space accesses.                                                                                                                                                                                                                     |

|                 |       | Five asynchronous memory control signals. Asynchronous memory control signals that are from the DSP, or derived from DSP signals to provide C6x daughterboard compatibility, are available on the expansion memory interface. The signals include $\overline{X_RE}$ , $\overline{X_OE}$ , $\overline{X_MSTRB}$ , $\overline{X_WE}$ and $\overline{X_RDY}$ . $\overline{X_RDY}$ can be used by the daughterboard to control hardware wait states. |

|                 |       | Power Signals. The expansion memory interface also provides ground, 5-V, and 3.3-V power signals to the daughterboard.                                                                                                                                                                                                                                                                                                                           |

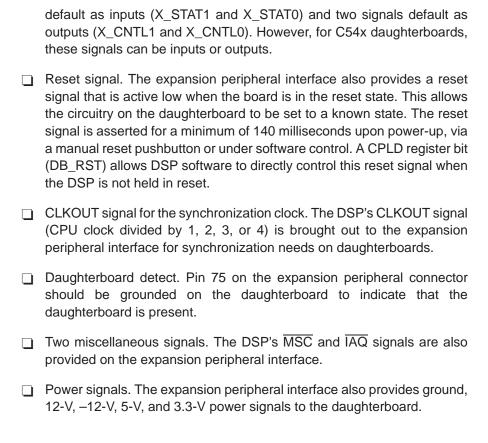

| 4.8.2 Expansion | Perip | heral Interface                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | a d   | e expansion peripheral interface provides the DSP's peripheral signals to aughterboard. This peripheral expansion capability allows serial devices thas other codecs and communication devices to be added to the EVM via aughterboard.                                                                                                                                                                                                          |

|                 | The   | e expansion peripheral interface includes:                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 |       | Six signals for each serial port. The DSP's six McBSP signals for McBSP0 and McBSP2 are available on the expansion peripheral interface (mapped to serial ports 0 and 1, respectively). These signals are buffered on the EVM to support both 5-V and 3.3-V serial devices. Each McBSP has CLKX, FSX, DX, XLKR, FSR, and DR signals.                                                                                                             |

|                 |       | Timer output signal. The DSP's timer output signal TOUT is available on the expansion peripheral interface.                                                                                                                                                                                                                                                                                                                                      |

|                 |       | Interrupts and interrupt acknowledge. The four external DSP interrupts ( $\overline{\text{INT0}}$ – $\overline{\text{INT3}}$ ), a DSP-to-daughterboard interrupt ( $\overline{\text{X}}$ _DBINT), and the DSP's interrupt acknowledge ( $\overline{\text{IACK}}$ ) are available on the expansion peripheral interface. Note that $\overline{\text{INT2}}$ is only available if it is not used on the EVM as the HPI boot indicator.             |

|                 |       | DSP general-purpose I/O signals. The DSP's XF and $\overline{\mbox{BIO}}$ signals are available on the expansion peripheral connector.                                                                                                                                                                                                                                                                                                           |

|                 |       | Three asynchronous memory control signals. Asynchronous memory control signals that are from the DSP are available on the expansion memory interface. The signals include $\overline{X}$ -PS, $\overline{X}$ -IS, and $\overline{X}$ -IOSTRB.                                                                                                                                                                                                    |

|                 |       | Four general-purpose input/output flags. Four signals provided by the EVM's CPLD can be individually programmed as inputs or outputs. By                                                                                                                                                                                                                                                                                                         |

default, for compatibility with C6x EVM daughterboards, two signals

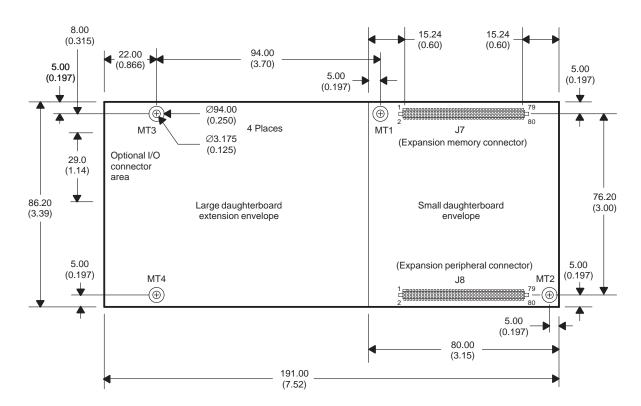

#### 4.8.3 Daughterboard

The EVM supports the mating of a daughterboard that has two 80-pin 0.050"x0.050" TFM-series connectors from Samtec. The recommended mating connector, whose part number is TFM-140-32-S-D-LC, is a surface-mount connector that provides a 0.465" mated height.

The EVM supports two sizes of daughterboards which both use the two 80-pin connectors. The small daughterboard measures approximately 3.15" long and 3.4" wide and mounts in the center of the board over the low-profile buffers and memories. This format is intended for daughterboards that do not require an I/O connection on the mounting bracket.

The large daughterboard measures approximately 7.5" long and 3.4" wide and mounts from the center of the board over to the mating connector end of the board. This format is intended for daughterboards that require an I/O connection on the mounting bracket or need more space than the small daughterboard provides.

Daughterboards mount with their primary component sides down. This ensures that the PCI height requirement is met and no components are exposed to possible damage due to board insertions and extractions.

Figure 4–3 shows the location of the expansion connectors and the dimensions of the EVM daughterboards. This figure shows the component side of the EVM.

Figure 4–3. Daughterboard Envelopes and Connections on EVM

#### Notes:

- 1. All dimensions are shown in millimeters. Inch dimensions are shown in parentheses.

- 2. Drawing shows daughterboard envelopes and connections on components side of EVM board.

- 3. Standard size daughterboard is 80.0 x 86.2 mm (3.15 x 3.39").

- 4. Full-size daughterboard is 191.0 x 86.2 mm (7.52 x3.39").

- 5. Daughterboard connectors are Samtec .050 x .050" Micro Strips (SFM-140-L2-S-D-LC).

- 6. Daughterboard mating connectors are Samtec TFM-140-32-S-D-LC.

- 7. Mating height is 0.465" (11.81 mm).

- 8. There are four plated holes (MT1–MT4) on the EVM for standoff mounting.

- 9. Mounting holes MT1-MT3 are electrically connected to digital ground

- 10. Mounting hole MT4 is floated with no electrical connection.

#### 4.8.4 Compatibility with C6x EVM Daughterboards

The PCI2040 EVM's expansion interfaces are designed to be compatible with the C6x EVM daughterboards. This is advantageous because it allows these daughterboards to be used on this EVM also. This presents a few challenges, since the C6x is a 32-bit processor with a different memory interface. However, with some additional logic and a registered transceiver on the EVM, the PCI2040's EVM should be compatible with virtually all existing daughterboards.

32-bit memory accesses from the 16-bit 5410 DSP are accomplished in software by making two accesses to the least and most significant words. In hardware, this involves the use of a 16-bit registered transceiver and control logic in the CPLD.

DSP software must enable the 32-bit access mode by setting the DB\_WIDE bit in the CPLD and setting the DB\_32ODD bit for the appropriate target address (0 = even, 1 = odd). For reads, the LSW is read first, followed by the MSW. For writes, the MSW is written first, followed by the LSW. Accesses to the LSW cause the memory access to take place with a 32-bit daughterboard.

The C6x has four byte enables since it can access individual bytes. The C54x does not support individual byte accesses. This shouldn't be a problem with most daughterboards. The PCI2040 EVM does ground BE1 and BE0 so that they are always enabled. BE3 and BE2 are mapped to the DSP's upper address lines A21 and A20 which are always zero for memory accesses to C6x daughterboards. Therefore, all four bytes enables are enabled when accessing C6x daughterboards.

The C6x DSP has different memory interface signals than the C54x DSP. Since the daughterboard interface is based on the C6x memory interface, some simple logic is included on the EVM to convert C54x memory control signals to C6x memory control signals for compatibility. The signals that are created include  $\overline{X}$ \_OE,  $\overline{X}$ \_RE, and  $\overline{X}$ \_WE. Additionally, the C54x MSTRB signal is provided on a pin that is a no-connect on C6x daughterboards.

The C6x DSP has four chip enables ( $\overline{CE0}$ – $\overline{CE3}$ ). C6x daughterboards are provided with  $\overline{CE1}$ ,  $\overline{CE2}$ , and  $\overline{CE3}$ . The C54x does not provide chip enables, but it does provide memory space enables. Therefore, the C6x enables were mapped to the DSP's  $\overline{DS}$ ,  $\overline{PS}$ , and  $\overline{IS}$  signals. Since  $\overline{CE1}$  is the default space for C6x daughterboards, the 54x's data memory space is the default space, so it can support bootloading from a daughterboard.

The C5410 does not provide the McBSP signal CLKS, so it is not available on the daughterboard interface. These signals are no connects on the C54x EVM. Since the C54x EVM still provides the CLKX and CLKR signals, independent transmit and receive clocks are available at the daughterboard, so this should meet most daughterboards' requirements.

The C6x has two timers, with each timer having an input and an output. The C5410 only has one timer output. The C54x EVM has a no connect for the first timer input. It places the software-controlled DB\_INT signal on the timer 1 output and the DSP's  $\overline{\text{BIO}}$  signal on the timer 1 input pins.

The C54x provides all four external DSP interrupt signals (INT0–INT3). The C6x EVM only provided a single interrupt on the pin where INT0 is assigned. Therefore, the PCI2040 EVM has a superset of interrupts on pins that were no-connects on the C6x EVM. Note that these interrupts are compatible with TI's new daughterboard specification that allocates these extra pins to additional interrupts.

The C54x does not have interrupt identification codes like the C6x (INUM0–INUM3). Therefore, these pins provide C54x signals including IACK, MSC, and IOSTRB. The interrupt ID codes are not used on any existing C6x daughterboards, so this shouldn't be a problem.