# ICE3B2565

SMPS Evaluation Board with  $CoolSET^{TM}$  F3 ICE3B2565

Power Management & Supply

Edition 2005-01-13

Published by Infineon Technologies Asia Pacific, 168 Kallang Way, 349253 Singapore, Singapore

© Infineon Technologies AP 2004.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### **Warnings**

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| ICE3B2565         |                                              |      |

|-------------------|----------------------------------------------|------|

| Revision History: | 2004-11                                      | V1.0 |

| Previous Version: | none                                         |      |

| Page              | Subjects (major changes since last revision) |      |

|                   |                                              |      |

|                   |                                              |      |

|                   |                                              |      |

|                   |                                              |      |

|                   |                                              |      |

|                   |                                              |      |

|                   |                                              |      |

SMPS Evaluation Board with CoolSET<sup>™</sup> F3 ICE3B2565: License to Infineon Technologies Asia Pacific Pte Ltd

ANP0012

Simon Lim Jeoh Meng Kiat Luo Junyang

#### **We Listen to Your Comments**

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: <a href="mailto:ap-lab.admin@infineon.com">ap-lab.admin@infineon.com</a>

| Table of Contents                             |                                                                                                                                                                                                             | Page |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1                                             | Evaluation Board                                                                                                                                                                                            | 5    |

| 2                                             | List of Features                                                                                                                                                                                            | 6    |

| 3                                             | Technical Specifications                                                                                                                                                                                    | 6    |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7 | Circuit Description  Line Input.  PWM Control and Power Stage  Clamping Network.  Primary Current Sense.  Output Stage  Feedback Loop  Blanking Window for Load Jump / Active Burst Mode  Active Burst Mode |      |

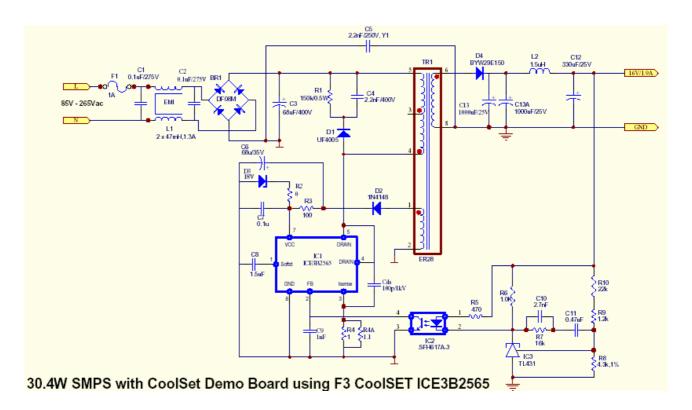

| 5                                             | Circuit Diagram                                                                                                                                                                                             | 9    |

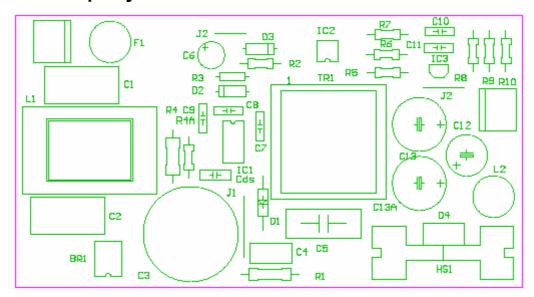

| 6                                             | PCB Top Layer                                                                                                                                                                                               | 10   |

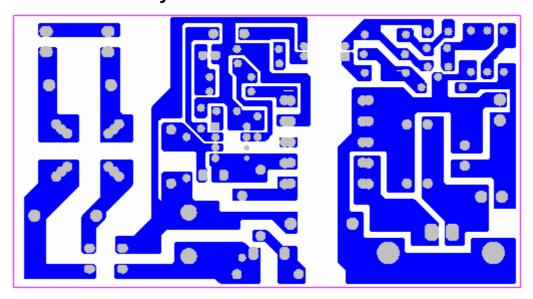

| 7                                             | PCB Bottom Layer                                                                                                                                                                                            | 11   |

| 8                                             | Component List                                                                                                                                                                                              | 12   |

| 9                                             | Transformer Layout                                                                                                                                                                                          | 13   |

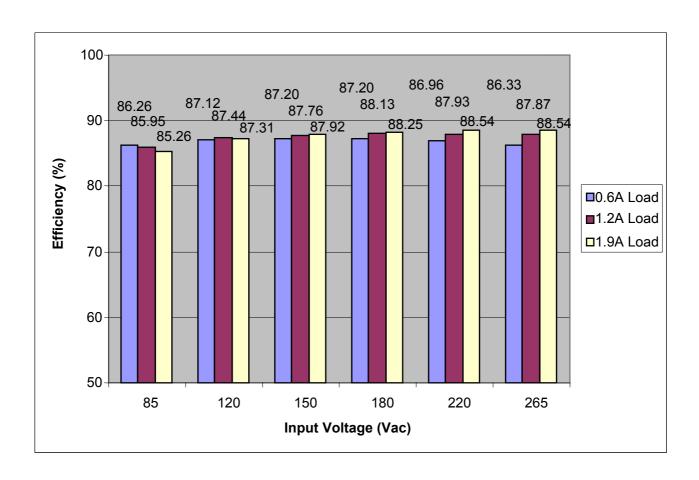

| <b>10</b><br>10.1                             | Test ResultsLoad test (table and figure)                                                                                                                                                                    |      |

| 11                                            | Standby Power Test (Figure)                                                                                                                                                                                 | 15   |

#### **Abstract**

This application note is a description for a switching mode power supply Evaluation Board designed in a typical off-line flyback converter topology that utilizes the ICE3B2565 F3 CoolSET<sup>TM</sup>. The application operates in discontinuous conduction mode and is especially suitable as an AC/DC power supply for LCD monitors, adapters for printers and notebook computers, DVD players and set-top boxes in addition to industrial auxiliary power supplies. Designed based on the proven technology of F2 CoolSET<sup>TM</sup> ICE2xxxxx, the F3 CoolSET<sup>TM</sup> provides Active Burst Mode to reach the lowest Standby Power Requirement at less than 100mW during no load conditions. In Active Burst Mode the ripple of the output can also be reduced to less than 1%. Furthermore, an adjustable Blanking Window by varying the value of Soft Start capacitor is being offered to support applications which needs surge power for a limited period of time (e.g. switching on capacitive loads).

### 1 Evaluation Board

#### 2 List of Features

Features Of CoolSET<sup>TM</sup> F3 ICE3B2565

650V avalanche rugged CoolMOS™ with built in switchable Startup Cell

Active Burst Mode for lowest Standby Power @ light load controlled by Feedback signal

Fast load jump response in Active Burst Mode

67kHz fixed switching frequency

Auto Restart Mode for Overtemperature Detection, Overvoltage Detection,

Overload, Open Loop and VCC Undervoltage

Blanking Window for short duration high current

User defined Soft Start

Max Duty Cycle 72%

Internal Leading Edge Blanking

Soft switching for low EMI

### 3 Technical Specifications

| Input voltage              | 85VAC~265VAC      |

|----------------------------|-------------------|

| Input frequency            | 50Hz, 60Hz        |

| Output voltage and current | 16VDC, 1.9A       |

| Output power               | 30.4W             |

| Efficiency                 | >80% at full load |

Application Note 6 2005-01-13

### 4 Circuit Description

#### 4.1 Line Input

The AC line input side comprises the input fuse F1 as over-current protection. The choke L1, X2-capacitors C1, C2 and Y1-capacitor C5 act as radio interference suppressors. After the bridge rectifier BR1 and the input capacitor C3, a voltage of 80 to 380 VDC depending on input voltage is available.

#### 4.2 PWM Control and Power Stage

The PWM pulse is generated by 8-pin CoolSET™F3 ICE3B2565. ICE3B2565 is an integrated power IC which includes both of the current- mode PWM controller and a CoolMOS<sup>™</sup> with 650V breakdown voltage. The control IC and CoolMOS<sup>™</sup> are fabricated by the different optimized chip technologies respectively and no compromise like monolithic approaches is necessary.

#### 4.3 Clamping Network

R1, C4 and D1 dissipate the energy of the leakage inductance.

#### 4.4 Primary Current Sense

The primary current is sensed by the external shunt resistor R4 and R4A. The sense voltage is fed into ICE3B2565 and a cycle by cycle current limiting is achieved. Primary current is being converted to a corresponding voltage level at CS pin. A 220ns leading edge blanking is provided to avoid leading edge spikes from distorting the current limiting.

#### 4.5 Output Stage

On the secondary side the power is coupled out by an ultra-fast diode BYW29E150. The capacitor C13, provide energy buffering following with the LC filter, L2 and C12 to reduce the output voltage ripple considerably. Storage capacitor C13 is selected to have an internal resistance as small as possible (ESR) to minimizes the output voltage ripple

#### 4.6 Feedback Loop

The output voltage is sensed by the voltage divider of R8, R9 and R10 and compare to TL431 internal reference voltage. The output voltage of TL431, IC3 is transferred to the primary via an optocoupler, IC2 for regulation control. The secondary regulation control is adopted with TL431 and optocoupler. C10, C11, R7 being the compensation network constitutes the external circuitry of the error amplifier of TL431. This circuitry allows the feedback to be precisely matched to dynamically varying load conditions, thereby providing stable control. The maximum current through the optocoupler diode and the voltage reference is limited by the resistor R5 and R6. Optocoupler IC2 is used for floating transmission of the control signal to the "FB" input of the ICE3B2565.

#### 4.7 Blanking Window for Load Jump / Active Burst Mode

In case of Load Jumps the Controller provides a Blanking Window before activating the Overvoltage Protection and entering the Auto Restart Mode. This time is generated by charging up the Soft Start capacitor from 4.4V to 5.4V. Within this timeframe the voltage at Feedback pin can rise up above 4.8V, without switching off due to Overload Protection. During this operation the transferred power is limited to the maximum peak current defined by the value of the sense resistor. The same procedure happens to the

Application Note 7 2005-01-13

external Soft Start capacitor if a low load condition is detected when VFB is falling below 1.32V. Only after  $V_{SOFTS}$  has exceeded 5.4V and Vfb is still below 1.32V, Active Burst Mode is entered.

#### 4.8 Active Burst Mode

At light load condition, the SMPS enters into Active Burst Mode. The controller is always active at this state.  $V_{CC}$  must therefore be above the switch off threshold  $V_{CCoff}$  = 8.5V. While supporting low ripple on  $V_{OUT}$  and fast response on load jump, efficiency also increased significantly during Active Burst Mode. When the voltage level at FB falls below 1.32V, capacitor C8 at SOFTST pin is allowed to charge starting from the clamped voltage level at 4.4V in Normal Operating Mode. Active Burst Mode is entered if  $V_{SOFTST}$  exceeds 5.4V. A Blanking Window as mentioned earlier which can be adjusted by manipulating C8 is generated to avoid a sudden entering of Burst Mode due to load jump.

During Active Burst Mode the current sense voltage limit at  $I_{SENSE}$  pin,  $V_{ISENSE}$ , is set to 0.257V to reduce the conduction losses. All the internal circuits are switched off except the reference and bias voltages to reduce the total  $V_{CC}$  current consumption to below 1.1mA. The FB voltage is changing like a sawtooth between 3.4 and 4V. To leave Burst Mode, FB voltage must exceed 4.8V. This resets the Active Burst Mode and turns the SMPS into Normal Operating Mode. Maximum current can now be provided to stabilize  $V_{OUT}$ .

Application Note 8 2005-01-13

# 5 Circuit Diagram

# 6 PCB Top Layer

# 7 PCB Bottom Layer

# 8 Component List

| No | Designator | Part Type        | Quantity |

|----|------------|------------------|----------|

| 1  | BR1        | DF08M            | 1        |

| 2  | C1         | 0.1uF/275V       | 1        |

| 3  | C2         | 0.1uF/275V       | 1        |

| 4  | C3         | 68uF/400V        | 1        |

| 5  | C4         | 2.2nF/400V       | 1        |

| 6  | C5         | 2.2nF/250V, Y2   | 1        |

| 7  | C6         | 47u/35V          | 1        |

| 8  | C7         | 0.1u             | 1        |

| 9  | C8         | 1.5uF            | 1        |

| 10 | C9         | 1nF              | 1        |

| 11 | C10        | 2.7nF            | 1        |

| 12 | C11        | 0.47uF           | 1        |

| 13 | C12        | 330uF/25V        | 1        |

| 14 | C13        | 1000uF/25V       | 1        |

| 15 | C13A       | 1000uF/25V       | 1        |

| 16 | Cds        | 100p/1kV         | 1        |

| 17 | D1         | UF4005           | 1        |

| 18 | D2         | 1N4148           | 1        |

| 19 | D3         | 18V              | 1        |

| 20 | D4         | BYW29E150        | 1        |

| 21 | EMI        | 2 x 47mH,1.3A    | 1        |

| 22 | F1         | 1A Fuse          | 1        |

| 23 | HS1        | Heat Sink        | 1        |

| 24 | IC1        | ICE3B2565        | 1        |

| 25 | IC2        | SFH617A-3        | 1        |

| 26 | IC3        | TL431            | 1        |

| 27 | J1         | 30mm Jumper      | 1        |

| 28 | J2         | 10mm Jumper      | 1        |

| 29 | J2         | 10mm Jumper      | 1        |

| 30 | L2         | 1.5uH            | 1        |

| 31 | R1         | 150k/0.5W        | 1        |

| 32 | R2         | 10mm Jumper      | 1        |

| 33 | R3         | 100              | 1        |

| 34 | R4         | 1                | 1        |

| 35 | R4A        | 1.2              | 1        |

| 36 | R5         | 470              | 1        |

| 37 | R6         | 1.5K             | 1        |

| 38 | R7         | 16k              | 1        |

| 39 | R8         | 4.3k,1%          | 1        |

| 40 | R9         | 1.2k             | 1        |

| 41 | R10        | 22k              | 1        |

| 42 | TR1        | ER28             | 1        |

| 43 |            | 3mm screw & nut  | 1        |

| 44 |            | Screw stop       | 1        |

| 45 |            | Insulator Pad    | 1        |

| 46 |            | 2 Pole Connector | 2        |

# 9 Transformer Layout

| Start       | Stop  | No of turns | Wire Size | Layer     |

|-------------|-------|-------------|-----------|-----------|

| 1           | 2     | 5           | 3X0.3mm   | Aux       |

| 3           | 5     | 15          | 2X0.3mm   | Primary   |

| 6           | 8     | 6           | 5X0.3mm   | Secondary |

| 5           | Float |             | 1X0.3mm   | Shield    |

| 4           | 3     | 15          | 2X0.3mm   | Primary   |

| Core Inside |       |             |           |           |

Bobbin: Horizontal Version

Core: ER28/BH1

With 3mm safety margin on both sides of bobbin

Primary Inductance, Lp=325μH, measured between pin 4 and pin 5

(Gapped to Inductance)

### 10 Test Results

### 10.1 Load test (table and figure)

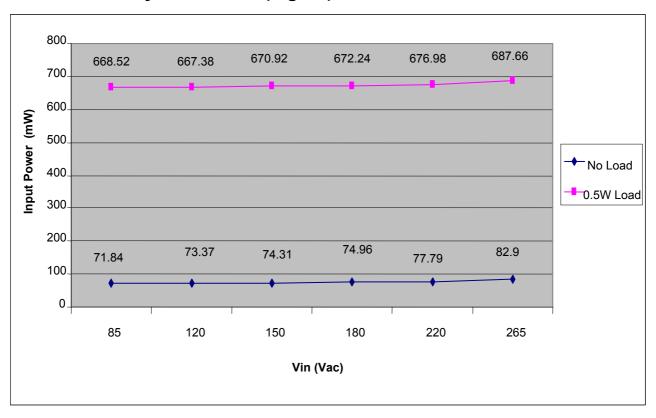

# 11 Standby Power Test (Figure)

#### References

- [1] Infineon Technologies, Datasheet

CoolSET<sup>™</sup> F3

OFF-Line SMPS Current Mode Controller with integrated 650V

Startup Cell/CoolMOS<sup>™</sup>

- Infineon Technologies, Application Note

AN-SMPS-ICE2AXXX-1

CoolSET<sup>TM</sup>

ICE2AxXXX for OFF-Line Switch Mode Power Supply (SMPS)

- [3] Infineon Technologies, Application Note

AN-SMPS-ICE3DS01-1

CoolSET<sup>TM</sup>

ICE3DS01 Current Mode Controller for OFF-Line Switch Mode

Power Supply (SMPS)

- [4] APEB Power Management Chapter September, Article60W SMPS design achieving <100mW standby power</li>

- [5] Infineon Technologies, Application NoteANP0015CoolSet F3 Design Guide