## METHOD 3001.1

## DRIVE SOURCE, DYNAMIC

1. <u>PURPOSE</u>. This method establishes a drive source to be used in measuring dynamic performance of digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The drive source shall supply a smooth transition between specified voltage levels. The signal characteristics shall not vary outside of their prescribed tolerances when interfaced with the device under test (device in the test socket).

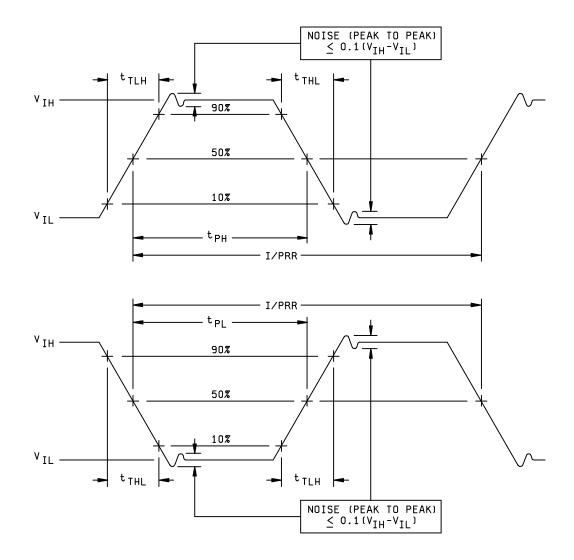

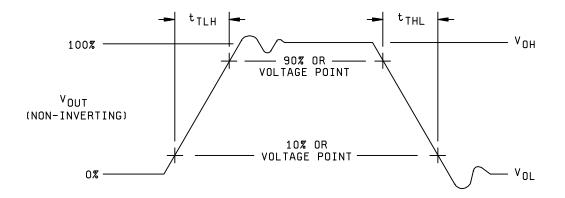

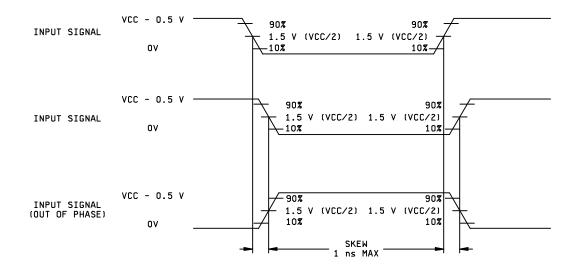

3. <u>PROCEDURE</u>. The drive source shall be measured at the input terminal of the test socket (no device in the test socket). Figure 3001-1 shows typical driving source waveforms and should be used specifying the parameters shown, unless otherwise stated in the applicable acquisition document.

3.1 <u>Pulse amplitude</u>. The specified HIGH level of the driving source shall be greater than the  $V_{OH}$  of the device. The specified LOW level of the driving source shall be less than  $V_{OL}$  of the device.

3.2 <u>Transition times</u>. The transition times of the driving source  $(t_{THL} \text{ and } t_{TLH})$  shall be faster than the transition time of the device being tested, unless otherwise stated in the acquisition document. The transition times shall normally be measured between the 10 percent and 90 percent levels of the specified pulse.

3.3 <u>Pulse repetition rate (PRR)</u>. Unless the pulse repetition rate is the parameter being tested, it shall be chosen so that doubling the rate or reducing by a half will not affect the measurement results.

3.4 <u>Duty factors (duty cycles)</u>. The duty cycles of the driving source shall be chosen so that a 10 percent variation in the duty cycle will not affect the measurement results. The duty cycle shall be defined with respect to either a positive or negative pulse. The pulse width  $(t_p)$  of the input pulses shall be measured between the specified input measurement levels. When more than one pulse input is needed to test a device, the duty cycle of the prime input (i.e., clock, etc.) shall be specified. The phase relationship of all other input pulses shall be referenced to the prime input pulse.

- 4. <u>SUMMARY</u>. The following details, when applicable, shall be specified in the applicable acquisition document:

- a. Levels VIL and VIH.

- b. Driving signal transition times.

- c. Pulse repetition rate.

- d. Duty factors.

- e. Recommended pulse generator, if required.

- f. Input measurement levels, if other than those shown in figure 3001-1.

FIGURE 3001-1. Drive sources.

## METHOD 3002.1

#### LOAD CONDITIONS

1. <u>PURPOSE</u>. This method establishes the load conditions to be used in measuring the static and dynamic performance of digital microelectronic devices such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The load for static tests shall simulate the worst case conditions for the circuit parameters being tested. The load for dynamic tests shall simulate a specified use condition for the parameters being tested. The loads shall be specified in the applicable acquisition document.

2.1 Discrete component load. The load will consist of any combination of capacitive, inductive, resistive, or diode components.

2.1.1 <u>Capacitive load (C<sub>L</sub>)</u>. The total load capacitance of the circuit under test shall include probe and test fixture capacitance and a compensating capacitor as required. The value of the capacitance, measured at 1 MHz  $\pm$ 10 percent, shall be specified in the applicable acquisition document.

2.1.2 Inductive load (L\_). The total load inductance of the circuit under test shall include probe and test fixture inductance and a compensating inductor as required. The value of the inductance, measured at 1 MHz  $\pm$ 10 percent, shall be specified in the applicable acquisition document.

2.1.3 <u>Resistive load (R<sub>L</sub>)</u>. The resistive load shall represent the worst case fan out conditions of the device under test for static tests and a specified fan out condition for dynamic tests. For sink loads, the resistor shall be connected between the power supply ( $V_{CC}$  or  $V_{DD}$ ) and the circuit output for TTL, DTL, RTL, C-MOS, and MOS (N-Channel) and between circuit output and ground for MOS (P-Channel). For source loads, the resistor shall be connected between circuit output and ground for TTL, DTL, RTL, C-MOS, and MOS (P-Channel). For source loads, the resistor shall be connected between circuit output and ground for TTL, DTL, RTL, C-MOS, and MOS (P-Channel). For ECL devices, the load resistors are connected from the output to a specified negative voltage.

2.1.4 <u>Diode load (D\_)</u>. The diode load shall represent the input diode(s) of the circuit under test. The equivalent diode, as specified in the applicable acquisition document, will also represent the base-emitter or base-collector diode of any transistor in the circuit path of the normal load.

2.2 <u>Dynamic load change</u>. The load shall automatically change its electrical parameters as the device under test changes logic state if this is the normal situation for the particular family of circuits being tested. One method of accomplishing this dynamic change is to simulate devices or use actual devices from the same logic family equal to the specified load.

3. <u>PROCEDURE</u>. The load will normally be paralleled by a high impedance voltage detection indicator. The indicator may be either visual or memory storage.

- 4. SUMMARY. The following shall be defined in the applicable acquisition document:

- a. Capacitive load (see 2.1.1).

- b. Inductive load (see 2.1.2).

- c. Resistive load (see 2.1.3).

- d. Diode load, the 1NXXX number and any associated critical parameters shall be specified (see 2.1.4).

- e. Negative voltage, when using a resistive load for ECL (see 2.1.3).

### METHOD 3003.1

## DELAY MEASUREMENTS

1. <u>PURPOSE</u>. This method established the means for measuring propagation delay of digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

1.1 Definitions. The following definitions for the purpose of this test method shall apply.

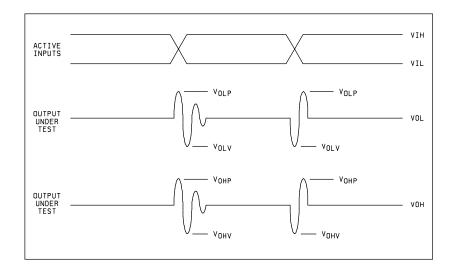

1.1.1 <u>Propagation delay time ( $t_{PHL}$ )</u>. The time measured with the specified output changing from the defined HIGH level to the defined LOW level with respect to the corresponding input transition.

1.1.2 Propagation delay time ( $t_{PLH}$ ). The time measured with the specified output changing from the defined LOW level to the defined HIGH level with respect to the corresponding input transition.

2. <u>APPARATUS</u>. Equipment capable of measuring elapsed time between the input signal and output signal at any percentage point or voltage point between the maximum LOW level and minimum HIGH level shall be provided. The input shall be supplied by a driving source as described in method 3001 of this standard. It is desirable for this equipment to have data logging capability so that circuit dynamic performance can be monitored. The test chamber shall be capable of maintaining the device under test at any specified temperature.

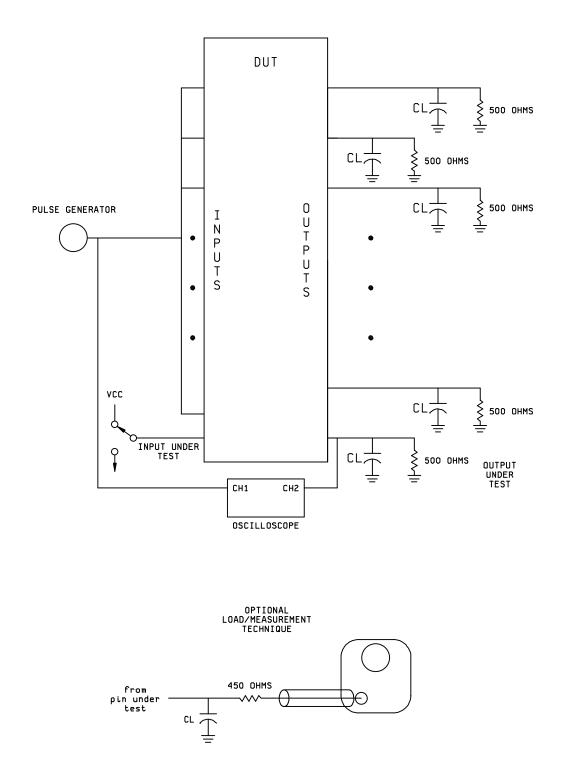

3. <u>PROCEDURE</u>. The test circuit shall be loaded according to method 3002 of this standard. The driving signal to the test circuit shall be provided according to method 3001 of this standard. The device shall be stabilized at the specified test temperature.

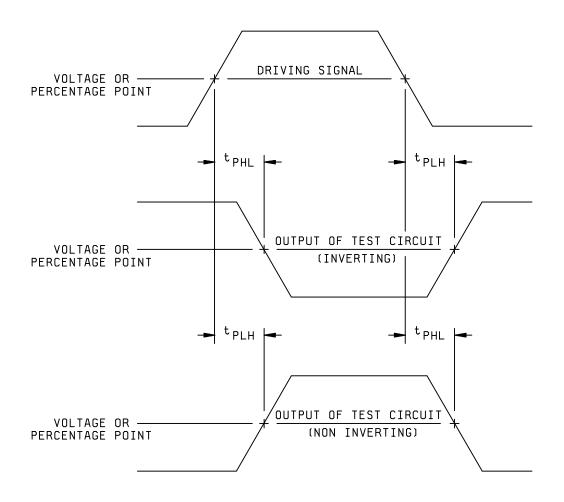

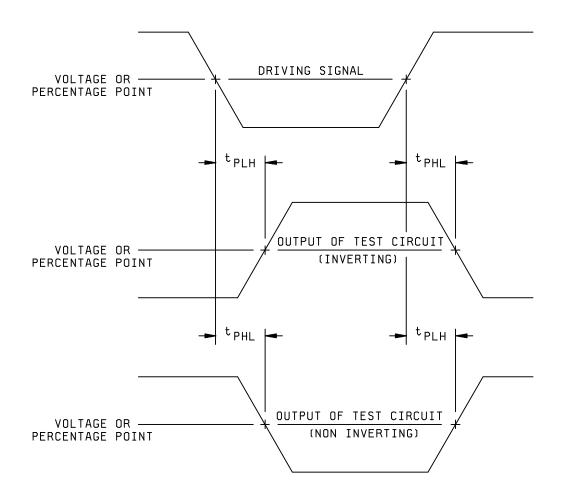

3.1 <u>Measurements at a voltage point</u>. t<sub>PLH</sub> and t<sub>PHL</sub> shall be measured from the threshold voltage point on the driving signal to the threshold voltage point on the test circuit output signal for both inverting and noninverting logic. These delays shall be measured at the input and output terminals of the device under test. The device under test shall be conditioned according to the applicable acquisition document with nominal bias voltages applied. Figures 3003-1 and 3003-2 show typical delay measurements.

3.2 <u>Measurements at percentage points</u>. t<sub>PLH</sub> and t<sub>PHL</sub> shall be measured from a specified percentage point on the driving signal to a specified percentage point on the test circuit output signal for both inverting and noninverting logic. These delays shall be measured at the input and output terminals of the device under test. The device under test shall be conditioned according to the applicable acquisition document with nominal bias voltages applied. Figures 3003-1 and 3003-2 show typical delay measurements.

4. SUMMARY. The following details shall be specified in the applicable acquisition document:

- a. t<sub>PLH</sub> and t<sub>PHL</sub> limits.

- b. Parameters of the driving signal: t<sub>THL</sub>, t<sub>TLH</sub>, high Level, low Level, pulse width, repetition rate.

- c. Load conditions.

- d. Conditioning voltages (static or dynamic).

- e. Measurement points (see 3.1 and 3.2).

- f. Power supply voltages.

- g. Test temperature.

FIGURE 3003-1. Propagation delay-positive input pulse.

FIGURE 3003-2. Propagation delay - negative input pulse.

### METHOD 3004.1

## TRANSITION TIME MEASUREMENTS

1. <u>PURPOSE</u>. This method establishes the means for measuring the output transition times of digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

1.1 <u>Definitions</u>. The following definitions shall apply for the purpose of this method.

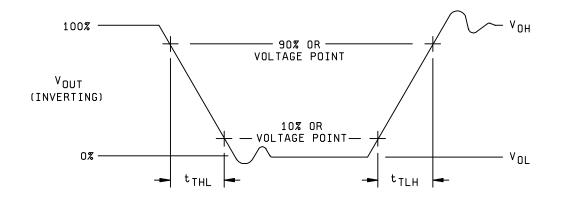

1.1.1 Rise time  $(t_{TLH})$ . The transition time of the output from 10 percent to 90 percent or voltage levels of output voltage with the specified output changing from the defined LOW level to the defined HIGH level.

1.1.2 Fall time ( $t_{THL}$ ). The transition time of the output from 90 percent to 10 percent or voltage levels of output voltage with the specified output changing from the defined HIGH level to the defined LOW level.

2 <u>APPARATUS</u>. Equipment capable of measuring the elapsed time between specified percentage points (normally 10 percent to 90 percent on the positive transition and 90 percent to 10 percent on the negative transition) or voltage levels. The test chamber shall be capable of maintaining the device under test at any specified temperature.

3. <u>PROCEDURE</u>. The device shall be stabilized at the specified test temperature. The device under test shall be loaded as specified in the applicable acquisition document. The load shall meet the requirements specified in method 3002 of this document. The driving signal shall be applied as specified in method 3001 or the applicable acquisition document.

3.1 <u>Measurement of  $t_{TLH}$  and  $t_{THL}$ </u>. Unless otherwise stated, the rise transition time ( $t_{TLH}$ ) shall be measured between the 10 percent and 90 percent points on the positive transition of the output pulse and the fall transition time ( $t_{THL}$ ) shall be measured between the 90 percent and 10 percent points on the negative transition of the output pulse. The device under test shall be conditioned according to the applicable acquisition document with nominal bias voltages applied. Figure 3004-1 shows typical transition time measurement.

4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. t<sub>TLH</sub> limits.

- b. t<sub>THL</sub> limits.

- c. Transition time measurement points if other than 10 percent or 90 percent.

- d. Parameters of the driving signal.

- e. Conditioning voltages (static or dynamic).

- f. Load condition.

- g. Power supply voltages.

- h. Test temperature.

FIGURE 3004-1. Transition time measurements.

### METHOD 3005.1

## POWER SUPPLY CURRENT

1. <u>PURPOSE</u>. This method establishes the means for measuring power supply currents of digital microelectronic devices such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. Equipment capable of applying prescribed voltage to the test circuit power supply terminals and measuring the resultant currents flowing in these terminals shall be provided. The test chamber shall be capable of maintaining the device under test at any specified temperature.

3. PROCEDURE. The device shall be stabilized at the specified test temperature.

3.1 <u>I<sub>CCH</sub> (logic gate)</u>. Inputs of the device under test shall be conditioned in such a way as to provide a HIGH level at the output, the worst case supply voltage(s) shall be applied and the resultant current flow in the supply terminals measured.

3.2 <u>I<sub>CCL</sub> (logic gate)</u>. Inputs of the device under test shall be conditioned in such a way as to provide a LOW level at the output, the worst case supply voltages(s) shall be applied and the resultant current flow in the supply terminals measured.

3.3 <u>I<sub>CC</sub> or I<sub>EE</sub> of combinatorial digital circuits</u>. The inputs of the device under test shall be conditioned to put the device into its worst case power dissipating state. The current flowing into the V<sub>CC</sub>, (positive supply) terminal, or out of the V<sub>EE</sub> (negative supply) terminal shall be measured with the V<sub>CC</sub> and V<sub>EE</sub> voltages at their maximum specified operating levels.

3.4  $I_{CC}$  or  $I_{EE}$  of sequential digital circuits. The inputs of the device under test shall be exercised to put the device in a known output state (either HIGH or LOW) that causes worst case power dissipation. The current flowing into the V<sub>CC</sub> (positive supply) terminal, or out of the V<sub>EE</sub> (negative supply) terminal shall be measured with the V<sub>CC</sub> and V<sub>EE</sub> voltages at their maximum specified operating levels.

3.5 IDD (MOS logic gate). Inputs of the device under test shall be conditioned in such a way as to provide a HIGH level at the output of MOS (P-Channel and C-MOS) or a LOW level at the output of MOS (N-Channel and C-MOS); worst case voltage(s) shall be applied and the resultant current in the supply terminals measured.

3.6 I<sub>GG</sub> (MOS P-Channel and N-Channel logic gates). Inputs of the device under test shall be conditioned in such a way as to provide a HIGH level at the output of MOS (P-Channel) or a LOW level at the output of MOS (N-Channel); worst case voltage(s) shall be applied and the resultant current flow in the supply terminals measured.

3.7 I<sub>DD</sub> of MOS combinatorial circuits. See 3.3 above.

3.8 I<sub>DD</sub> of MOS sequential circuits. See 3.4 above.

3.9  $I_{GG}$  of MOS combinatorial circuits. See 3.3 above.

3.10 IGG of MOS sequential circuits. See 3.4 above.

3.11 I<sub>DD</sub> dynamic (MOS logic gating and flip flop circuits). The driving signal to the test circuit shall be provided according to method 3001 of this standard; the worst case voltage(s) shall be applied and the resultant average current in the supply terminals measured.

- 4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. Test temperature.

- b. Power supply voltages.

- c.  $I_{CCH}$ ,  $I_{CCL}$ ,  $I_{DD}$ ,  $I_{GG}$ , and  $I_{EE}$  limits.

- d. Conditioning voltages.

- e. Dynamic input parameters (see 3.11).

### METHOD 3006.1

## HIGH LEVEL OUTPUT VOLTAGE

1. <u>PURPOSE</u>. This method establishes the means for assuring circuit performance to the limits specified in the applicable acquisition document in regard to HIGH level output drive, which may be specified as a minimum value  $V_{OH}$  min. or as a maximum  $V_{OH}$  max. This method applies to digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The test instrument shall be capable of loading the output of the circuit under test with the specified positive or negative currents ( $I_{OH}$ ). Resistors may be used to simulate the applicable current levels. The test instrument shall also be capable of supplying the worst case power supply and input voltages. The test chamber shall be capable of maintaining the device under test at any specified test temperature.

3. <u>PROCEDURE</u>. The device shall be stabilized at the specified test temperature. Worst case power supply voltages and worst case input levels including guaranteed noise margins shall be applied to the test circuit to provide a HIGH level output. Forcing current, equal to the circuit worst case high level fan out, shall then be applied to the test circuit output terminal and the resultant output voltage measured. The output measurement shall be made after each input is conditioned.

4. SUMMARY. The following details shall be specified in the applicable acquisition document:

- a. Test temperature.

- b. Current to be forced from or into output terminal.

- c. Power supply voltage(s).

- d. Input levels.

- e. V<sub>OH</sub> min. or V<sub>OH</sub> max. limits.

### METHOD 3007.1

## LOW LEVEL OUTPUT VOLTAGE

1. <u>PURPOSE</u>. This method establishes the means for assuring circuit performance to the limits specified in the applicable acquisition document with regard to LOW level output drive which is specified as a maximum value ( $V_{OL}$  max) or a minimum value ( $V_{OL}$  min). This method applies to digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The test instrument shall be capable of loading the output of the circuit under test with the specified positive or negative currents ( $I_{OL}$ ). Resistors may be used to simulate the applicable current levels. The test instrument shall be capable of supplying the worst case power supply and input voltages. The test chamber shall be capable of maintaining the device under test at any specified temperature.

3. <u>PROCEDURE</u>. The device shall be stabilized at the specified test temperature. Worst case power supply voltages and worst case input levels including guaranteed noise margins shall be applied to the test circuit to provide a LOW level output. Forcing current, equal to the circuit worst case LOW level fan out, shall be applied to the test circuit output and the resultant output voltage measured. The output measurement shall be made after each input is conditioned.

4. SUMMARY. The following details shall be specified in the applicable acquisition document:

- a. Test temperature.

- b. Current to be forced into or from the output terminal.

- c. Power supply voltage(s).

- d. Input levels.

- e. V<sub>OL</sub> max or V<sub>OL</sub> min limits.

### METHOD 3008.1

## BREAKDOWN VOLTAGE, INPUT OR OUTPUT

1. <u>PURPOSE</u>. This method establishes the means for assuring device performance to the limits specified in the applicable acquisition document in regard to input and output breakdown voltage symbolized as  $V_{IH}$  (max),  $V_{OH}$  (max),  $V_{IL}$  (min), and  $V_{OL}$  (min) as applicable. This method applies to digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The test chamber shall be capable of maintaining the device under test at any specified temperature.

2.1 <u>Method A</u>. This test is generally performed to assure that breakdown does not occur on a device. An instrument shall be provided that has the capability of forcing a specified voltage at the input or output terminal of the test circuit and measuring the resultant current flowing in that terminal. The test instrument shall also have the capability of applying voltage levels to all other terminals. Care should be taken to assure that the test equipment does not inadvertently apply voltage to the device under test that will exceed the maximum rating of each terminal and that the current from the test equipment is sufficiently limited so that the device is not destroyed. This method can also be used to test the ability of power supply terminals to withstand a voltage overload.

2.2 <u>Method B</u>. This test is generally performed to assure that breakdown does occur on a device as specified in the applicable acquisition document. An instrument shall be provided that has the capability of forcing a specified current at the input or output terminal of the test circuit and measuring the resultant voltage at that terminal. The test instrument shall also have the capability of applying voltage levels to all other terminals. Care should be taken to assure that the test equipment does not inadvertently apply voltage to the device under test that will exceed the maximum rating of each terminal so that the device is not destroyed. The minimum compliance voltage of the current source shall be specified when applicable.

3. <u>PROCEDURE</u>. The device shall be stabilized at the specified test temperature.

3.1 <u>Method A</u>. All terminals, with the exception of the test terminal, shall be conditioned according to the applicable acquisition document. A prescribed voltage shall be applied to the designated input or output terminal and the resultant current measured. When testing for breakdown, all input and output terminals shall be tested individually. At the conclusion of the test, the device shall be functional.

3.2 <u>Method B</u>. All terminals, with the exception of the test terminal, shall be conditioned according to the applicable acquisition document. The specified current shall be forced at the designated input or output terminal, and the voltage at the terminal measured. At the conclusion of the test, the device shall be functional.

- 4. SUMMARY. The following details shall be specified in the applicable acquisition document:

- a. Test temperature.

- b. Forced voltages (method A).

- c. Conditioning voltages for all other terminals.

- d. Forced current (method B).

- e. Maximum breakdown current limits (method A).

- f. Minimum breakdown terminal voltage (method B).

### METHOD 3009.1

## INPUT CURRENT, LOW LEVEL

1. <u>PURPOSE</u>. This method establishes the means for assuring circuit performance to the limits specified in the applicable acquisition document in regard to LOW level input load which may be specified as a minimum value ( $I_{IL}$  min) or as a maximum value ( $I_{IL}$  max). This method applied to digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The test chamber shall be capable of maintaining the device under test at any specified test temperature. An instrument shall be provided that has the capability of applying the worst case LOW voltage to the input terminal of the test circuit, (and worst case levels on the other inputs), and measuring the resultant current at the input terminal.

3. <u>PROCEDURE</u>. The device shall be stabilized at the specified test temperature. Worst case power supply voltages and worst case input voltages shall be applied to the test circuit and the resultant current at the input terminal shall be measured. Inputs shall be tested individually.

4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. Test temperature.

- b. Power supply voltages.

- c. Input voltage.

- d. Voltages at other input terminals which cause worst case current at the input under test.

- e.  $I_{IL}$  max or  $I_{IL}$  min.

### METHOD 3010.1

## INPUT CURRENT, HIGH LEVEL

1. <u>PURPOSE</u>. This method establishes the means for assuring circuit performance to the limits specified in the applicable acquisition document in regard to HIGH level input load which may be specified as a maximum value ( $I_{IH}$  max) or a minimum value ( $I_{IH}$  min). This method applies to digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The test chamber shall be capable of maintaining the device under test at any specified temperature. An instrument shall be provided that has the capability of applying the worst case HIGH voltage to the input terminal of the test circuit, and worst case levels at the other inputs, and measuring the resultant current at the input terminal.

3. <u>PROCEDURE</u>. The device shall be stabilized at the specified test temperature. Worst case power supply voltages and worst case input voltages shall be applied to the test circuit and the resultant current at the input terminal shall be measured. Inputs shall be tested individually.

4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. Test temperature.

- b. Power supply voltages.

- c. Input voltage.

- d. Input voltages at other input terminals which cause worst case current at the input under text.

- e. I<sub>IH</sub> max.

### METHOD 3011.1

## OUTPUT SHORT CIRCUIT CURRENT

1. <u>PURPOSE</u>. This method establishes the means for assuring circuit performance to the limits specified in the applicable acquisition document in regard to output short circuit current (I<sub>OS</sub>). This method applied to digital microelectronic devices, such as TTL, DTL, RTL, and MOS.

2. <u>APPARATUS</u>. A test chamber capable of maintaining the device under test at any specified temperature. An instrument will be provided that has the capability of forcing a voltage specified in the applicable acquisition document at the output terminal of the device under test and measuring the resultant current flowing in that terminal. The test instrument shall also have the capability of applying specified voltage levels to all other inputs.

3. <u>PROCEDURE</u>. The device shall be stabilized at the specified test temperature. Each output per package shall be tested individually.

3.1 <u>TTL, DTL, RTL, MOS (P-Channel and N-Channel)</u>. Inputs of the device under test shall be conditioned in such a way as to provide a HIGH level at the output for TTL, DTL, RTL, and MOS (N-Channel) and a LOW level at the output for MOS (P-Channel). The output terminal shall be forced to 0 volt potential and the resultant current flow measured.

3.2 <u>C-MOS  $I_{OSH}$ </u>. Inputs of the device under test shall be conditioned in such a way as to provide a HIGH level at the output. The output terminal shall be forced to 0 volt potential and the resultant current flow measured.

3.3 <u>C-MOS  $I_{OSL}$ </u>. Inputs of the device under test shall be conditioned in such a way as to provide a LOW level at the output. The output terminal shall be forced to a voltage potential specified in the acquisition document and the resultant current flow measured.

- 4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. Test temperature.

- b. Input conditioning voltages.

- c. Power supply voltages.

- d. I<sub>OS</sub> max and I<sub>OS</sub> min limits.

### METHOD 3012.1

### **TERMINAL CAPACITANCE**

1. <u>PURPOSE</u>. This method establishes the means for assuring circuit performance to the limits specified in the applicable acquisition document in regard to terminal capacitance. This method applies to digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The instrument shall be capable of applying a 1 MHz controllable amplitude signal superimposed on a variable plus or minus dc voltage. The instrument will also have the capability of measuring the capacitance of this terminal to within the limits and tolerance specified in the applicable acquisition document.

3. <u>PROCEDURE</u>. This test may be performed at 25°C ±3°C. The capacitance measuring bridge shall be connected between the input or output terminal and the ground terminal of the test circuit. The bridge shall be adjusted for a signal of 1 MHz, riding a bias level specified in the applicable acquisition document; the signal amplitude shall not exceed 50 mV rms. With no device in the test socket the bridge shall then be zeroed. For capacitance values below 20 pF, the device shall be connected directly to the bridge with leads as short as possible to avoid the effects of lead inductance. After inserting the device under test and applying the specified bias conditions, the terminal capacitance shall be measured and compared to the limits listed in the applicable acquisition document.

4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. Circuit bias conditions.

- b. Bias level at which measurements are to be made.

- c. Maximum capacitance limits.

## METHOD 3013.1

### NOISE MARGIN MEASUREMENTS FOR DIGITAL MICROELECTRONIC DEVICES

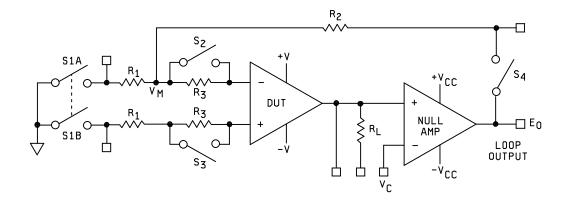

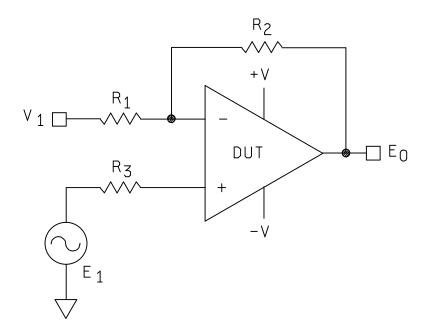

1. <u>PURPOSE</u>. This method establishes the means of measuring the dc (steady- state) and ac (transient) noise margin of digital microelectronic devices or to determine compliance with specified noise margin requirements in the applicable acquisition document. It is also intended to provide assurance of interchangeability of devices and to eliminate misunderstanding between manufacturers and users on noise margin test procedures and results. The standardization of particular combinations of test parameters (e.g., pulse width, pulse amplitude, etc.) does not preclude the characterization of devices under test with other variations in these parameters. However, such variations shall, where applicable, be provided as additional conditions of test and shall not serve as a substitute for the requirements established herein.

- 1.1 <u>Definitions</u>. The following definitions shall apply for the purposes of this test method:

- a. Noise margin. Noise margin is defined as the voltage amplitude of extraneous signal which can be algebraically added to the noise-free worst case "input" level before the output voltage deviates from the allowable logic voltage levels. The term "input" (in quotation marks) is used here to refer to logic input terminals or ground reference terminals.

- b. DC noise margin. DC noise margin is defined as the dc voltage amplitude which can be algebraically added to the noise-free worst case "input" level before the output exceeds the allowable logic voltage levels.

- c. AC noise margin. AC noise margin is defined as the transient or pulse voltage amplitude which can be algebraically added to the noise-free worst case "input" level before the output voltage exceeds the allowable logic voltage levels.

- d. Maximum and minimum. Maximum and minimum refer to an algebraic system where "max" represents the most positive value of the range and "min" represents the least positive value of the range.

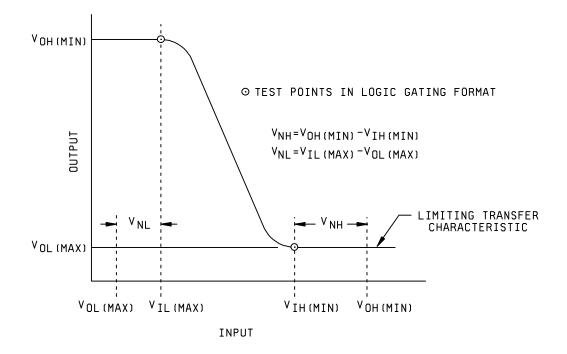

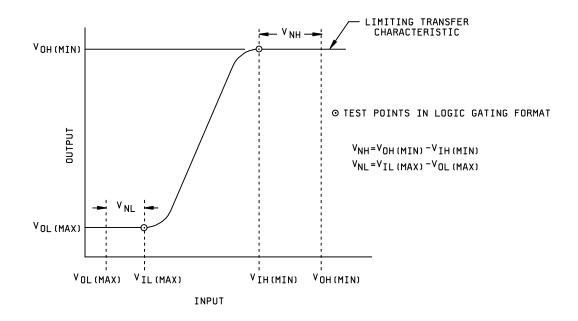

1.2 <u>Symbols</u>. The following symbols shall apply for the purposes of this test method and shall be used in accordance with the definitions provided (see 1.2.1, 1.2.2, and 1.2.3) and depicted on figures 3013-1, 3013-2, and 3013-3.

#### 1.2.1 Logic levels.

- VIL max: The maximum allowed input LOW level in a logic system.

- V<sub>IL</sub> min: The minimum allowed input LOW level in a logic system.

- V<sub>IH</sub> max: The maximum allowed input HIGH level in a logic system.

- V<sub>IH</sub> min: The minimum allowed input HIGH level in a logic system.

- $V_{OL}$  max: The maximum output LOW level specified for a digital microelectronic device.  $V_{OL}$  max is also the noise-free worst case input LOW level,  $V_{OL}$  (max)  $\leq V_{IL}$  (max)

- $V_{OH}$  min: The minimum output HIGH level specified for a digital microelectronic device.  $V_{OH}$  min is also the noise-free worst case input HIGH level,  $V_{OH}$  (min)  $\geq V_{IH}$  (min)

#### Noise margin levels.

- V<sub>NL</sub>: The LOW level noise margin or input voltage amplitude which can be algebraically added to V<sub>OL</sub> (max) before the output level exceeds the allowed logic level.

- V<sub>NH</sub>: The HIGH level noise margin or input voltage amplitude which can be algebraically added to V<sub>OH</sub> (min) before the output level exceeds the allowed logic level.

- V<sub>NG+</sub>: The positive voltage which can be algebraically added to the ground level before the output exceeds the allowed logic level determined by worst case logic input levels.

- V<sub>NG</sub>.: The negative voltage which can be algebraically added to the ground level before the output exceeds the allowed logic level determined by worst case logic input levels.

- V<sub>NP+</sub>: The positive voltage which can be algebraically added to the noise-free worst case most positive power supply voltage before the output exceeds the allowed logic level determined by worst case logic input levels.

- V<sub>NP</sub>.: The negative voltage which can be algebraically added to the noise-free worst case most negative (least positive) power supply voltage before the output exceeds the allowed logic level determined by worst case logic input levels.

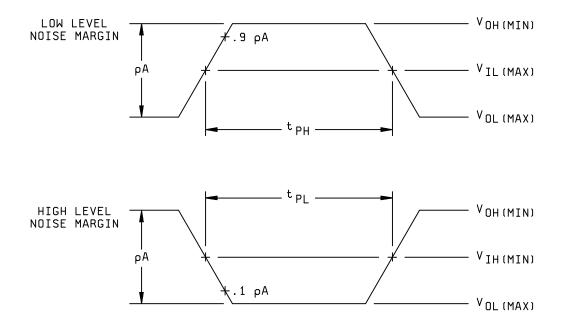

#### 1.2.3 Noise pulse widths.

- t<sub>PL</sub>: The LOW level noise pulse width, measured at the V<sub>IL</sub> (max) level.

- $t_{PH}$ : The HIGH level noise pulse width, measured at the V<sub>IH</sub> (min) level.

2. <u>APPARATUS</u>. The apparatus used for noise margin measurements shall include a suitable source generator (see 2.1), load (see 2.2), and voltage detection devices for determining logic state.

2.1 <u>Source generator</u>. The source generator for this test shall be capable of supplying the required ac and dc noise inputs. In the case of pulsed inputs the transition times of the injected noise pulse shall each be maintained to less than 20 percent of the pulse width measured at the 50 percent amplitude level. For the purpose of this criteria, the transition times shall be between the 10 percent and 90 percent amplitude levels. The pulse repetition rate shall be sufficiently low that the element under test is at steady-state conditions prior to application of the noise pulse. For the purpose of this criteria, doubling the repetition rate or duty cycle shall not affect the outcome of the measurement.

2.2 Load. The load for this test shall simulate the circuit parameters of the normal load which would be applied in application of the device under worst-case conditions. The load shall automatically change its electrical parameters as the device under test changes logic state if this is the normal situation for the particular device load. The load shall be paralleled by a high impedance voltage detection device.

3. <u>PROCEDURE</u>. The device shall be connected for operation using a source generator and load as specified (see 2), and measurements shall be made of  $V_{NL}$ ,  $V_{NH}$ ,  $V_{NG}$ ,  $V_{NP}$ ,  $t_{PL}$ , and  $t_{PH}$  following the procedures for both ac noise margin and dc noise margin (see 3.2 through 3.3.3).

### 3.1 General considerations.

3.1.1 <u>Nonpropagation of injected noise</u>. As defined in 1.1, noise margin is the amplitude of extraneous signal which may be added to a noise-free worst case "input" level before the output breaks the allowable logic levels. This definition of noise margin allows the measurement of both dc and ac noise immunity on logic inputs or power supply lines or ground reference lines by detection of either a maximum LOW level or a minimum HIGH level at the output terminal. Since the output level never exceeds the allowable logic level under conditions of injected noise, the noise is not considered to propagate through the element under test.

3.1.2 <u>Superposition of simultaneously injected noise</u>. Because the logic levels are restored after one stage, and because the noise margin measurement is performed with all "inactive" inputs at the worst case logic levels, the proper system logic levels are guaranteed in the presence of simultaneous disturbances separated by at least one stage.

3.1.3 <u>Characterization of ac noise margin</u>. Although the purpose of this standard test procedure is to insure interchangeability of elements by a single- point measurement of ac noise margin, the test procedure is well suited to the measurement of ac noise margin as a function of noise pulse width. In particular, for very wide pulse widths, the ac noise margin asymptotes to a value identically equal to the dc noise margin.

3.2 Test procedure for dc noise margin.

3.2.1 <u>Worse case configuration</u>. The measurement of dc noise margin using a particular logic input terminal should correspond to the worst case test configuration in the applicable acquisition document. For example, the measurement of LOW level noise margin for a positive-logic inverting NAND gate should be performed under the same worst case test conditions as the dc measurement of  $V_{OH}$  (min). If the worst case dc test conditions for  $V_{OH}$  (min) are high power supply voltage, all unused logic inputs connected to  $V_{OH}$  (min) and output current equal to zero, these conditions should be applied to the corresponding dc noise margin measurement.

3.2.2 LOW level noise margin,  $V_{NL}$ . The LOW level noise margin test is normally performed during the  $V_{OH}$  test for inverting logic and during the  $V_{OL}$  test for noninverting logic. The noise margin is calculated from the following expression:

$$V_{NL} = V_{IL} (max) - V_{OL} (max)$$

3.2.3 <u>HIGH level noise margin,  $V_{NH}$ .</u> The HIGH level noise margin test is performed during the  $V_{OL}$  test for inverting logic and during the  $V_{OH}$  test for noninverting logic. The noise margin is calculated from the following expression:

3.2.4 <u>Negative ground noise margin</u>,  $V_{NG}$ . With all power supply and output terminals connected to the appropriate worst case conditions, apply  $V_{OL}$  (max) to the inputs specified in the applicable acquisition document and decrease the voltage applied to the ground terminal until the output levels equal  $V_{IH}$  (min) for inverting logic and  $V_{IL}$  (max) for noninverting logic. The dc ground noise margin is the voltage measured at the device ground terminal. The dc source resistance of the injected ground line voltage shall be negligible.

3.2.5 <u>Positive ground noise margin, V<sub>NG+</sub></u>. With all power supply and output terminals connected to the appropriate worst case conditions, apply V<sub>OH</sub> (min) to the inputs specified in the applicable acquisition document and increase the voltage applied to the ground terminal until the output levels equal V<sub>IL</sub> (max) for inverting logic and V<sub>IH</sub> (min) for noninverting logic. The dc ground noise margin is the voltage measured at the device ground terminal. The dc source resistance of the injected ground line voltage shall be negligible.

3.2.6 Power supply noise margin,  $V_{NP+}$  or  $V_{NP-}$ . With all input, power supply, and output terminals connected to the appropriate worst case conditions, increase (or decrease) the power supply voltage(s) until the output level equals the appropriate logic level limit. The power supply noise margin is the difference between the measured supply voltage(s) and the appropriate noise-free worst case supply voltage level(s). If more than one power supply is required, the noise margin of each supply should be measured separately.

### 3.3 Test procedure for ac noise margin.

3.3.1 <u>AC noise margin test point</u>. If, for any combination of noise pulse width or transition times, the ac noise margin is less than the dc noise margin, the noise pulse amplitude, pulse width, and transition time which produce the minimum noise margin shall be used as the conditions for test. If the ac noise margin exceeds the dc noise margin, the dc noise margin tests only shall be performed.

3.3.2 LOW level noise margin, pulse width,  $T_{PL}$ . With all unused logic input, power supply, and output terminals connected to the appropriate worst case conditions, a positive-going noise pulse shall be applied to the input under test. The pulse amplitude shall be equal to  $V_{OH}$  (min) minus  $V_{OL}$  (max); the pulse amplitude shall be equal to  $V_{OH}$  (max); and the transition times shall be much less than the minimum transition times of the device under test. The test is performed by initially adjusting the input pulse width at the 0.9 amplitude level to one and one quarter times the rise time. The pulse width is increased until the output voltage is equal to  $V_{IH}$  (max) for inverting logic and equal to  $V_{IL}$  (min) for noninverting logic. The noise margin pulse width is then measured at the input pulse  $V_{IL}$  (max) level.

3.3.3 <u>HIGH level noise margin, pulse width, T<sub>PH</sub>.</u> With all unused logic input, power supply, and output terminals connected to the appropriate worst case conditions, a negative-going noise pulse shall be applied to the input under test. The pulse amplitude shall be equal to  $V_{OH}$  (min) minus  $V_{OL}$  (max); the pulse shall be superimposed on a dc level equal to  $V_{OH}$  (min); and the transition times shall be much less than the minimum transition times of the device under test. The test is performed by initially adjusting the input pulse width at the 0.1 amplitude level to one and one quarter times the rise time. The pulse width is increased until the output voltage is equal to  $V_{IL}$  (min) for inverting logic and  $V_{IH}$  (max) for noninverting logic. The noise margin pulse width is then measured at the input pulse  $V_{IH}$  (min) level.

- 4. <u>SUMMARY</u>. The following details, when applicable, shall be specified in the applicable acquisition document:

- a.  $V_{IL}$  (max).

- $b. \quad V_{IL} \ (min).$

- $c. \quad V_{IH} \ (min).$

- $d. \quad V_{IH} \ (max).$

- e. V<sub>OL</sub> (max).

- f. V<sub>OH</sub> (min).

- $g. \quad V_{\text{NL}}.$

- h.  $V_{\text{NH}}$ .

- i. V<sub>NG</sub>.

- j. V<sub>NP</sub>.

- k. t<sub>PL</sub>.

- I. t<sub>PH</sub>.

- m. Test temperature. Unless otherwise specified, dc noise margin measurements shall be made at the rated operating temperature extremes in addition to any other nominal test temperatures.

- n. Specific noise margin measurements and conditions which are to be performed.

- o. Power supply voltages.

- p. Input conditioning voltages.

- q. Output loads.

- r. Parameters of noise signal.

FIGURE 3013-1. Definitions of noise pulse width.

FIGURE 3013-2. Inverting logic gate transfer characteristic defining test points.

FIGURE 3013-3. Noninverting logic gate transfer characteristic defining test points.

### METHOD 3014

## FUNCTIONAL TESTING

1. <u>PURPOSE</u>. This method establishes the means for assuring circuit performance in regard to the test requirements necessary to verify the specified function and to assure that all logic element paths are not open, stuck-at-HIGH level or stuck-at-LOW LEVEL. This method applies to digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. An instrument shall be provided which has the capability of applying logic patterns (sequentially, if specified) to the logic network input(s) in accordance with the applicable acquisition document. The test instrument shall also be capable of applying nominal power supply voltages and monitoring the outputs for the specified logic levels. The output monitoring circuit may be either a single or double comparator type. The threshold voltage (trip point) for a single comparator or  $V_{OL}$  (max) and  $V_{OH}$  (min) for a double comparator shall be specified in the applicable acquisition document. The test chamber shall be capable of maintaining the device under test at any specified test temperature.

3. <u>PROCEDURE</u>. The device shall be stabilized at the specified test temperature. Nominal power supply voltages and the specified input logic patterns shall be applied to the logic network under test and the output(s) monitored.

4. SUMMARY. The following details shall be specified in the applicable acquisition document:

- a. Test temperature.

- b. Power supply voltage.

- c. Input voltage levels.

- d. Input and output logic patterns.

- e. Output threshold voltage (see 2).

- f.  $V_{OH}$  (min) and  $V_{OL}$  (max) (see 2).

### METHOD 3015.7

### ELECTROSTATIC DISCHARGE SENSITIVITY CLASSIFICATION

1. <u>PURPOSE</u>. This method establishes the procedure for classifying microcircuits according to their susceptibility to damage or degradation by exposure to electrostatic discharge (ESD). This classification is used to specify appropriate packaging and handling requirements in accordance with MIL-PRF--38535, and to provide classification data to meet the requirements of MIL-STD-1686.

1.1 Definition. The following definition shall apply for the purposes of this test method.

1.1.1 Electrostatic discharge (ESD). A transfer of electrostatic charge between two bodies at different electrostatic potentials.

2. APPARATUS.

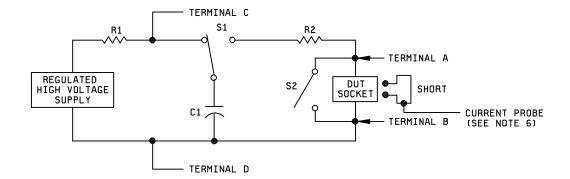

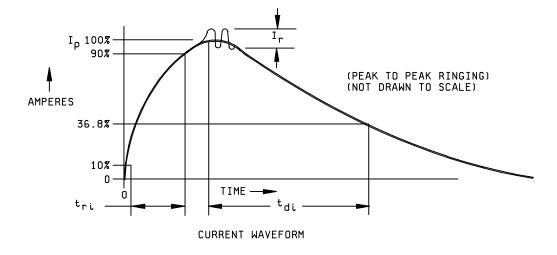

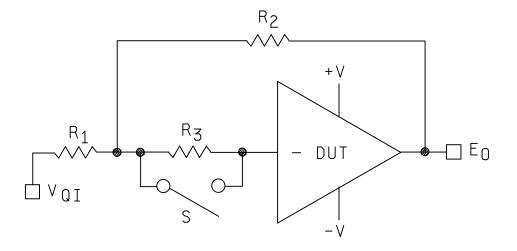

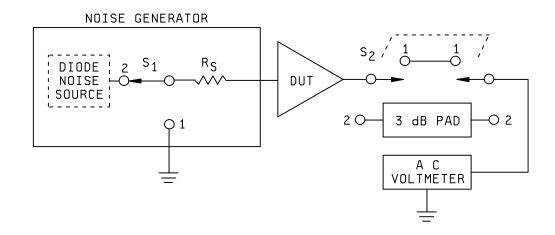

2.1 <u>Test apparatus</u>. ESD pulse simulator and device under test (DUT) socket equivalent to the circuit of figure 3015-1, and capable of supplying pulses with the characteristics required by figure 3015-2.

2.2 <u>Measurement equipment</u>. Equipment including an oscilloscope and current probe to verify conformance of the simulator output pulse to the requirements of figure 3015-2.

2.2.1 <u>Oscilloscope and amplifier</u>. The oscilloscope and amplifier combination shall have a 350 MHz minimum bandwidth and a visual writing speed of 4 cm/ns minimum.

2.2.2 Current probe. The current probe shall have a minimum bandwidth of 350 MHz (e.g., Tektronix CT-1 at 1,000 MHz).

2.2.3 <u>Charging voltage probe</u>. The charging voltage probe shall have a minimum input resistance of 1,000 MΩand a division ratio of 4 percent maximum (e.g., HP 34111A).

2.3 Calibration. Periodic calibration shall include but not be limited to the following.

2.3.1 <u>Charging voltage</u>. The meter used to display the simulator charging voltage shall be calibrated to indicate the actual voltage at points C and D of figure 3015-1, over the range specified in table I.

2.3.2 <u>Effective capacitance</u>. Effective capacitance shall be determined by charging C1 to the specified voltage (with table I), with no device in the test socket and the test switch open, and by discharging C1 into an electrometer, coulombmeter, or calibrated capacitor connected between points A and B of figure 3015-1. The effective capacitance shall be 100 pF ±10 percent over the specified voltage range and shall be periodically verified at 1,000 volts. (Note: A series resistor may be needed to slow the discharge and obtain a valid measurement.)

2.3.3 <u>Current waveform</u>. The procedure of 3.2 shall be performed for each voltage step of table I. The current waveform at each step shall meet the requirements of figure 3015-2.

2.4 <u>Qualification</u>. Apparatus acceptance tests shall be performed on new equipment or after major repair. Testing shall include but not be limited to the following.

2.4.1 <u>Current waveform verification</u>. Current waveform shall be verified at every pin of each test fixture using the pin nearest terminal B (see figure 3015-1) as the reference point. All waveforms shall meet the requirements of figure 3015-2. The pin pair representing the worst case (closest to the limits) waveform shall be identified and used for the verification required by 3.2.

## 3. PROCEDURE.

3.1 General.

3.1.1 <u>Test circuit</u>. Classification testing shall be performed using a test circuit equivalent to figure 3015-1 to produce the waveform shown on figure 3015-2.

METHOD 3015.7 22 March 1989

3.1.2 Test temperature. Each device shall be stabilized at room temperature prior to and during testing.

3.1.3 ESD classification testing. ESD classification testing of devices shall be considered destructive.

3.2 <u>ESD simulator current waveform verification</u>. To ensure proper simulator operation, the current waveform verification procedure shall be done, as a minimum, at the beginning of each shift when ESD testing is performed, or prior to testing after each change of the socket/board, whichever is sooner. If the simulator does not meet all requirements, all classification testing done since the last successful verification shall be repeated. At the time of initial facility certification and recertifications, photographs shall be taken of the waveforms observed as required by 3.2c through 3.2e and be kept on file for purposes of audit and comparison. (Stored digitized representations of the waveforms are acceptable in place of photographs.)

- a. With the DUT socket installed on the simulator, and with no DUT in the socket, place a short (figure 3015-1) across two pins of the DUT socket and connect one of the pins to simulator terminal A and the other pin to terminal B.

- b. Connect the current probe around the short near terminal B (see figure 3015-1). Set the simulator charging voltage source V<sub>S</sub> to 4,000 volts corresponding to step 4 of table I.

- c. Initiate a simulator pulse and observe the leading edge of the current waveform. The current waveform shall meet the rise time, peak current, and ringing requirements of figure 3015-2.

- d. Initiate a simulator pulse again and observe the complete current waveform. The pulse shall meet the decay time and ringing requirement of figure 3015-2.

- e. Repeat the above verification procedure using the opposite polarity  $(V_S = -4,000 \text{ volts}).$

- f. It is recommended that the simulator output be checked to verify that there is only one pulse per initiation, and that there is no pulse while capacitor C1 is being charged. To observe the recharge transient, set the trigger to the opposite polarity, increase the vertical sensitivity by approximately a factor of 10, and initiate a pulse.

| Step | V <sub>S</sub> (volts) | $I_P$ (amperes) |

|------|------------------------|-----------------|

| 1    | 500                    | 0.33            |

| 2    | 1,000                  | 0.67            |

| 3    | 2,000                  | 1.33            |

| 4    | 4,000                  | 2.67            |

TABLE I. Simulator charging voltage (V<sub>S</sub>) steps versus peak current (I<sub>P</sub>). <u>1</u>/

$\underline{1}$ / I<sub>P</sub> is the current flowing through R2 during the current waveform verification procedure and which is approximately V<sub>S</sub>/1,500 ohms.

### 3.3 Classification testing.

a. A sample of devices (see 4.c) shall be characterized for the device ESD failure threshold using the voltage steps shown in table I, as a minimum. Finer voltage steps may optionally be used to obtain a more accurate measure of the failure voltage. Testing may begin at any voltage step, except for devices which have demonstrated healing effects, including those with spark gap protection, which shall be started at the lowest step. Examination of known technology family input or output V/I damage characteristics (i.e., curve tracer), or other simplified test verification techniques may be used to validate the failure threshold (e.g., cumulative damage effects may be eliminated by retesting at the failure voltage step using a new sample of devices and possibly passing the step).

METHOD 3015.1 22 March 1989

- b. A new sample of devices shall be selected and subjected to the next lower voltage step used. Each device shall be tested using three positive and three negative pulses using each of the pin combinations shown in table II. A minimum of 1 second delay shall separate the pulses.

- c. The sample devices shall be electrically tested to subgroups 1 and 7 as applicable (room temperature dc parameters and functional tests).

- d. If one or more of the devices fail, the testing of 3.3b and 3.3c shall be repeated at the next lower voltage step used.

- e. If none of the devices fail, record the failure threshold determined in 3.3a. Note the highest step passed, and use it to classify the device according to table III.

|    | Terminal A<br>(Each pin individually<br>connected to terminal A<br>with the other floating) | Terminal B<br>(The common combination<br>of all like-named pins<br>connected to terminal B) |

|----|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 1. | All pins except $V_{ps1}$ <u>3</u> /                                                        | All V <sub>ps1</sub> pins                                                                   |

| 2. | All input and output pins                                                                   | All other input-output pins                                                                 |

TABLE II. Pin combinations to be tested. 1/2/

1/ Table II is restated in narrative form in 3.4 below.

- 2/ No connects are not to be tested.

- 3/ Repeat pin combination 1 for each named power supply and for ground (e.g., where V<sub>ps1</sub> is V<sub>DD</sub>, V<sub>CC</sub>, V<sub>SS</sub>, V<sub>BB</sub>, GND, +V<sub>S</sub>, -V<sub>S</sub>, V<sub>REF</sub>, etc.)

## 3.4 Pin combination to be tested.

- a. Each pin individually connected to terminal A with respect to the device ground pin(s) connected to terminal B. All pins except the one being tested and the ground pin(s) shall be open.

- b. Each pin individually connected to terminal A with respect to each different set of a combination of all named power supply pins (e.g., V<sub>SS1</sub> or V<sub>SS2</sub> or V<sub>SS3</sub> or V<sub>CC1</sub> or V<sub>CC2</sub>) connected to terminal B. All pins except the one being tested and the power supply pin or set of pins shall be open.

- c. Each input and each output individually connected to terminal A with respect to a combination of all the other input and output pins connected to terminal B. All pins except the input or output pin being tested and the combination of all the other input and output pins shall be open.

| Class 1 | 0 volt to 1,999 volts      |

|---------|----------------------------|

| Class 2 | 2,000 volts to 3,999 volts |

| Class 3 | 4,000 volts and above      |

|  | TABLE III. | Device ESD failure threshold classification. |

|--|------------|----------------------------------------------|

|--|------------|----------------------------------------------|

4. <u>SUMMARY</u>. The following details shall be specified in the applicable purchase order or contract, if other than specified herein.

- a. Post test electricals.

- b. Special additional or substitute pin combinations, if applicable.

- c. Sample size, if other than three devices.

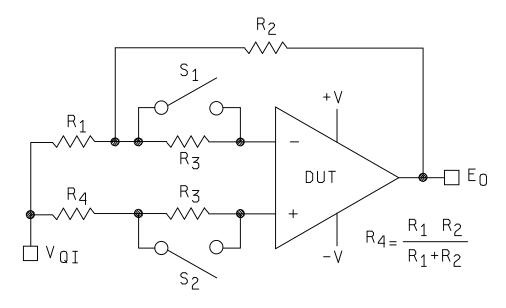

R2 = 1,500 ohms ±1 percent S1 = High voltage relay

$R1 = 10^6$  ohms to  $10^7$  ohms C1 = 100 picofarads ±10 percent

S2 = Normally closed switch

(Insulation resistance 10<sup>12</sup> ohms minimum)

(Bounceless, mercury wetted, or equivalent) (Open during discharge pulse and capacitance measurement)

NOTES:

- 1. The performance of this simulator circuit is strongly influenced by parasitics. Capacitances across relays and resistor terminals, and series inductance in wiring and in all components shall be minimized.

- 2. As a precaution against transients upon recharge of C1, the supply voltage V<sub>S</sub> may be reduced before switch S1 is returned to the charging position.

- 3. Piggybacking DUT sockets is not permitted during verification or classification testing.

- 4. Switching terminals A and B internal to the simulator to obtain opposite polarity is not recommended.

- 5. C1 represents the effective capacitance (see 2.3.2).

- 6. The current probe connection shall be made with double shielded cable into a 50-ohm termination at the oscilloscope. The cable length shall not exceed 3 feet.

FIGURE 3015-1. EDS classification test circuit (human body model).

NOTES:

- The current waveforms shown shall be measured as described in the waveform verification procedure of 3.2, 1. using equipment meeting the requirements of 2.

- The current pulse shall have the following characteristics: 2.

Tri (rise time) ------Less than 10 nanoseconds. Tdi (delay time) ------Less than 10 nanoseconds.  $I_p$  (peak current) -------Within ±10 percent of the  $I_p$  value shown in table II for the voltage step selected.  $I_r$  (ringing) ------The decay shall be smooth, with ringing, break points, double time constants or discontinuities less than 15 percent I<sub>p</sub> maximum, but not observable 100 nanoseconds after start of the pulse.

FIGURE 3015-2. EDS classification test circuit waveforms (human body model).

### METHOD 3016

## ACTIVATION TIME VERIFICATION

1. <u>PURPOSE</u>. This method establishes a means for assuring circuit performance during cold temperature start up. It defines an activation time for digital microelectronic devices such as TTL, DTL, RTL, ECL, and MOS and establishes the procedure necessary to accomplish the required testing. This method will ensure that a specified capability is available a known time interval after application of power.

- 1.1 <u>Definitions</u>. The following definitions shall apply for the purposes of this test method:

- a. Activation time. Activation time is defined as the time required for a device to become functionally operable after initial power is applied at the operating temperature extremes as specified by the applicable acquisition document. Note that activation time may be due to device and test system limitations, or both.

- b. Maximum and minimum. Maximum and minimum refer to an algebraic system where "max" represents the most positive value of the range and "min" represents the least positive value of the range. This is consistent with MIL-STD-1331, 30.1 and 30.2 for logic levels only.

- c. Maximum operating frequency. Maximum operating frequency is defined as the frequency of operation resulting from use of the minimum clock period for devices requiring a clock, or the frequency of operation resulting from the use of the minimum cycle time for devices not requiring a clock (such as memory devices) as specified in the applicable acquisition document.

- 1.2 <u>Symbols</u>. The following symbols and definitions shall apply for the purposes of this method.

### 1.2.1 Logic levels.

- V<sub>LW</sub> = worst case nominal low level logic input. The maximum allowable V<sub>IL</sub> specified in the applicable acquisition document minus 100 millivolts to allow for uncertainty in the drive level capability of high speed functional test equipment. (V<sub>LW</sub> = V<sub>IL</sub> (max) 100 mV).

- b. V<sub>HW</sub> = worst case nominal high level logic input. The minimum allowable V<sub>IH</sub> as specified by the applicable acquisition document plus 100 millivolts (V<sub>HW</sub> = V<sub>IH</sub> (min) + 100 mV).

- c. V<sub>OH</sub> (min) = minimum output high level specified for a digital microelectronic device.

- d. V<sub>OL</sub> (max) = maximum output low level specified for a digital microelectronic device.

### 1.2.2 Activation times.

- a.  $t_{AH}$  = maximum allowable activation time requirement, measured at V<sub>CC</sub> (max).

- b.  $t_{AL}$  = maximum allowable activation time requirement, measured at V<sub>CC</sub> (min).

2. <u>APPARATUS</u>. An instrument shall be provided which has the capability of applying sequential logic patterns to the device under test in accordance with the applicable acquisition document. The test instrument shall also be capable of applying nominal power supply voltage(s) and monitoring the output for the specified logic levels. The output monitoring circuit shall be of the double comparator type. The threshold voltage (trip point) for a comparator shall be  $V_{OL}$  (max) and  $V_{OH}$  (min) as specified in the applicable acquisition document. The test chamber shall be capable of maintaining the device under test at any specified test temperature.

3. <u>PROCEDURE.</u> The device shall be thermally stabilized at the minimum specified test temperature with no power applied to the device. The specified power supply voltage and the specified input logic patterns using  $V_{LW}$  and  $V_{HW}$  input voltage levels shall then be applied to the device under test and the outputs shall be monitored as described in section 2. This functional test shall be performed at a speed of at least 75 percent of F(max) using a test vector pattern as called out in the applicable acquisition document that has been designed for maximum fault coverage with no more than 4 K vectors.

METHOD 3016 29 November 1985

3.1 Activation time, maximum supply voltage,  $t_{AH}$ . Available test equipment has inherent delays (due to test program statement execution, voltage driver rise/fall times, etc.) between the time power is applied to the device under test and actual execution of the test. Therefore, the activation time stated in the applicable acquisition document should not be specified as less than the test system delay (even though device performance may be better). The test sequence shall be as follows.

3.1.1 <u>Device under test</u>. The device under test shall be thermally stabilized at the minimum specified test temperature, with the device unpowered.

3.1.2 Device under test shall then be powered up at  $V_{CC}$  (max). After waiting the time specified by  $T_{AH}$  (taking into account test equipment delays), the functional test pattern (using  $V_{LW}$  and  $V_{HW}$ ) logic levels) shall be applied to verify proper operation.

3.1.3 Repeat sequences 3.1.1 and 3.1.2 at the maximum specified test temperature.

3.2 <u>Activation time, minimum supply voltage</u>,  $t_{AL}$ . Repeat sequence described in 3.1.1 to 3.1.3 using a supply voltage of  $V_{CC}$  (min).

3.3 <u>Failure criteria</u>. The device must pass the functional test pattern and is a failure if the device fails any single pattern or vector in the specified test set.

4. <u>SUMMARY</u>. The following details, when applicable, shall be as specified in the applicable acquisition document:

- a. V<sub>IL</sub> (max).

- b. V<sub>IH</sub> (min).

- c. V<sub>OH</sub> (min).

- d. V<sub>OL</sub> (max).

- e. V<sub>CC</sub> (min).

- f. V<sub>CC</sub> (max).

- g. Test temperature (min and max operating temperature).

- h. t<sub>AH</sub> (max).

- i. t<sub>AL</sub> (max).

- j. Functional test pattern (see 3).

- k. Maximum operating frequency, F (max) (see 1.1.c).

### METHOD 3017

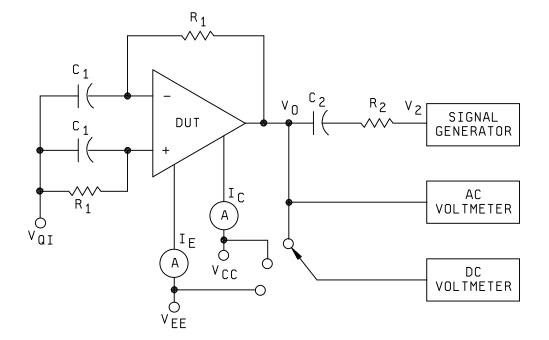

### MICROELECTRONICS PACKAGE DIGITAL SIGNAL TRANSMISSION

1. <u>PURPOSE</u>. This method establishes the means of evaluating the characteristic impedance, capacitance, and delay time of signal lines in packages used for high frequency digital integrated circuits. It is intended to assure a match between circuit performance and interconnecting wiring to minimize signal degradation.

1.1 Definitions.

1.1.1 <u>Characteristic impedance</u>. The impedance that a section of transmission line exhibits due to its ratio of resistance and inductance to capacitance.

1.1.2 <u>Delay time</u>. The time delay experienced when a pulse generated by a driver with a particular drive impedance is propagated through a section of transmission line.

1.2 Symbols.

- R: Resistance

- L: Inductance

- C: Capacitance

- tpd: Propagation delay time

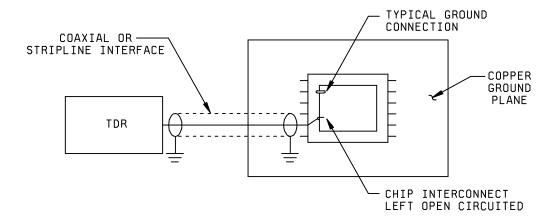

2. <u>APPARATUS</u>. The approaches for transmission performance measurements shall include a suitable time domain reflectometer (TDR) (see 2.1) and dc resistance measuring equipment (see 2.2).

2.1 <u>Time domain reflectometer</u>. The TDR used for this test shall have a system rise time for the displayed reflection that is not less than 5 times and preferably 10 times the rise time (method 3004) for the candidate integrated circuits to be packaged. Interconnecting cables and fixtures shall be designed such that this ratio is not degraded due to reflections and ringing in the test setup.

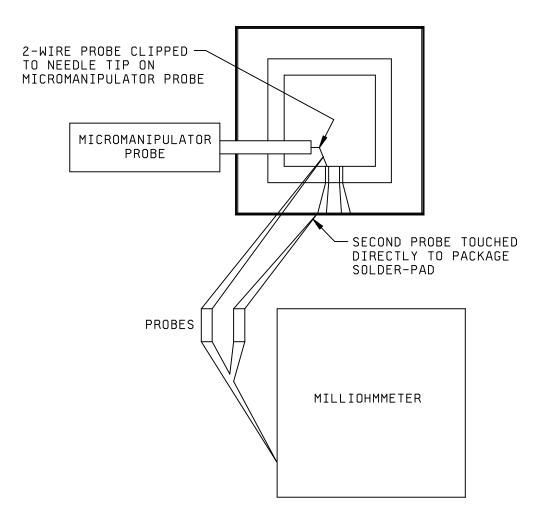

2.2 <u>DC resistance</u>. DC resistance measuring equipment and probe fixtures shall be capable of measuring the resistance of the package leads and the chip-to- package interconnect media with an accurancy of no greater than ±10 percent of the actual value including errors due to the mechanical probing interface contact resistance.

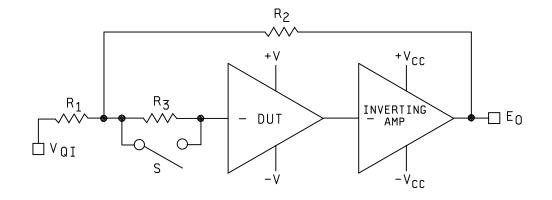

3. <u>PROCEDURE</u>. The test equipment configuration shall be as shown on figure 3017-1 using a time domain reflectometer as specified (see 2). The characteristic impedance ( $Z_0$ ), propagation time ( $t_{pd}$ ), resistance and load capacitance ( $C_L$ ) shall be measured for all representative configurations as determined by a review of the package drawings, and the intended applications (see 3.2 through 3.3).

3.1 General considerations.

3.1.1 <u>TDR measurements</u>. Accurate measurement of transmission performance of a package pin using a TDR requires careful design and implementation of adapter fixtures to avoid reflections due to transmission line discontinuities in the cables and junctions between the TDR and the package being tested. The accuracy of the measurement will be enhanced if the coaxial cable used to interface to the package is of a characteristic impedance as close as possible to the package pin impedance. The interface to the package should be a soldered connection and mechanical design of the actual coax-to-package interface should minimize the length of the uncontrolled impedance section. Stripline interfaces are the best method for surface mount package styles.

3.1.2 <u>Test configurations</u>. Obtaining a good high frequency ground is also important. Connection of the package ground plane (if the package design has one) to the test set-up ground plane should be accomplished with a pin configuration similar to actual usage in the intended package applications.

Pin selection for testing may vary according to package complexity. For packages with very symmetrical pin configurations only a few pins need be tested but configurations must include pins adjacent and nonadjacent to the ground pins. Packages with complex wiring and interconnection media should be tested 100 percent.

METHOD 3017 29 May 1987

3.2 <u>Test procedure for package transmission characteristics</u>. Using a section of coaxial cable of known, calibrated characteristic impedance ( $Z_{Ref}$ ) as a reference measure the minimum ( $Z_{Min}$ ) maximum ( $Z_{Max}$ ) and average ( $Z_{o}$ ) values of reflection coefficient ( $_{\odot}$ ) for the section of line on the TDR display that has been carefully determined to be the package pin (locate using zero-length short circuits).

Calculate characteristic impedance (Z<sub>o</sub>) for each of the cases from the formula:

$$Z_0 = Z_{Ref} x \frac{(l+\rho)}{(l-\rho)}$$

3.2.2 <u>Delay time measurement</u>. From the TDR display of 3.2.1 measure the time difference in picoseconds from the point identified as the start of the exterior package pin  $(t_1)$  to the chip interface point  $(t_2)$  ( $\triangle t = t_1 - t_2$ )

Form the package design drawings, determine the physical length of the package run (L)

Time delay

$$t_{pd} = \frac{\Delta t}{L}$$

3.2.3 Load capacitance calculation.

Load capacitance

$$C_L = \frac{t_{pd}}{Z_o}$$

3.2.4 Load inductance calculation.

Load inductance (series) =

$$\frac{(t_{pd})^2}{C_L}$$

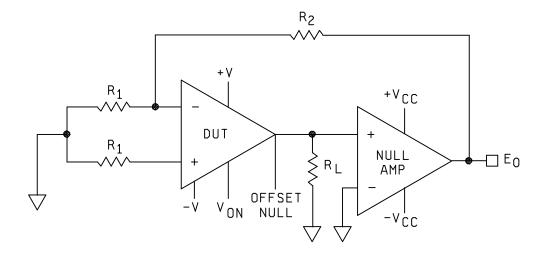

#### 3.3. Series resistance measurement.

Using the test setups of figure 3017-2, separately measure the dc resistance of the chip-to-package interface media ( $R_M$ ) and the package lead ( $R_L$ ).

- 4. <u>SUMMARY</u>. The following details, when applicable, shall be specified in the applicable acquisition document:

- a. Z<sub>Max</sub>.

- b. Z<sub>Min</sub>.

- c. Z<sub>o</sub> (max).

- d. Z<sub>o</sub> (min).

- e. t<sub>pd</sub> (max).

- f. t<sub>pd</sub> (min).

- g.  $C_L$  (max).

- h.  $C_{L}$  (min).

- $\text{i.} \quad L_{L} \text{ (max).}$

- j.  $L_L$  (min).

- k. R<sub>M</sub> (max).

- I. R<sub>M</sub> (min).

- m. R<sub>L</sub> (max).

- n. R<sub>L</sub> (min).

- o. Package pins to be tested.

- p. Package ground configuration.

FIGURE 3017-1. Time domain reflectometer test setup.

METHOD 3017 29 May 1987

FIGURE 3017-2. Test setup for dc resistance using a milliohmmeter.

### METHOD 3018

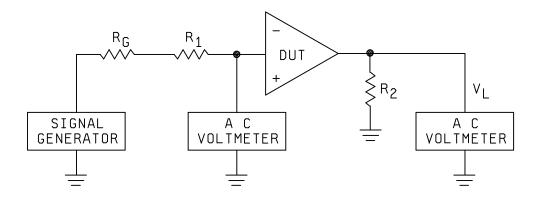

# CROSSTALK MEASUREMENTS FOR DIGITAL MICROELECTRONICS DEVICE PACKAGE

1. <u>PURPOSE</u>. This method establishes the means of measuring the level of cross-coupling of wideband digital signals and noise between pins in a digital microcircuit package. The method may be used to gather data that are useful in the prediction of the package's contribution to the noise margin of a digital device. The technique is compatible with multiple logic families provided that the drive and load impedance are known.

1.1 Definitions.

1.1.1 Crosstalk. Signal and noise waveforms coupled between isolated transmission lines, in this case, package conductors.

1.1.2 <u>Coupling capacitance</u>. The effective capacitance coupling between a pair of conductors in a package as measured by the time constant of the charge pulse applied on one line and measured on the other.

1.1.3 <u>Noise pulse voltage</u>. The voltage of a crosstalk measured at the minimum noise pulse width as measured on a receiver input line.

1.1.4 Peak noise voltage. The peak value of the noise pulse measured on a receiver input line.

1.2 <u>Symbols</u>. The following symbols shall apply for the purpose of this test method and shall be used in accordance with the definitions provided (see 1.2.1 and 1.2.2).

- 1.2.1 Logic levels.

- Vol(max): The maximum output low level specified in a logic system.

- V<sub>OH</sub>(min): The minimum output high level specified in a logic system.

- V<sub>IL</sub>(max): The maximum allowed input low voltage level in a logic system.

- V<sub>IH</sub>(min): The minimum allowed input high level in a logic system.

#### 1.2.2 Noise pulse width.

- $t_{PL}$ : The low level noise pulse width, measured at the V<sub>IL</sub> (max) level (see method 3013).

- $t_{PH}$ : The high level noise pulse width, measured at the V<sub>IH</sub> (min) level (see method 3012).

#### 1.2.3 Transition times (see method 3004).

- t<sub>tLH</sub>: Rise time. The transition time of the output from the 10 percent to the 90 percent of the high voltage levels with the output changing from low to high.

- $t_{tHL}$ : Fall time. The transition times from the 90 percent to the 10 percent of the high voltage level with the output changing from high to low.

## 1.2.4 Crosstalk parameters.

- C<sub>c</sub>: Coupling capacitance (see 1.1.2).

- V<sub>N</sub>: Noise pulse voltage (see 1.1.3).

- V<sub>NPK</sub>: Peak noise voltage (see 1.1.4).

2. <u>APPARATUS</u>. The apparatus used for crosstalk measurements shall include a suitable source generator (see 2.1), wideband oscilloscope (see 2.2), low capacitance probe (see 2.3) and load resistors (see 2.4).

2.1 <u>Source generator</u>. The source generator for this test shall be capable of duplicating (within 5 percent) the transition times,  $V_{OH}$  and  $V_{OL}$  levels of the logic system(s) being considered for application using the package style under evaluation. The source generator shall have a nominal characteristic source impedance of 50 ohms.

2.2 <u>Wideband oscilloscope</u>. The oscilloscope used to measure the crosstalk pulse shall have a display risetime that is less than 20 percent of the risetime of the logic systems being considered for application in the package style under evaluation. A sampling-type oscilloscope is recommended.

2.3 Low capacitance probe. The interface between the oscilloscope and the unit under test shall be a high impedance low capacitance probe. The probe impedance shall be 10 k $_{\Omega}$ , minimum and the capacitance shall be 5 pF, maximum, unless otherwise specified in the acquisition document.

2.4 <u>Load resistor</u>. The load resistors specified for this test shall be low inductance, low capacitance, chip style resistors with a tolerance of ±5 percent. Load resistor values(s) shall be specified by the acquisition document to match the load impedance levels of the application logic family for a single receiver load.

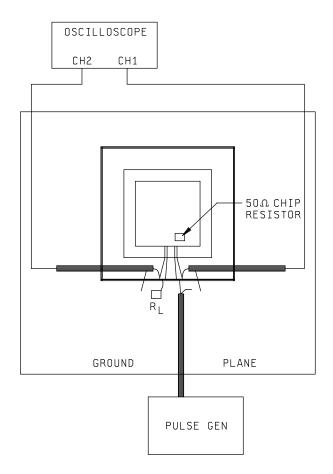

3. <u>PROCEDURE</u>. The test equipment configuration shall be as shown on figure 3018-1 using a source generator, oscilloscope, probe and loads as specified (see 2). Measurements shall be made of coupling capacitance, (see 3.2) and if required by the acquisition document, of noise pulse voltage, peak noise pulse voltage, and noise pulse width (see 3.3).

## 3.1 General considerations.

3.1.1 Package test configuration. It is important to ground the package using the same pins as would be used in the microcircuit application. If the package has an internal ground plane or ground section, this should be connected via package pin(s) to the exterior test set-up ground plane. The package should be connected to the test set-up with coaxial cable or stripline. Unshielded conductor medium should not be used between the signal source and package. Coaxial shields must be grounded at both ends of the cable. Package sockets should not be used unless these are to be part of the microcircuit application configuration. Package leads must be formed and trimmed as specified in the application. Package-to-chip interconnecting media shall be installed in the package and used to connect to the load resistors.

3.1.2 <u>Pin selection</u>. For simple packages with symmetrical, parallel pin conductors, only a sample of pin combinations need be tested. Unless otherwise specified by the acquisition document, all combinations adjacent to the ground pin(s) and combinations opposite the ground pin(s) shall be tested, as a minimum. Complex packages with nonparallel conductors or multilayer wiring shall be tested for all adjacent-pair combinations, unless otherwise specified.

3.2 <u>Coupling capacitance measurements</u>. Connect the test equipment as shown on figure 3018-1. Use a 50 ohm chip resistor load in the driven pin channel, unless otherwise specified. For the pick-up channel, use the load resistor value(s) as specified by the acquisition document. (Load resistor values should be set such that the parallel combination of load resistance and probe impedance matches as closely as practical the specified load impedance of a single receiver in the logic system to be used in the microcircuit application.) Check the residual cross-coupling of the measuring set-up by touching the probe to the pick-up channel load before the pick-up pin is connected to the resistor. Measure and record the peak pulse voltage observed. This peak pulse reading must be less than 50 percent of the reading observed with the pin connected to the resistor for a reading to be valid. Adjust the test set-up cable orientation and configuration to minimize this residual cross-coupling.

Connect the pick-up pins to the load resistor and adjust the pulse width so that the time required to charge the coupling capacitance to 0 V can be observed. Measure the time at the 63 percent voltage point on the waveform (T) and calculate coupling capacitance ( $C_c$ ) as follows:

Determine

$$R_{Total} = \frac{R_{Probe} \times R_{Load}}{R_{Probe} + R_{Load}}$$

$C_{Total} = \frac{T}{R_{Total}}$

$C_{C} = C_{Total} - C_{Probe}$

Values of  $C_c$  can be used as a relative measure for comparison of potential crosstalk among several packages to a standard package. The coupling capacitance ( $C_c$ ) can also be used to predict levels of crosstalk for various logic systems or circuit configurations by performing a pulse response analysis using a circuit simulator.

3.3 <u>Noise pulse measurements</u>. Using the same test setup as in 3.2, measure the crosstalk noise pulse voltage at the minimum noise pulse width specified for the logic system or as specified by the acquiring agency.

Measure the peak noise voltage value of the coupled crosstalk.

- 4. <u>SUMMARY</u>. The following details, when applicable, shall be specified in the acquisition document:

- a. C<sub>c</sub>.

- b. V<sub>OL</sub> (max).

- c. V<sub>OH</sub> (min).

- d. V<sub>IL</sub> (max).

- e. V<sub>IH</sub> (min).

- f. t<sub>PL</sub>.

- g. t<sub>PH</sub>.

- $h. \quad t_{tLH}.$

- i. t<sub>tHL</sub>.

- j. V<sub>N</sub>.

- k. V<sub>NPK</sub>.

MIL-STD-883E

FIGURE 3018-1. Test setup for coupling capacitance measurement.

METHOD 3018 29 May 1987

#### METHOD 3019.1

#### GROUND AND POWER SUPPLY IMPEDANCE MEASUREMENTS FOR MICROELECTRONICS DEVICE PACKAGE

1. <u>PURPOSE</u>. This method establishes the means of measuring the series impedance of the ground and power supply circuit pin configurations for packages used for complex, wide bandwidth microcircuits. The method provides data that are useful in the evaluation of the relative performance of various packages and can be used to predict the contribution of the package to power supply noise and ground noise.

1.1 Definition.

1.1.1 <u>Ground or power supply impedance</u>. The series combination of inductive reactance and resistance exhibited by all of the conductor paths between the semiconductor chip interface and the exterior package interface in either the ground circuit or the power supply circuit. The impedance of a series inductive circuit is defined by the equation:

$$Z = \sqrt{R^2 + X^2 L}$$

1.2 <u>Symbols</u>. The following symbols shall apply for purposes of this test method and shall be used in conjunction with the definition provided in 1.1.

- L<sub>G</sub>: Series inductance of the ground circuit path in a package (henries).

- L<sub>p</sub>: Series inductance of the power supply circuit path in a package (henries).

- X<sub>G</sub>: Series inductive reactance of ground path =  $2 \pi fL_p$  (ohms).

- $X_p$ : Series inductive reactance of power supply path = 2  $\pi$  fL<sub>p</sub> (ohms).

- f: Frequency (Hz).

- $f_{tr}$ : Frequency of primary component of digital pulse transition = <u>1</u> (Hz).

- f<sub>tp</sub>: Frequency related to noise pulse width specified for the logic system:

$$f_{tp} = \frac{1}{t_{Pmin}}^{(Hz)}$$

- t: Transition time from logic system. Equal to the smaller value of low to high or high to low transition.

- Z<sub>G</sub>: Series impedance of ground path at frequency:

$$Z_G = \sqrt{R_G^2 + Z_G^2}$$