## SIX-Channel Digital Still Camera Power Supplies

#### Features:

- ◆ 95% Efficient Step-Up (CH1) Converter

- ♦ 95% Efficient Step-Down (CH3) Converter

- ◆ Combine CH1 and CH3 for 90% Efficient Boost-Buck

- ◆ Low Start-Up Voltage : 1.2V (CH1)

- CH2 Converter as Either Step-Up or Step-Down

- Built-in Soft-Start Function

- ◆ Independent On/Off Control for CH1~CH6

- Regulate LED Current for 4, 6 or More LEDs

- Open LED Overvoltage Protection

- Transformerless Inverting Controller for CCD Bias (CAT7301)

- ◆ Up to 1MHz Operating Frequency

- ◆ Built-in Overload Protection Function

- ♦ Shutdown Current < IuA</p>

- ◆ QFN40 Package

- RoHS Compliant (100% Green available)

### **General Description:**

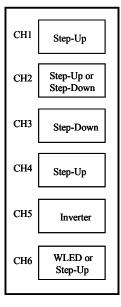

The CAT7301/CAT7302 provide a complete power supply solution for digital still cameras. They improve performance, component count, and size compared to conventional controllers in 2-cell AA, 1-cell Li-Ion, and dual-battery designs. The CAT7301 / CAT7302 include six high efficiency dc-dc conversion channels: three current mode converters and three voltage mode controllers. The current-mode converters, CH1, CH2 and CH3, with on-chip MOSFETs provide up to 95% efficiency for critical power supplies. The CH2 can be configured as either step-up or step-down converter. The CH4,

CH5 and CH6 voltage mode controllers operate with external MOSFETs to optimum design flexibility. The CH5 is the inverting controller in CAT7301 and the step-up controller in CAT7302. The CH6 can be used as switch-mode boost current source for white LEDs or as a conventional step-up controller.

### **Application:**

- Digital Still Camera

- PDAs and Smart Phones

- ◆ PMP

- CCD Devices

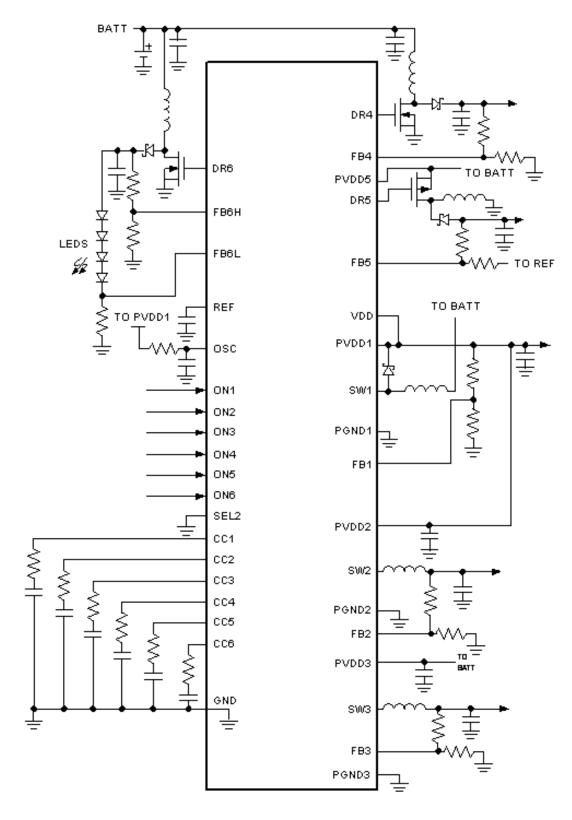

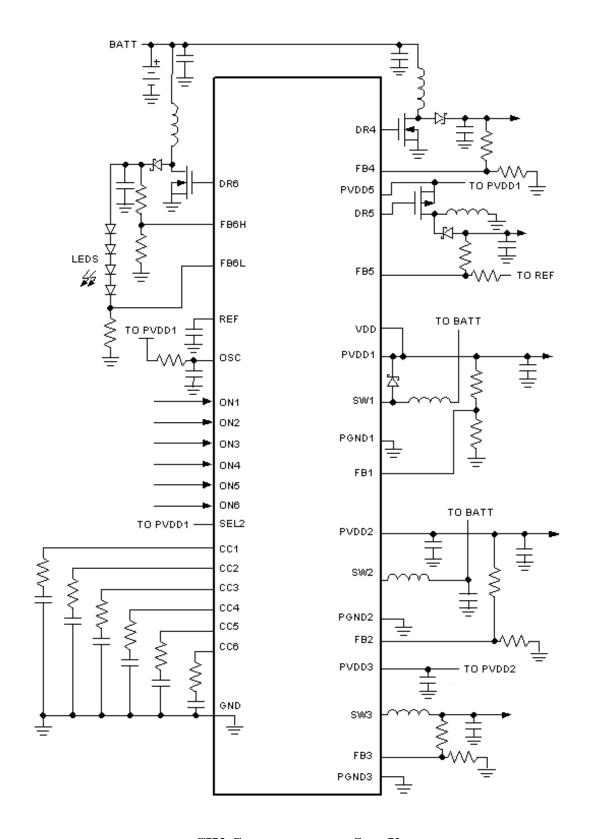

### Simplified Block Diagram:

CAT7302

1/12/2006 1 www.chipadvanced.com

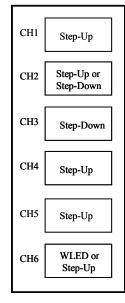

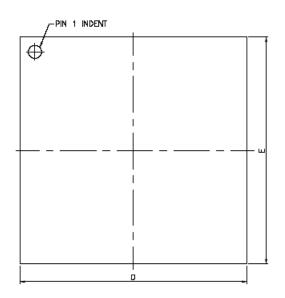

## **Pin Configuration:**

40 LD 6mm x 6mm QFN-40

### **Ordering Information:**

| Part Number | Package   | Ship              |

|-------------|-----------|-------------------|

| CAT7301CF   | 40-Ld QFN | 2500/Tono % Dool  |

| CAT7302CF   | (Green)   | 2500/ Tape & Reel |

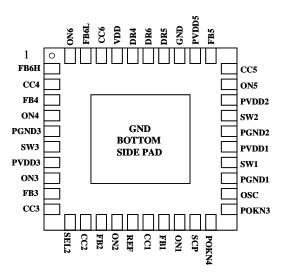

### **Function Block Diagram:**

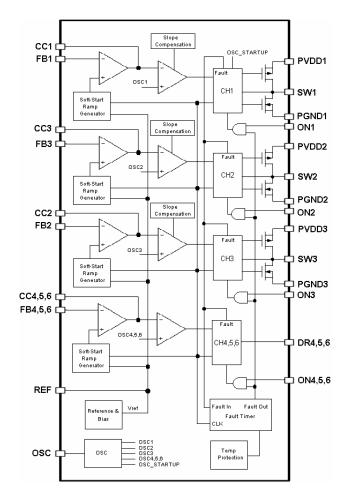

## **Typical Application:**

CH2 Converter acts as Step-Down

CH2 Converter acts as Step-Up

\*note: The recommended applications shall be customer design-in orientation to fit each customers demand. Based on the nature of customers demand-oriented, please contact CAT or agent for design support service.

### **Absolute Maximum Ratings**

1. VDD, PVDD1, ON\_, FB\_, SCP, POKN3, POKN4,

SEL2 to GND \_\_\_\_\_\_-0.3V to +6V

2. PGND to GND \_\_\_\_\_\_-0.3 to +0.3V

3. DR4, DR6, PVDD5, PVDD2, PVDD3 to GND

-0.3V to PVDD1 + 0.3V

4. DR5 to GND \_\_\_\_\_-0.3V to PVDD5 + 0.3V

5. SW1 Current \_\_\_\_\_\_3.6A

| 6. SW2 Current                  | 3.6A                  |

|---------------------------------|-----------------------|

| 7. SW3 Current                  | 2.25A                 |

| 8. REF, OSC, CC_ to GND         | -0.3V to PVDD1 + 0.3V |

| 9. ESD Classification           | Class 2               |

| 10. Junction Temperature Range  | :125°C                |

| 11. Operating Temperature       |                       |

| 12. Storage Temperature Range   | 40°C to 150°C         |

| 13. Lead Temperature (Soldering | g 10s)260°C           |

\*note: The IC has a protection circuit against static electricity. Do not apply high static electricity or high voltage that exceeds the performance of the protection circuit to the IC.

#### **Electrical Characteristic:**

$(V_{PVDD1} = V_{VDD} = V_{PVDD2} = V_{PVDD3} = V_{PVDD5} = 3.6V$ , TA = 0°C to +85°C, unless otherwise noted.)

| Parameter                                             | Test Conditions                                                   | Min  | Тур  | Max  | Units |

|-------------------------------------------------------|-------------------------------------------------------------------|------|------|------|-------|

| SYSTEM                                                |                                                                   |      |      |      |       |

| Input Voltage Range                                   |                                                                   |      |      | 5.5  |       |

| CH1 Minimum Startup Voltage                           | LOAD < 1mA, TA = +25°C;                                           |      | 1.2  |      | V     |

| Shutdown Supply Current into VDD                      | VDD = 3.6V                                                        |      | 0.1  | 10   | uA    |

| CH1 Switch-Off Supply Current into VDD                | ON1 = 3.6V, FB1 = 1.5V (not include switching losses)             |      | 300  | 450  | uA    |

| CH1, CH3 Switch-Off Supply Current into VDD           | ON1 = ON3 = 3.6V, FB1 = FB3 = 1.5V (not include switching losses) |      | 450  | 700  | uA    |

| CH1, CH2 Switch-Off Supply Current into VDD           | ON1 = ON2 = 3.6V, FB1 = FB2 = 1.5V (not include switching losses) |      | 450  | 700  | uA    |

| CH1, CH4 Switch-Off Supply Current from VDD and PVDD1 | ON1 = ON4 = 3.6V, FB1 = FB4 = 1.5V (not include switching losses) |      | 400  | 650  | uA    |

| REFERENCE                                             |                                                                   |      |      |      | •     |

| Reference Output Voltage                              | I <sub>REF</sub> = 20uA                                           | 1.23 | 1.25 | 1.27 | V     |

| Reference Load Regulation                             | 10uA < I <sub>REF</sub> < 200uA                                   |      | 5    | 10   | mV    |

| Reference Line Regulation                             | 2.7V < PVDD1 < 5.5V                                               |      |      | 5    | mV    |

| OSCILLATOR                                            |                                                                   |      |      |      |       |

| Frequency                                             | $R_{OSC} = 47k\Omega$ , $C_{OSC} = 100pF$                         | 240  | 320  | 400  | kHz   |

| Adjustment Range                                      |                                                                   | 100  |      | 1000 | kHz   |

| OSC Discharge Pulse Width                             |                                                                   |      | 200  |      | nS    |

| CH1                                                    |                                               |      |       |      | _      |

|--------------------------------------------------------|-----------------------------------------------|------|-------|------|--------|

| Startup-to-Normal Operating                            | Distance falling adva                         |      | 2.5   |      | V      |

| Threshold                                              | Rising or falling edge                        |      | 2.5   |      | V      |

| Voltage Adjust Range                                   |                                               | 3.0  |       | 5.5  | V      |

| Startup-to-Normal Operating                            |                                               |      | 80    |      | mV     |

| Threshold Hysteresis                                   |                                               |      | 80    |      | IIIV   |

| Start Delay of ON2, ON3, ON4,                          |                                               |      |       |      | osc    |

| ON5, and ON6 after CH1 in                              |                                               |      | 1024  |      | cycles |

| Regulation                                             |                                               |      |       |      | Cycles |

| FB1 Regulation Voltage                                 |                                               | 1.23 | 1.25  | 1.27 | V      |

| FB1 to CC1 Transconductance                            | FB1 = CC1                                     | 80   |       | 185  | uS     |

| FB1 Input Leakage Current                              | FB1 = 1.25V                                   | -100 |       | 100  | nA     |

| Current-Sense Amplifier                                |                                               |      | 0.275 |      | V/A    |

| Transresistance                                        |                                               |      | 0.275 |      | V/A    |

| PVDD1 Leakage Current                                  | V <sub>SW1</sub> = 0V, PVDD1 = 3.6V           |      |       | 5    | uA     |

| SW1 Leakage Current                                    | V <sub>SW1</sub> = PVDD1 = 3.6V               |      |       | 5    | uA     |

| Maximum Duty Cycle                                     | FB1 = 1V                                      | 80   | 85    | 90   | %      |

| N-Channel Switch On-Resistance                         |                                               |      | 95    | 150  | mΩ     |

| P-Channel Switch On-Resistance                         |                                               |      | 150   | 250  | mΩ     |

| N-Channel Current Limit                                |                                               | 1.8  | 2.1   | 2.4  | Α      |

| P-Channel Turn-Off Current                             |                                               |      | 20    |      | mA     |

| Startup Current Limit                                  | PVDD1 = 1.8V                                  |      | 450   |      | mA     |

| Startup Frequency                                      | PVDD1 = 1.8V                                  | 200  |       |      | kHz    |

| CH2                                                    |                                               |      |       |      |        |

| FB2 Regulation Voltage                                 |                                               | 1.23 | 1.25  | 1.27 | V      |

| CH2 Step-Up Voltage Adjust Range                       | SEL2 = PVDD1                                  | 3    |       | 5    | V      |

| CH2 Step-Down Voltage Adjust Range                     | SEL2 = GND, PVDD2 must be greater than output | 2.45 |       | 5    | V      |

| PVDD2 Undervoltage Shutdown in Step-Down Mode          | SEL2 = GND                                    | 2.45 | 2.5   | 2.55 | V      |

| FB2 to CC2 Transconductance                            | FB2 = CC2                                     | 80   |       | 185  | uS     |

| FB2 Input Leakage Current                              | FB2 = 1.25V                                   | -100 |       | 100  | nA     |

| Step-Up mode Current-Sense Amplifier Transresistance   |                                               |      | 0.25  |      | V/A    |

| Step-Down mode Current-Sense Amplifier Transresistance |                                               |      | 0.5   |      | V/A    |

| Maximum Duty Cycle                                     | FB2 = 1V                                      | 80   | 85    | 90   | %      |

| SW2 Leakage Current                                    | V <sub>SW2</sub> = 0 to 3.6V , PVDD1= 3.6V    |      |       | 5    | uA     |

|                                   | <u> </u>                                    |       | 1    | 1    | _          |

|-----------------------------------|---------------------------------------------|-------|------|------|------------|

| Soft-Start Interval               |                                             |       | 4096 |      | OSC cycles |

| N-Channel Switch On-Resistance    |                                             |       | 95   | 150  | mΩ         |

| P-Channel Switch On-Resistance    |                                             |       | 150  | 250  | mΩ         |

| Step-Up Mode Switch Current Limit |                                             | 1.8   | 2.1  | 2.4  | Α          |

| Step-down Mode Switch Current     |                                             | _     |      |      |            |

| Limit                             |                                             | 0.7   | 0.8  | 0.95 | A          |

| Step-Up Mode Synchronous          |                                             |       |      |      |            |

| Rectifier Turn-Off Current        |                                             |       | 20   |      | mA         |

| Step-Down Mode Synchronous        |                                             |       | -00  |      |            |

| Rectifier Turn-Off Current        |                                             |       | 20   |      | mA         |

| СНЗ                               |                                             | •     |      | •    | •          |

| Voltage Adjust Range              |                                             | 1.25  |      | 5    | V          |

| FB3 Regulation Voltage            |                                             | 1.23  | 1.25 | 1.27 | V          |

| FB3 to CC3 Transconductance       | FB3 = CC3                                   | 80    |      | 185  | uS         |

| FB3 Input Leakage Current         | FB3 = 1.25V                                 | -100  |      | 100  | nA         |

| Current-Sense Amplifier           |                                             |       | 0.5  |      | >//^       |

| Transresistance                   |                                             |       | 0.5  |      | V/A        |

| SW3 Leakage Current               | V <sub>SW3</sub> = 0 to 3.6V , PVDD1 = 3.6V |       |      | 5    | uA         |

| Soft-Start Interval               |                                             |       | 2048 |      | OSC cycles |

| N-Channel Switch On-Resistance    |                                             |       | 95   | 150  | mΩ         |

| P-Channel Switch On-Resistance    |                                             |       | 150  | 250  | mΩ         |

| P-Channel Current Limit           |                                             | 0.65  | 0.77 | 0.9  | A          |

| N-Channel Turn-Off Current        |                                             |       | 20   |      | mA         |

| POKN3 Output Low Voltage          | 0.1mA into POKN3                            |       |      | 0.1  | V          |

| POKN3 Leakage Current             | ON1 = GND                                   |       |      | 1    | uA         |

| CH4, CH5, CH6                     |                                             |       |      |      |            |

| FB4, FB6H Regulation Voltage      |                                             | 1.23  | 1.25 | 1.27 | V          |

| FB5 Regulation Voltage            |                                             | -0.01 | 0    | 0.01 | V          |

| FB6L Regulation Voltage           |                                             | 0.19  | 0.2  | 0.21 | V          |

| Maximum Duty Cycle                | FB_ = 1V                                    | 80    | 85   | 90   | %          |

| PVDD5 Undervoltage Lockout        |                                             | 2.45  | 2.5  | 2.55 | V          |

| FB_ to CC_Transconductance        | FB_ = CC_                                   | 80    |      | 185  | uS         |

| FB_ Input Leakage Current         | FB_ = 1.25V                                 | -100  |      | 100  | nA         |

| DR_ Driver Resistance             | Output high or low                          |       | 2.5  | 7    | Ω          |

| DR_ Drive Current                 | Sourcing or sinking                         |       | 0.5  |      | Α          |

| Soft-Start Interval               |                                             |       | 4096 |      | OSC        |

| _                                                |                         |          |        |     | cycles      |

|--------------------------------------------------|-------------------------|----------|--------|-----|-------------|

| POKN4 Output Low Voltage                         | 0.1mA into POKN4        |          |        | 0.1 | V           |

| POKN4 Leakage Current                            | ON1 = GND               |          |        | 1   | uA          |

| OVERLOAD PROTECTION                              |                         | ·        |        |     |             |

| Overload Protection Fault Delay                  |                         |          | 100000 |     | osc         |

| SCP Output Low Voltage                           | 0.1mA into SCP          |          |        | 0.1 | cycles<br>V |

| SCP Leakage Current                              | ON1 = PVDD1, FB1 = 1.5V |          |        | 1   | uA          |

| THERMAL-LIMIT PROTECTION                         |                         |          |        |     | l .         |

| Thermal Shutdown                                 |                         |          | 160    |     | °C          |

| Thermal Hysteresis                               |                         |          | 20     |     | °C          |

| LOGIC INPUTS (ON_, SUSD)                         |                         | ·        |        |     |             |

| ON1 Input Low Voltage                            |                         |          |        | 0.5 | V           |

| ON1 Input High Voltage                           | PVDD1 < 1.8V            | PVSU-0.2 |        |     | V           |

| ON Imput riigii voitage                          | 1.8V <= PVDD1 < 5.5V    | 1.6      |        |     | V           |

| ON2, ON3, ON4, ON5, ON6, SEL2<br>Input Low Level | 2.7V < PVDD1 < 5.5V     |          |        | 0.5 | ٧           |

| ON2, ON3, ON4, ON5, ON6, SEL2 Input High Level   | 2.7V < PVDD1 < 5.5V     | 1.6      |        |     | V           |

| SEL2 Input Leakage Current                       |                         |          |        | 1   | uA          |

| ON_ impedance to GND                             |                         |          | 330    |     | kΩ          |

#### Notes:

### **Pin Description**

#### 1. FB6H

The CH6 Controller Voltage Feedback Input. Connect a resistive voltage-divider from the CH6 converter output to FB6H to set the output voltage. The feedback threshold is 1.25V. FB6H can provide conventional voltage feedback (with FB3L grounded) or open-LED protection in white LED drive circuits.

#### 2. CC4

The CH4 Controller Compensation Pin. Connect a series resistor-capacitor from this pin to GND to

compensate the converter control loop.

#### 3. FB4

The CH4 Controller Feedback Input. The feedback threshold is 1.25V.

#### 4. ON4

The CH4 Controller On/Off Input. Logic high = on; however, turn-on is locked out until 1024 OSC cycles after the CH1 Converter has reached regulation.

#### **5. PGND3**

<sup>\*</sup> Specifications are subjected to change without notice.

<sup>\* 3</sup> PENTENTS PENDING for CAT7301/CAT7302.

The CH3 Converter On Chip MOSFET Ground.

#### 6. SW3

The CH3 Converter Switching Pin. Connect to the inductor of the CH3 converter.

#### **7. PVDD3**

The CH3 Converter On Chip MOSFET Power Supply. Bypass to GND with a 1uF ceramic capacitor.

#### 8. ON3

The CH3 Converter On/Off Input. Logic high = on; however, turn-on is locked out until 1024 OSC cycles after the CH1 Converter has reached regulation.

#### 9. FB3

The CH3 Converter Feedback Input. The feedback threshold is 1.25V.

#### 10. CC3

The CH3 Converter Compensation Pin. Connect a series resistor-capacitor from this pin to GND to compensate the converter control loop.

#### 11. SEL2

The Configures the CH2 Converter as a Step-Up or a Step-Down. This function can not change on-the-fly. With SEL2 connected to VDD, the CH2 is configured as a step-up and PVDD2 is the converter output. With SEL2 connected to GND, the CH2 is configured as a step-down and PVDD2 is the on chip MOSFET power input.

#### 12. CC2

The CH2 Converter Compensation Pin. Connect a series resistor-capacitor from this pin to GND to compensate the converter control loop.

#### 13. FB2

The CH2 Converter Feedback Input. The feedback threshold is 1.25V.

#### 14. ON2

The CH2 Converter On/Off Input. Logic high = on; however, turn-on is locked out until 1024 OSC cycles after the CH1 Converter has reached regulation.

#### 15. REF

The Reference Output. Bypass REF to GND with a 0.1uF or greater capacitor. The maximum allowed REF load is 200uA.

#### 16. CC1

The CH1 Converter Compensation Pin. Connect a series resistor-capacitor from this pin to GND to compensate the converter control loop.

#### 17. FB1

The CH1 Converter Feedback Input. The feedback threshold is 1.25V.

#### 18. ON1

The CH1 Converter On/Off Control. Logic high = on. All other ON\_ pins are locked out until 1024 OSC cycles after the CH1 DC-to-DC converter output has reached its final value.

#### 19. SCP

The Open-Drain, Short-Circuit-Protection Flag Output. SCP goes open when overload protection occurs. Under normal operation, SCP pulls low.

#### **20. POKN4**

Open-Drain, Active-Low, Power-OK Signal for CH4 Controller. POKN4 goes low when the CH4

controller has successfully completed soft-start.

#### **21. POKN3**

Open-Drain, Active-Low, Power-OK Signal for CH3 Converter. POKN3 goes low when the CH3 has successfully completed soft-start.

#### 22. OSC

Oscillator Control. Connect a timing capacitor from OSC to GND and a timing resistor from OSC to PVDD (or other DC voltage) to set the oscillator frequency between 100kHz and 1MHz.

#### 23. PGND1

CH1 Converter On Chip MOSFET Ground.

#### 24. SW1

CH1 Converter Switching Pin. Connect to the inductor of the CH1 converter

#### 25. PVDD1

Power Output of the CH1 DC-to-DC Converter. PVDD1 can also power other converter channels. Connect PVDD1 and VDD together.

#### 26. PGND2

CH2 Converter On Chip MOSFET Ground.

#### 27. SW2

CH2 Converter Switching Pin. Connect to the inductor of the CH2 converter.

#### 28. PVDD2

When SEL2 = PVDD1, the CH2 converter is configured as a step-up and PVDD2 is the CH2 output. When SEL2 = GND, the CH2 is configured as a step-down and PVDD2 is the on chip MOSFET power input.

#### 29. ON5

CH5 Controller On/Off Input. Logic high = on; however, turn-on is locked out until 1024 OSC cycles after the CH1 Converter has reached regulation.

#### 30. CC5

CH5 Controller Compensation Pin. Connect a series resistor-capacitor from this pin to GND to compensate the converter control loop.

#### 31. FB5

CH5 Controller Feedback Input. The feedback threshold is 0V.

#### 32. PVDD5

Voltage Input for CH5 Controller Gate Driver. The voltage at PVDD5 sets the high gate-drive voltage.

#### 33. GND

Analog Ground.

#### 34. DR5

CH5 Controller Gate-Drive Output. DR5 drives between PVDD5 and GND.

#### 35. DR6

CH6 Controller Gate-Drive Output.

#### 36. DR4

CH4 Controller Gate-Drive Output.

#### 37. VDD

Chip Power input.

#### 38. CC6

CH6 Controller Compensation Pin. Connect a series resistor-capacitor from this pin to GND to compensate the converter control loop.

#### 39. FB6L

CH6 Controller Current-Feedback Input. Connect a resistor from FB6L to GND to set LED current in LED boost-drive circuits. The feedback threshold is 0.2V. Connect this pin to GND if using only the FB6H feedback

#### 40. ON6

CH6 Controller On/Off Input. Logic high = on; however, turn-on is locked out until 1024 OSC cycles after the CH1 Converter has reached regulation.

#### **FUNCTION DESCRIPTION:**

The CAT7301/CAT7302 include three DC-to-DC converters and three DC-to-DC controllers to generate all DSC required power voltages:

- CH1 : Step-up DC-to-DC converter with on-chip power MOSFETs.

- CH2: Step-up/Step-down DC-to-DC converter with on-chip power MOSFETs.

This channel can be configured as either a step-up or step-down converter.

- CH3: Step-down DC-to-DC converter with on-chip power MOSFETs.

- CH4 : DC-to-DC controller for boost and flyback converters.

- CH5: DC-to-DC controller for inverting converters in CAT7301.

DC-to-DC controller for boost and flyback converters in CAT7302.

- CH6: DC-to-DC controller for white LED driver with open LED overvoltage protection or conventional boost controller.

#### CH1: Step-up DC-to-DC converter

This channel typically is used to generate a 5V output voltage from 1.5V to 4.5V battery input and self-power the CAT7301/CAT7302. An internal MOSFET and external synchronous rectifier allow the efficiency up to 95%.

## CH2 : Step-up or Step-down DC-to-DC converter

This channel can be configured as a step-up or step down converter by setting the SEL2 pin. An internal MOSFET and external synchronous rectifier allow the efficiency up to 95%. The step-down operation can be direct form a Li-Ion cell if the minimum input voltage exceeds the desired output by approximately 200mv. When generating 3.3V from a Li-Ion cell, boost-buck operation may be needed so a regulated output can be maintained for input voltages above and below 3.3V. In this case, the CH2 may be configured as a step-down (SEL2=GND) and connect its input, PVDD2, to the CH1 output (PVDD1), set to a voltage at or above 4.2V. The output efficiency with this topology is typically up to 90% and better than SEPIC and ZETA structure. Note the CH2 output must not be set higher than CH1 output.

#### CH3: Step-down DC-to-DC converter

This channel is optimized for generating DSP core voltage at high efficiency. It runs from the voltage at PVDD3. This pin can be connected directly to the battery if sufficient headroom exists to avoid dropout. It can be powered from the output of another converter, CH1 or CH2 for example, for boost-buck operation.

# CH4, CH5, CH6 : Auxiliary DC-to-DC controllers

These three channels operate as fixed-frequency voltage-mode PWM controllers. Their operations incorporate external power MOSFETs, so output power and efficiency is determined by external components.

All of AUX PWM controllers have a guaranteed maximum duty cycle of 80% and typically achieve 85%. In boost design that employ continuous inductor current (CCM), the maximum duty cycle limits the boost ratio so:

$1 - Vin / Vout \leq 80 \%$

With discontinuous inductor current (DCM), no such limits exists for the input/output ratio since the inductor has time to fully discharge before the next cycle begins.

The CH4 can be used for conventional DC-to-DC boost and flyback designs. Its output is designed to drive an N-channel power MOSFET.

The CH5 is identical to CH4 in the CAT7302. In the CAT7301, CH5 is an inverting controller and generates a regulated negative output voltage, typically for CCD and LCD bias. This is useful in height-limit designs where transformers may not be desired. The efficiency is more than the charge-pump inverter for the same loading.

The CH5 power MOSFET driver is designed to drive P-channel power MOSFETs in the CAT7301.

The CH6 can be configured as a switch-mode boost current source for white LEDs, FB6L (0.2V) provides current sensing feedback, while FB6H provides (optional) open-LED overvoltage

protection. If used as a conventional voltage-mode boost converter, FB6L is grounded and FB6H (1.25V) is used as the feedback input. In this case CH6 behaves exactly like CH4.

#### Soft-Start

The CAT7301/CAT7302 all channels feature a internal soft-start function that limits inrush current and prevents excessive battery loading at startup by ramping the output voltage of each channel up to the regulation voltage.

This is accomplished by the internal counters to count over a period of 4096 oscillator cycles and ramp the reference voltage of each channel error amplifier from 0V to 1.25V when a channel is enabled.

The CH3 soft-start ramp take half the time (2048 cycles) of the other channel ramps. This allows the CH3 and CH2 outputs to track each other and rise at nearly the same dV/dt rate on the power-up.

#### **Fault Protection**

The CAT7301/CAT7302 have robust fault and overload protection. After power-up, the device is set to detect an out-of-regulation state that could be caused by an overload or short. If any channel remains faulted for 100,000 cycles, then all outputs latched off until the CH1 is reinitialized by the ON1 pin or by cycling the input power.

An exception to the standard fault behavior is if the CH1 output (PVDD1) is dragged below 2.5V UVLO threshold or is short. In this case, all channels are shut-down immediately.

When CH6 (as WLED driver) overvoltage occurs, all channels are latched off and needs CH1 reinitialization or by cycling the input power.

### **Design Procedure:**

#### **Setting the switching frequency**

The switching frequency is set with an external resistor (Rosc) and capacitor (Cosc). At the beginning of a switching cycle, the capacitor charges through the resistor until it reaches Vref (1.25V). The charge time t is:

$$Vref = Vpvdd1 * (1 - exp (-t / (Rosc * Cosc)))$$

Such that,

$$t = -Rosc * Cosc * ln (1 - Vref / Vpvdd1)$$

The device internal delay and the Cosc discharge time is about 250ns (td), so

Note, the parasitic capacitance at the OSC pin need to be calculated into Cosc (typically 15pf).

#### Setting the output voltage

The CAT7301/CAT7302 output voltages are set by resistors as below:

$$Rtop = Rbottom * (Vout / Vref - 1)$$

Rtop: fb pin to output resistor

Rbottom: fb pin to ground resistor

When CH6 works as WLED driver, the current setting resistor is set by:

Rwled = 0.2 / Iled

The FB5 pin of CH5 threshold on the CAT7301 is 0V. The output voltage of CH5 can be set by the formula:

Rtop: fb5 pin to output resistor Rref: fb pin to ref pin resistor

#### **Output filter capacitor selection**

An output capacitor is required to filter the output and supply the load transient current. Higher Capacitor value and lower ESR reduce the output ripple and the load transient drop.

Output ripple with a output capacitor is approximately as follows:

k value is approximately 4 for boost converter and 8 for buck converter

# Step-up converter (CH1, Ch2) inductor selection

In most setp-up degsin in continuous mode (CH1, CH2), a reasonable inductor value can be derived from the following formula:

Lideal =

$$(2 * Vin(max) * D * (1-D)) / (Iout * fosc)$$

D is duty cycle and given by D = 1- Vin / Vout. In this equation, the  $\Delta I_L$  (inductor peak-to-peak current) is 1/2 DC inductor current.

The smaller inductor value is used, the higher the inductor peak-to-peak current and a larger output

capacitance may be required to suppress output voltage ripple.

# Step-up converter (CH1, CH2) compensation

The inductor and output filter capacitor are usually chosen first in consideration of performance, cost, and size. The CH1, CH2 step-up converters operate with continuous inductor current, a right-half-plane zero (RHPZ) appears in the loop-gain frequency response. To ensure stability, the control-loop gain should cross over (drop below unity gain) at a frequency (fC) much less than that of the right-half-plane zero. Typically, fC is approximately below  $1/4 \sim 1/10$  of the minimum value for RHPZ and fosc.

$$f_{RHPZ} = (1-D)^2 * Rload / (2 \Pi * L)$$

The CH1, CH2 step-up converters compensation steps are listed below:

- (1). Choose resonable inductor and output capacitance according to the allowed output voltage ripple and load transient.

- (2). Place fC sufficiently below the RPHZ and fosc

- (3). Calculate Cc.

$$Cc = Gm * Vref * (1-D) / (2 \Pi * fC * Rcs * Iload)$$

Gm (error amp transconductance) = 135uS, Rcs (current sense gain) = 0.3 Vref =1.25V

(4). Calculate Rc.

$$Rc = Cout * Rload / (2 * Cc)$$

(5). Determine Cp if is required.

If fESR (zero occurs by output capacitor ESR) is less than fC, it should be cancelled with a pole set by capacitor CP connected from CC to GND.

$$Cp = Cout * Resr / Rc$$

# Step-down (CH2, CH3) converter inductor selection

A reasonable inductor value for step-down converter can be derived from the following formula:

Lideal =

$$(2 * Vin(max) * D * (1-D)) / (Iout * fosc)$$

D is duty cycle and given by D = 1- Vin / Vout. In this equation, the  $\Delta I_L$  (inductor peak-to-peak current) is 1/2 DC inductor current.

# Step-down converter (CH2, CH3) compensation

The CH2, CH3 step-down converters compensation steps are listed below:

- (1). Choose resonable inductor and output capacitance according to the allowed output voltage ripple and load transient.

- (2). Place fC sufficiently below fosc. Typically, fC is approximately below  $1/4 \sim 1/10$  of fosc.

- (3). Set the compensation RC to zero to cancel the Rload Cout pole.

$$Cc = Gm * Vref / (2 \Pi * fC * Rcs * Iload)$$

$$Rc = Cout * Rload / Cc$$

Gm (error amp transconductance) = 135uS, Rcs (current sense gain) = 0.3 Vref = 1 25V

(4). Determine Cp if is required.

If ZESR (zero occurs by output capacitor ESR) is less than fC, it should be cancelled with a pole set by capacitor CP connected from CC to GND.

$$Cp = Cout * Resr / Rc$$

# Auxiliary step-up controller inductor selection

An asynchronous PWM regulator can operate at continuous current mode (CCM) or discontinuous current mode (DCM). When the inductor current falls to zero on each switching cycle, it works at DCM. Otherwise, it works at CCM.

PWM works at CCM sometimes improve the efficiency by lowering the ratio between peak inductor current and output current. It does this at the expense of a larger inductance value that requires larger size for a given current rating.

The benefit of DCM is more flexible loop compensation, and no maximum duty-cycle restriction on boost ratio.

The boundary between CCM and DCM is decided by inductor value. The following equation lists the step-up PWM critical inductor calculation:

$$Lcrit = (Vin^2 * (Vout - Vin) / (2 * Vout^2 * Iload * fosc)$$

L > Lcrit, the PWM works at CCM, otherwise at DCM.

# Auxiliary step-up controller DCM compensation

The DCM boost compensation lists below:

- (1). Choose resonable inductor works at DCM.

Choose output capacitance according to the allowed output ripple and load transient.

- (2). Place fC sufficiently below fosc. Typically, fC is approximately fosc/10 or lower for voltage-mode boost.

- (3). Set the compensation RC to zero to cancel the single fp pole.

$$fp = (2*Vout - Vin) / (2 \Pi*Rload*Cout*(Vout - Vin))$$

$$Cc = (2* Vout * Vin / (2* Vout - Vin)) * ((Vout-Vin) / (k * Vout))^{1/2} * (Vref * Gm / (2 \Pi * fc * Vout * Vramp))$$

$$k = 2 * L * fosc / Rload$$

Vramp is the internal slope-compensation voltage ramp of 1.25V.

$$Rc = 1 / (fp * Cc)$$

# Auxiliary step-up controller CCM compensation

With CCM boost operation, there is a right-half-plane zero (RPHZ) at the following:

$$f_{RHPZ} = (1 - D)^2 * Rload / (2\pi * L)$$

where

$$(1 - D) = Vin / Vout$$

There is a complex pole pair at the following:

fp =

$$(1 - D)^2 / (2\pi * (L * C)^{1/2})$$

The compensation steps are listed below:

- Choose resonable inductor works at CCM.

Choose output capacitance according to the allowed output ripple and load transient.

- (2). If the zero due to the output capacitance and ESR is less than 1/10 the RHPZ:

$$fesr = 1 / (2\pi * Cout * Resr)$$

Place fC at fesr. The Cc can be calculated by:

$$Cc = (Vin * Vref * Gm / (2\Pi * Vramp * Vout * fesr)$$

Choose Rc to cancel one of the poles pair at fp.

$$Rc = 1 / (fp * Cc)$$

(3). If fesr is not less than  $f_{RHPZ}/10$  (as is typical with ceramic output capacitors), then cross the loop over before  $f_{RHPZ}$  and 10.

$$fC < fosc / 10$$

and  $fC < f_{RHPZ} / 10$

$$Cc = (Vin * Vref * Gm / (2\Pi * Vramp * Vout * fC)$$

$$Rc = Rload * Cout / Cc$$

# Auxiliary inverting controller inductor selection

The boundary between CCM and DCM of inverting controller is listed below:

$$Lcrit = (Vin / (|Vout| + Vin))^2 * Rload / (2 * fosc)$$

L > Lcrit, the PWM works at CCM, otherwise at DCM.

# Auxiliary inverting controller DCM compensation

- (1). Choose resonable inductor works at DCM.

Choose output capacitance according to the allowed output ripple and load transient.

- (2). Place fC sufficiently below fosc. Typically, fC is approximately fosc/10 or lower for voltage-mode boost.

- (3). Set the compensation RC to zero to cancel the single fp pole.

$$fp = 1 / (\Pi * Rload * Cout)$$

Cc =

$$(Vin * Vref / ((|Vout| + Vref) * (k)^{1/2})) * (Gm / (2 \Pi * fc * Vramp))$$

$$k = 2 * L * fosc / Rload$$

$$Rc = 1 / (fp * Cc)$$

# Auxiliary inverting controller CCM compensation

With CCM inverter operation, there is a right-half-plane zero (RPHZ) at the following:

$$f_{RHPZ} = (1 - D)^2 / D * Rload / (2\pi * L)$$

where

$$D = |Vout| / (|Vout| + Vin)$$

There is a complex pole pair at the following:

fp =

$$(1 - D)^2 / (2\pi * (L * C)^{1/2})$$

The compensation lists below:

- (1). Choose resonable inductor works at CCM.

Choose output capacitance according to the allowed output ripple and load transient.

- (2). If the zero due to the output capacitance and ESR is less than 1/10 the RHPZ:

$$fesr = 1 / (2\pi * Cout * Resr)$$

Place fC at fesr. The Cc can be calculated by:

$$Cc = (Vin * Vref * Gm / (2\Pi * Vramp * (|Vout| + Vin) * fesr * (1-D)^2)$$

Choose Rc to cancel one of the poles pair at fp.

$$Rc = 1 / (fp * Cc)$$

(3). If fesr is not less than  $f_{RHPZ}/10$  (as is typical with ceramic output capacitors), then cross the loop over before  $f_{RHPZ}$  and 10.

$$fC < fosc / 10$$

and  $fC < f_{RHPZ} / 10$

$$Cc = (Vin * Vref * Gm / (2\Pi * Vramp * (|Vout| + Vin) * fC * (1-D)^2)$$

#### **Auxiliary diode selection**

For asynchronous applications, a Schottky diode rectifies the output voltage. Schottky low forward voltage and fast recovery time provide the best performance in most applications. Silicon signal diodes are sometimes adequate in low-current (<10mA), high-voltage (>10V) output circuits where the output voltage is large compared to the diode forward voltage.

#### **Auxiliary power MOSFET selection**

On th CAT7302, CH4, CH5, CH6 drivers are designed for N-channel MOSFETs. On the CAT7301, CH5 is a DC-to-DC inverter, so DR5 is designed to drive a P-channel MOSFET.

The MOSFET should be selected base on  $R_{ds(on)}$ , gate supply voltage, gate charge (capacitance) and thermal management requirements.

The MOSFET power dissipation is a combination of on-resistance and switching losses. The following equations can be used to calculate power dissipation in the MOSFETs:

P\_mosfet =

$$Iout^2 * R_{ds(on)} * D + 1/2 * Iout * Vin * fosc * tsw$$

Where.

D is the duty cycle tsw is the switching interval for MOSFET. fosc is the switching frequency.

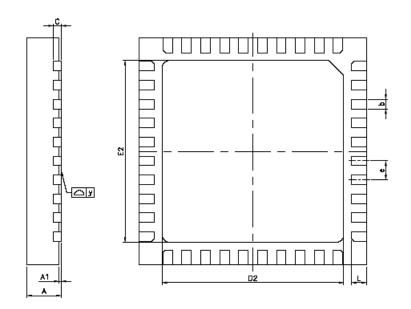

## **Mechanical Dimension**

| SYMBOLS | DIMENSIONS IN MILLIMETERS |           |       |  |

|---------|---------------------------|-----------|-------|--|

| SIMDULS | MIN                       | NOM       | MAX   |  |

| Α       | 0.80                      | 0.90      | 1.00  |  |

| A1      | 0.00                      | 0.02      | 0.05  |  |

| b       | 0.18                      | 0.25      | 0.30  |  |

| С       |                           | 0.20 REF. |       |  |

| D       | 5.90                      | 6.00      | 6.10  |  |

| D2      | 4.65                      | 4.80      | 4.95  |  |

| E       | 5.90                      | 6.00      | 6.10  |  |

| E2      | 4.65                      | 4.80      | 4.95  |  |

| е       |                           | 0.50      |       |  |

| L       | 0.35                      | 0.40      | 0.45  |  |

| у       | 0.00                      |           | 0.076 |  |

|         |                           |           |       |  |

#### CONTACT:

**HEADQUARTERS**:

8F, No.1, Jin-Shan 7<sup>th</sup> St., Hsin-Chu,

300 Taiwan, ROC. Tel: +886-3-666-8301 Fax: +886-3-666-8630

Website: http://www.chipadvanced.com

Information furnished is believed to be accurate and reliable. However, CAT Inc. assumes no responsibility for the consequences for use of such information or for any infringement of patens or other rights of third parties which may result from its use. No license is grated by implication or otherwise under any patent or patent rights of CAT Inc. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information if previously supplied. CAT Inc. products are not authorized for use as critical components in life support devices or systems without the express written approval of CAT Inc.

The CAT logo is a registered trademark of Chip Advanced Technology 2004 Chip Advanced Technology Inc. – All Right Reserved.