Shanghai Hometown Microsystems Inc

System Design Frontier

Monthly Online Technical Journal

Volume 1, Number 5, July 2004

Enabling of Your Local Globalization and Global Localization

# Content

| Editorial: Never Too Late Editor In Chief                                    |    |

|------------------------------------------------------------------------------|----|

| Loosely Does It Stephen Barrett                                              | 1  |

| Design for Manufacturibity - The Impact on the Physical Design Stage and Flo | w  |

| Danny Rittman                                                                | 3  |

| Fundamentals of Web Site Acceleration Performance Starts at the Web Server   |    |

| Port80 Software                                                              | 24 |

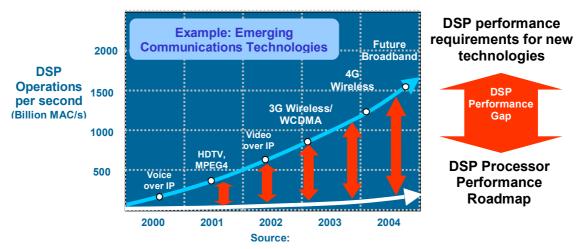

| Top-Down DSP Design Flow to Silicon Implementation                           |    |

| AccelChip, Inc                                                               | ;3 |

| Upcoming Advanced & Educational Trainings 4                                  | 1  |

| Industrial Job Openings                                                      | 59 |

**Copyrights** Copyright © 2004, Shanghai Hometown Microsystems Inc ("Publisher"). All rights reserved. No part of System Design Frontier ("Publication") may be reproduced, transmitted, or translated, in any form or by any means, electronics, mechanical, manual, optical, or otherwise, without prior written permission of Publisher.

Disclaimer Publisher Makes No Warranty Or Any Kind, Express Or Implied, With Regard To This Publication

## 64<sup>th</sup> China Electronics Fair (CEF Shanghai 2004) 2004年(第64届)全国电子产品展览会

# Venue: Shanghai New International Expo Center, China Date: Nov.15-18, 2004

**C**EF is a most authoritative, comprehensive and professional electronics fair in China, which is an electronic fair supported fully by China Ministry of Information Industry and Ministry of Commerce. CEF is also the fair with a long history, large scale, and deep influence of its kind in China. CEF Shanghai 2004 will reach 46,000 sqm in exhibition area. Now for FREE visitor ticket: www.chinaelec.com.cn

Together with 2004 Asia Electronics Exhibition in Shanghai (AEES 2004) www.aeesshow.com

Hall 1: AEES 2004 (For consumer elctronics), Digital household electronic device Hall 2: CEMAS 2004(For electronic facilities), Automobile electronics, Power & Supply

- Hall 6: Testing and measurement instrument, Optical products, Sensors

- Hall 7: Comprehensive electronic components, Military electronics

#### Sponsor:

China Electronic Appliance Corporation (CEAC)

#### Organizer:

China Electronic Exhibition & Information communication Co., Ltd (CEEIC)

#### Contact:

49, Fuxing Rd., Beijing, 100036, China Tel: +86-10-68207732/33/34 ext. 16/22 Fax: +86-10-68132578/68189519 E-mail: nef@ceac.com.cn www.chinaelec.com.cn

# **中电会展** 电子信息业会展专家

### Suite: 22217-22219, Pudong SW Park, Shanghai China Copyright <sup>©</sup> 2004 Shanghai Hometown Microsystems Inc.

#### Co-organizers:

Provincial branches of CEAC Hong Kong Trade Development Council (HKTDC) Taiwan Electrical And Electronic Manufacturers' Association (TEEMA) International PR, Inc. Korea American Business Exhibition Co., Ltd

| Reply Form (Fax to: 01    | 0-68132578):              |       |  |

|---------------------------|---------------------------|-------|--|

| I am interested in        | exhibit,                  | visit |  |

| CEF Shanghai 2004, please | sent me more information. |       |  |

| Name:                     | Company name:             |       |  |

| Position:                 | URL:                      |       |  |

| Addr:                     | email:                    |       |  |

| Tel:                      | Fax:                      |       |  |

| Main product:             |                           |       |  |

| 上规模上档次<br>展风采 | 国家规划布局内的重点软件企业<br>软件最大规模前100家企业 | 精英灿烂!<br>强劲登场! |

|---------------|---------------------------------|----------------|

| "中国           | 国软件 20 年"评选活动                   |                |

| INT'I         | SOFT CHIN                       | A 2004         |

## **1NI**<sup>2</sup>L SOFI CHINA 2004 2004 第八届中国国际软件博览会

主题: 中国软件产业国际化与企业做强做大

开幕式/主论坛/分论坛 2004年7月8日-7月10日 北京,中国国际展览中心1号馆、综合楼

支持单位:中华人民共和国国家发展与改革委员 会

中华人民共和国科学技术部 华人民共和国商务部 华人民共和国国务院信息化办公室 各省市、自治区信息产业主管部门 主办单位:中华人民共和国信息产业部 承办单位:中国软件行业协会 中国计算机报社

中国国际贸易中心 全网站。赛迪网(www.soidnot

大会网站:赛迪网(www.ccidnet.com)

### 欢迎各界报名参选、参会、参展!

评选报名热线: 010-88559723/9995

论坛联系方法:

联系人: 邱燕娜 郝杰

电话/传真: 010-88559723/9995/9809/9867,

88559887 (F)

地址: 北京海淀区紫竹院路 66 号赛迪大厦 18 层中

国计算机报(邮编: 100044)

电子邮箱: <u>qiuyanna@ciw.com.cn</u> grace@ciw.com.cn

参展联系方法: 联系人:朱芸 顾长江 李璐 电话/传真:010-62186579(F),62143871(F), 51527167,51527159 地址:北京海淀区学院南路 55 号中软大厦 A401 室(邮编:100081) 网站:<u>www.csia.org.cn</u><u>www.ccidnet.com</u>(欢迎 网上注册参展参观!) 电子邮箱:<u>csia@css.com.cn</u> **论坛内容** 第一部分:开幕式

第二部分:颁奖仪式 奖项设置: 中国软件 20 年明星企业—— 机授予在软件领域辛苦 耕耘了近二十年,在产业的发展过程中不断成长壮大, 起到了典范作用的软件企业

中国软件20年特别成就奖——拟授予在软件产业的 发展过程中付出了巨大心血,并在软件领域取得突出成 就的软件专家、学者及知名人士

中国软件 20 年杰出贡献奖——拟授予为推动软件产 业的发展做出长期贡献并取得骄人成绩的软件企业家

中国软件 20 年最具应用价值的优秀软件产品——拟 授予在长达近二十年的应用中经得住用户考验、发挥了 巨大应用价值的软件产品

评选流程:

第一阶段:通过各地信息产业主管部门、各地软件行 业协会推荐候选者,或由候选者主动报名,专家推荐

第二阶段:邀请软件领域知名专家、软件行业协会资 深人士、IT媒体资深人士及产业相关领导等组成评委会 进行审议

第三阶段:采用群众投票初评,评委会复评最后确定 获奖者

第四阶段:于软博会开幕式进行颁奖

第三部分: 主论坛 主题: 软件政策与产业发展论坛(18号文件与WTO、行 政许可证与18号文件、政府采购) 资本与软件企业成长性论坛 软件国际化与服务外包论坛 软件学院与人才培养论坛 技术进步与 IT 应用论坛 版权保护与国际形象论坛 开放源码论坛 高峰对话:中国软件二十年 对话嘉宾:"中国软件20年杰出贡献奖"及"中国 软件20年特别成就奖"获得者代表 第四部分 嵌入式专场 主题: 嵌入式产业新机遇(汽车电子、消费电子、移 动增值、工业控制、医疗电子、机床电子、银行终端 等) Ξ, 中间件专场 主题:软件产业的发展后动力 三、 游戏专场 主题: 做大做强国产游戏 四、 软件与传统产业专场 主题:从传统产业中诞生的软件企业 第五部分: "中国软件二十年"纪念展(软件墙) 在主论坛展示区内,以"产业篇章"的形式,总结中 国软件产业二十年来的发展:产业篇、人物篇、成果篇

### Never Too Late

Editor In Chief

I had my DAC trip at San Diego in early June, it shocked me in someway: due to the industry wide of cost reduction, I saw fewer attendees this year despite the fact that the industry definitely seems to be turning up, on the other hand, lots of startups showed up for the first time there demonstrating their key technologies. In late June, we set up a booth at ELECOM 2004, a leading trade show for telecommunication industry in China. I experienced the similar phenomena as I saw at DAC, one big difference between ELECOM is that, even though there are lots of startups in China, not too many startups showed up at the trade show, and multi-nationals along with local heavy-weights dominate the seen, and it makes startups hard to breathe. I was impressed by local heavyweights, on their deep pockets as well as their technology advance.

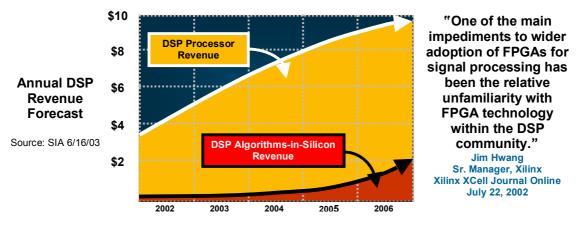

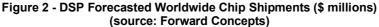

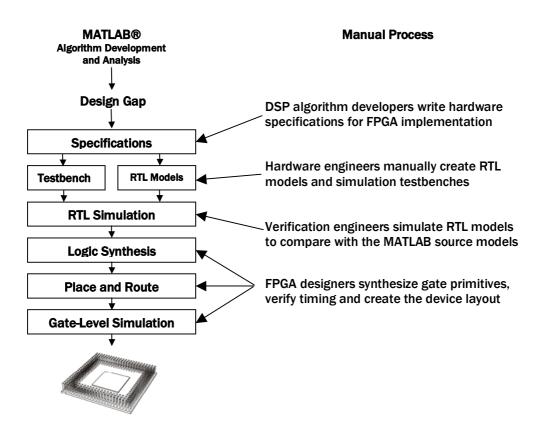

Honestly I am quite optimistic on the road ahead. Why? Both in HW engineering and SW engineering, there are so many existing problems yet to be solved or to be proved as unsolvable, and more and more new problems are emerging as well. For example, the Design for Manufacuribity problem is new, and is different as Yield Optimization problem a decade ago, and here Danny Rittman has a good paper in this issue; the system-level synthesis problem, proposed around the mid-90s, has no perfect solution so far, even with quite a few system-level specification languages being proposed, ranging from C to C++, Java, MatLab, SystemC, and most recently SystemVerilog, here AccelChip Inc contributes an interesting paper on how to automate the DSP design flow from MatLab to synthesized gate-level netlist along with generated testbenches. I strongly believe that the syntax of a specification really does not matter that much, as far as it is rich yet concise enough for system-level modeling (specification and verification), the thing matters is the semantics of the specification language from the synthesis point of view- It is not how you draw it, it is how we view it that really makes sense. Now if pure top-down approach never works for any practical design space, will the IP-based SoC design approach be the winner? No way, as the high NRE cost associated with SoC, nor is reconfigurable computing, and that leads to the rising of Structured ASIC

On SW development side, similar to HW, the one we care about is performance, and the other we care about is cost. When the computing paradigm migrates from client/server based to distributed based, the browser/server architecture now evolves to multi-tier architecture, and whether it is .Net based web services, or J2EE based web services (or even just IIS based web server versus Apache based web server), performance is always of paramount importance, and Port80 SW addresses this topic quite well in this issue. On the cost side, since the OO technology cannot deliver what it promised, pattern and component based technology takes over in attacking the yet to be solved SW design reuse problem, similar to HW design reuse, separating interface (communication or service) from implementation (action or computation) is the key for sure. In this issue, Stephen Barrette presents a novel way on component-based reuse under such scenario

So Never Too Late, and see you at INT'L SOFT CHINA 2004

## Loosely Does It

### Stephen Barrett

### Chief Architect, Wilde Technologies stephen.barrett@wildetechnologies.com

### Abstract

Software constructed using traditional development paradigms suffers from an

inherent inflexibility. This is due to both the tight coupling of the components of the system, and to the difference between the system's actual implementation and the architect's view of it. A loose coupling paradigm can overcome these problems, and deliver flexible enterprise software, but the architect must develop and deploy mechanisms that provide loose coupling if he or she wishes to architect for change. This is an expensive and risky under taking. Wilde reduces both risk and cost by supporting a loose coupling paradigm that is driven directly from application architectural modeling. It is built on and supports component technologies deployed today. It delivers more rapidly constructed, better defined and more easily maintained software than any technology currently available.

### 1. Introduction

A view of components has emerged that posits the component as a service provider, packaged using a component technology, and often available across the network. The service oriented architectures that we see emerging through standards such as WSDL, UDDI, and SOAP pay homage to this kind of model: the component as a service provider within a larger application. The enterprise has used this kind of client/server model as the backbone of enterprise systems for years. Over time, it has become clear that enterprise software is inflexible and very expensive to maintain, with some 70% of development effort going into the maintenance of these systems, once deployed. Leaders in the area of component-based development have identified a shortcoming in the modeling of the enterprise software system that substantially contributes to the problem.

They have proposed a solution based on a richer component model, built not around simple service provision, but rather around a more symmetric model that includes service requirements within the specification of a component [2]. I t is argued that this model better represents components in medium and larger scale software systems, as co-operating computational entities (i.e. n-tier), and not simply layers of dependent functionality. From an architectural point of view, symmetric component modeling adds clarity to the modeling of the enterprise. This makes maintenance easier to define and control, but the key benefit of a symmetric component model is its support for a component paradigm based on loosely coupled components. Coupling in software is the idea that one piece of software has dependencies on other software. This categorization includes dependencies such as a dependency on the host operating system (your

spreadsheet won't run on Linux), a dependency on simultaneous execution (as in client/server systems), and a dependency on shared data source (as with multiple applications accessing a common data base). In the context of component-based software, we focus hereon dependencies on other services, their location, and interfaces.

We thus define a loosely coupled component as one that can be bound late in the development cycle to partners that provide it with services. This means that the identity of service partners can be configured after the component has been deployed, and possibly while the component is executing. Software systems constructed as compositions of loosely coupled components are in theory more flexible, and less expensive to maintain.

In practice, flexibility costs - it takes substantial effort and skills to implement loosely coupled components, and assemble them into applications. Looser coupling requires a greater up-front investment in design and implementation. You must make use of mechanisms such as connection points, directory services, or event services. This almost certainly means utilizing and building skills in one or more component technologies.

Once this has been achieved, it is then necessary to build and maintain an architectural code base that assembles and configures the components to form a system. This requires a development team that has a high degree of skill in component technologies, and a strong, buy-in<sup>TM</sup> regarding the benefits of loose coupling and component based development by the architects and other stakeholders. Few architects doubt that loose coupling is a desirable goal in a software design, but the pragmatic recognize it as an expensive investment to be used only when its need can be predicted. The challenge then is to provide a paradigm that cost-effectively supports the implementation of loose coupling. Wilde is an architecture implementation platform that provides this kind of support. Before describing how Wilde works, and what the benefits of Wilde are, We want to look at why loose coupling is indeed a necessary paradigm for solving the flexibility problems in the enterprise

### 2. Loose Coupling: A Necessary Paradigm

At its most simple, loose coupling is about reducing the dependencies between pieces of code. In the context of component based software, we focus here on dependencies on other services, their location, and interfaces, and define a loosely coupled component as one that can be bound late in the development cycle to partners that provide it with services. This means that the identity of service partners can be configured after the component has been deployed, and possibly while the component is executing. Software systems constructed as compositions of loosely coupled components are in theory more flexible, and less expensive to maintain. To understand why this is so, it is necessary to study the limitations of a traditional development approach, and what occurs as components are connected together to form the software system. Typically what results is an interconnected component set that is very hard to break apart. We examine this later in The Drawbacks of Coupling in the context of a simple example software system. Following that in Loosely Coupled Components, we apply the loose coupling paradigm to the same system where we see that loose coupling preserves flexibility in a systems

2

implementation. This allows us to make architectural changes without the traditional expense

### 2.1 The Drawbacks of Coupling

All code in a software system fulfils one of two functions. Some code implements business logic algorithms, stores data, creates and responds to the button press and so forth. We call this behavioral code in that it provides some desirable execution behavior. The ecotype of code assembles the behavioral code, binding it together ensuring that it cooperates to achieve the desired overall system goals. We call this architectural code because it implements the application architecture. It typically amounts to some 30% of the overall code basin generally takes the form of constructor parameters, directory lookups, object creation in mainlines and in class methods, distributed invocation framework, and so on. This kind of activity seems so second nature to the typical developer that it seems odd to award it equal status with real functionality. However, it t is precisely this architectural code, and its structure, that has the principal impact on system flexibility. I f you don't believe this then we suggest you peruse redesign Patterns, by Eric Gamma et al. [2] paying particular attention to io behavioral patterns such as the Mediator, and structural patterns such as isBridgelland in Compositell- it<sup>TM</sup>s not what you do; it T<sup>M</sup>s the way that you do it!

A loose coupling paradigm implies that a system it s constructed from two separate and distinct code bases: one that implements the components, and one that assembles the components together. In other words, Behavioral code and architectural code are separated. This is quite different from traditional development approaches in which a single code base is implemented that combine architectural and behavioral code in the same computational units. The traditional development process makes no distinction between architectural and behavioral code. The system model, that describes necessary behavior and the structure of the system, is used to produce a single code base. This approach to system construction results in software that is overly complex and difficult to change, hard to understand, and thus expensive to change.

The lesson to be learned from this is that architecture should, if possible, be implemented separately from behavioral code. This means avoiding the embedding of architectural code in behavioral components. This may seem like a small point, but is in fact a major issue as you scale up from the class library or application to the enterprise. At the application level, you can make decisions like we will use Javelin, or acrobat is our distributed bus choice, it but not across the complete enterprise. At that level, aspects of a software system that inhibit flexible and cost effective reconfiguration have a disproportionate impact on the cost of maintenance.

In the following subsections, we look at why the construction of code that implements a system's application architecture is more difficult than is commonly assumed, and why in the absence of a clearly defined loose coupling paradigm, this typically results in the embedding of architectural code in behavioral code. We explain why this results in expensive maintenance and why the architect's view of the software system diverges

From the real code base so that it becomes increasingly difficult to change the system to accommodate new requirements.

2.1.1 Embedding Architecture Makes it Difficult to Change Implementing architecture is a complex business. Even if you work only with classes, the complexity inherent in the creation and maintenance of the relationship between client and object is often overlooked.

To illustrate this, let's explore how we might build the gateway component using C#: a language that lets us takes a class like view of component technology. We will assume that the method do Trade is supposed to do some internal computation before delegating the trade to the external trade service.

```

Public bolo do Trade(string arg_account, Trade Details arg_trade)

{

if(doTradeOK(arg_account))

{

return m_trade Service. doTrade(arg_account, arg_trade);

}

else

return false;

}

Figure 1: A simple inter face method

```

The first issue is how the gateway obtains a reference to the trade service - how do we create the relationship? There are many mechanisms and pat terms for doing this.

Figure 3 illustrates a constructor based approach that is typically used. The constructor includes a reference to a trade service object as a parameter.

```

void Gateway(ITradeService arg_tradeService)

{

m_tradeService = arg_tradeService;

}

Figure 2: A non-default constructor for the Gateway.

```

Let's be clear. This constructor is architectural code. It is about connecting behavior together. This const rector is one of the many ways to do that. This approach would have to be modified if we chose to implement the gateway as a COM component, because there can be no default constructor in a COM component. In such cases presumably we would provide an alternative **Init** method or property (note to architect: please remember to modify the UML model to take account of COM technology requirements).

Note that if we go with this kind of constructor based solution, or initialization method solution, and then the client is required to be aware of the identity of the trade service so that it can initialize the Gateway instance (see Figure 3). This may be acceptable (if you don't mind your clients configuring your services) in certain circumstances, but it would be an unacceptable solution in a real client/server scenario. In such a case, the Gateway will already be executing, before the client connects.

Class MyClient { Itrade Service m\_trade service = //get the trade service please IAction m\_gateway = // get the gateway please MyClient() { m\_gateway.Init(m\_tradeservice); } Figure 3: A trade service aware client

To solve this, we could engineer a third component (e.g. a server mainline) that manages the creation of the trade service and Gateway component instances and we would configure the Gateway component instance so that it holds a reference to the trade service instance.

This is not a bad idea, but because it constitutes additional implementation effort, it is more likely that in practice, the Gateway will be implemented to either directly create the trade service, or obtain a reference to it via some directory lookups mechanism, either a standardized mechanism such as UDDI, or some is spoke internal service. So, our code might look like Figure 4

```

public Gateway : IGateway

{

ITradeService m_tradeService = null;

Gateway()

{

m_tradeService = new (ITradeService) TradeService();

}

public bool doTrade(string arg_account, TradeDetails arg_trade)

{

if(m_tradeService == null)

throw new ExternalServiceError("where's my trade service?");

if(doTradeOK(arg_account))

{

return m_tradeService.doTrade(arg_account, arg_trade);

}

else

return false;

}

Figure 4: A non-parameterized gateway

```

Let's be clear here too that this is architectural code, buried within the behavior. As Figure 4 demonstrates, application code is typically writ ten so that it combines both behavioral code and architectural code. This is bad for flexibility because it is as expensive to change architecture, as it is hard to identify the scope and location of necessary change. It goes without saying that; anything that requires recoding does not bode well for flexibility in any case.

If we have a constructor-based solution such as described in Figure 2, then it might look like we can apply this architectural change without modification of the Gateway component. However this is only part of the story. If the new component is implemented using a new technology, such as Web services, then some development effort is incurred in order to pass the gateway a simple reference. Where should this code go? Who is responsible? It depends on how the developers implemented the architect's application architecture. Our model has no well-defined mapping to the distributed component code base.

If we had opted for a gateway implementation as described in Figure 4, then a degree of recoding of the Gateway itself would be necessary. Because we do not have an external code framework for the assembly of what is now a three component system, the following code segment (Figure 6) is quite likely to be embedded in the Gateway. Actually, something far more complex is likely to be needed, but there is no need to overcomplicate for this discussion. Note how application architectural code is becoming spread through behavioral code -why does the Gateway have a constructor that configures external components? If this particular three component system becomes obsolete in a couple of months, where do we look to change the architecture? Deep in the implementation of the components? If at some point, we wish to replace our Gateway component with a new implementation, this kind of architectural code will have to be replicated somewhere -- where should it go?

Gateway() { // create the trade service, and filter component ITradeService m\_ts = lookup("trade service"); IAction m\_fltr = lookup("filter"); // configure so chain is this-> filter -> trade service m\_action = m\_fltr; IConfigure cnf = (IConfigure) m\_fltr; cnf.InitTradeService(m\_ts); } Figure 6: Configuring the component set

We're not done yet. The new filter component must be configured to delegate trades to the trade service. We have to consider how it obtains references to external services. For example, it might look up such services using UDDI. The implementer of the filter component may have specified this so that it exhibits greater deployment flexibility, and so is easier to reuse in different systems. If so, then it will be necessary now to expose the trade service as a Web service, and possibly prepare a configuration file or write some code to initialize the new filter component so that an instance will perform the correct lookup. What happens if we wish to run two system types in parallel - for example, the original system, which does not perform account credit checking for internal traders, and the new version, which does? Do we have to up grade the gateway so that it accesses this Web service-based trade service implementation in systems that do not contain a filter component? Are there other components that access the trade service directly? Are different versions of components such as the Gate way component now needed?

These are the type of questions faced, with an increasingly disjointed view of the system architecture as the system develops. So far, we have considered an extremely simple system consisting of just three components, linked together in a pipeline. Scale this up, and consider perhaps three hundred components, ten legacy systems, two distributed bus architectures, Visual Basic on the desktop, COM, and Web services and so on. System assembly is less trivial than we would like.

Another argument is that the complexity isn't that hard to handle if done properly. Gamma et al. [2] have described design patterns such as the Mediator, Adaptors, Composites, and Abstract Factories and so on, which they propose can be used to handle this kind of complexity. Perhaps we are describing a worse case scenario. For example, mediators can instantiate and configure component sets, assembling them into coherent subsystems. Provided component references can be configured by this mediation code base, the complexity is manageable, and the kind of flexibility we are looking for is achievable. If you buy this, then you've just bought into loose coupling - you've advocated a separation of behavior and architecture. The degree to which you are willing to enforce the separation impacts directly on the flexibility of your software system going forward.

#### 2.1.2 Embedding Architecture

Leads to A Design Disconnect as argued in the previous section, embedding architectural code in behavioral code makes it difficult to change a system in response to new requirements.

The issue here is whether the architect can be certain that the implemented system accurately reflects the specified model. The key issue is certainty. The actual state of the system is not nearly as important as the accuracy of data available to the architect. Unfortunately, what tends to occur, even when architecture is implemented in code separately from behavior, is that small mistakes lead to a disconnection between what was specified and what was implemented. This is exacerbated by the difficulty in extracting a sensible view of the architecture from the implementation, as the architectural code is literally dispersed throughout the behavioral code. We call this the 'Design Disconnect'.

There is more to consider. What if we have used directory look up technology to obtain a reference to the Trade service rather than a class instance creation? Would we have a more tractable code base then? I t would depend on the nature of the lookup technology in use. If we were using a standard technology like UDDI, which is probably giving us access to a Web service, which would in effect be a Singleton, we would probably be OK. Of course if the lookup technology were be spoke, internal to the enterprise, we would have to check the documentation.

So far we've briefly examined some pitfalls in constructing architectural code. It's possible for developers to make subtle mistakes in the interpretation of the UML modeling that have architectural impact. Worse still, a fairly detailed understanding of

the technologies in use in the software system is necessary in order to correctly interpret what architectural modeling is implemented by specific architectural code. So once the architect hands over the architecture, how does he ensure his modeling remains relevant and more importantly, accurate?

Because these diagrams give very little detail, we have to look at the code (and project context) of the components in order to understand what application architecture has actually been implemented. Worse look for this information.

The design disconnect has the most damaging impact at the point where the system must undergo change. As we add more and more interdependent components into the mix of our enterprise system, what results is an increasingly rigid and hard to maintain enterprise. What is often forgotten is that enterprise systems and intra-enterprise systems are inherently n-tier. The key point is that as these complex systems diverge from the original architectural viewpoint, it becomes increasingly difficult to understand and plan for change. This implies additional costs and risk.

#### 2.2 Loosely Coupled Components

A loosely coupled component is one that can be bound to its partners late in the development life cycle. The key benefit of loose coupling paradigms is that they break the hard relationship between client and server, so allowing partners to be specified orthogonal to the implemented components set. Architectural decisions can be made late in the development cycle, even revisited inexpensively at deployment. This provides a very important kind of flexibility in the context of a component-based system.

Consider the following code segment from the Gateway component of the trading system tutorial that comes with Wilde 1.0 (Figure 7). Some detail has been omitted for clarity. It is a COM component, but one implemented to be loosely coupled. I t implements an interface, as we would expect of all components. It also implements a connection point. The connection point is a mechanism for a COM component to express a requirement for a service provider, that service being defined in terms of a specific interface type.

class CGateway : public CComObjectRootEx<CComSingleThreadModel>, public CComCoClass<CGateway, &CLSID\_CGateway>, public IConnectionPointContainerImpl<CGateway>, public IAction, public CProxyIAction< CGateway> { public: CCGateway() { } BEGIN\_COM\_MAP(CGateway) COM\_INTERFACE\_ENTRY(IConnectionPointContainer) COM\_INTERFACE\_ENTRY\_IMPL(IConnectionPointContainer) COM\_INTERFACE\_ENTRY(IAction) END\_COM\_MAP()

BEGIN\_CONNECTION\_POINT\_MAP(CGateway) CONNECTION\_POINT\_ENTRY(IID\_IAction) END\_CONNECTION\_POINT\_MAP() public: // IAction implementation omitted for clarity }; Figure 7: COM implementation of Gateway Component

The powerful thing about this type of component modeling and implementation is that because the service requirements of a component components are decoupled from their partners, and can thus be flexibly combined without expensive recoding and recompilation of the components. Note its symmetric nature it provides and requires interfaces. We've included the trade service component type, to illustrate how these components are related. We've also included one of the trade services interface requirements to hint at the complexity of a typical component. The tree view to the left of the main diagram contains a more detailed description of the trade service, or lookup the trade service. This is loose coupling. I t means that provided we have the appropriate underlying assembly support in place, we can bind this Gateway component to a component that implements the trade service. This might look like polymorphism, but it's far, far more powerful. It is a formalization of the decoupling of client and server at the component typing level, and it is this that leads directly to far more flexible software systems.

I four components are implemented according to a loose coupling type modelAll that must be changed is the implementation of the application architecture. That might be implemented as a set of mediator classes, some kind of script, or constructed using some other mechanism. So, in theory, any architectural change can be achieved without affecting the behavioral components. In theory this is extremely cheap. In theory what results is agile IT capable of speedy response to changing business requirements. In practice, as mentioned before, implementing this kind of loose coupling paradigm is expensive, requiring expert knowledge of a variety of infrastructure mechanisms. In the next sect ion, we describe Wilde, a platform that supports this paradigm directly

### 3. Wilde

Wilde is a first of breed Architecture Implementation Platform that delivers a highly flexible cost effective platform for distributed component based development. Wilde enables a uniquely structured software system that is rapidly assembled and easily and cost effectively maintained. The product has been built from the ground up to support a Component oriented development process that takes as its starting point the following key ideas.

1) Software systems are constructed by defining and composing components that provide distinct functionality, and that are deployed across a network. These compositions are inherently n-t ire.

2) The composition must be open, meaning components can be added, changed, removed, deployed on different application servers etc.

3) A range of component technologies are used in the physical component Implementations.

4) Change is the norm; system maintenance post-deployment is the principle development activity. Greenfield construction is rare.

5) Managing change requires a full and correct understanding of a system's application architecture from which to drive change.

6) There is no such thing as an application. Every software system is potential l y a component in a larger system.

Wilde supports this feature set as a platform that supports the structuring of software as UML architect compositions of loosely coupled components. This results in a far more flexible software system than can otherwise be achieved, with substantial cost benefits both during development, but most importantly, in the maintenance phase, where most effort is expended.

### 3.1 Wilde Platform

Wilde is delivered as a platform with a design time UML tool for the specification of application architectures of distributed component based systems, and a runtime component that executes these specifications at runtime. Like all component-based technologies, a Wilde system is deployed and executed by combining components. The key differentiator with the Wilde platform is that it uses UML based application architecture model directly as part of the executing software system

A Wilde system is launched by passing the UML model that describes it to the Wilde runtime. This runtime interrogates the model, identifies the components and the nodes in the network on which the system is to execute, and then launches the components and configures them so that they are bound together, as described in the UML model. What results is a set of components executing on the various nodes described in the model. These components might be backend components responsible for business functions, front-end applications presenting a GUI to users, or any other type of components. Wilde supports COM, .Net and Web Services based components. Components used in Wilde need not be implemented specifically to be used with Wilde, which implies that the full existing component asset base of an organization is available for use immediately in Wilde systems, without modification.

### 3.2 The Benefits of Wilde

Wilde has an immediate benefit in the development process but a more important return on investment after a system is deployed. Up front, because Wilde manages the distributed execution of component-based systems, building the required system infrastructure literally at runtime, the development of components is radically simplified. Wilde eliminates the need to encode an application architecture that describes a systems composition in terms of the component set and how those components interact. This eliminates the kind of problems discussed in this article from the development process, speeding up the development process.

This key ongoing benefit of Wilde is the ennoblement of a development process and deployed system that is fundamental l y more flexible and open once deployed. The

architect is in a greatly improved position in dealing with new business requirements. The actual system architecture is visible and directly malleable. This degree of control, which is not delivered by any other technology, allows the architect to both estimates The cost of change with greatly increased accuracy, and control its delivery with greater clarity. Wilde delivers a flexible IT function. This is explored further in Section 3.3.

### 3.3 Wilde -- The Loose Coupling Platform

As mentioned above, one of the key inhibitors to adopting loose coupling is the cost and complexity of application architectural code that performs component based assembly. To make system assembly easier, the Wilde platform provides a GUI for the modeling of component based application architectures, as UML models. The Wilde platform uses this model directly, dispensing with the need for an application architecture code base that manually brings components together. What You Design is What You Get (WYDIWYGŽ)? This approach means that system assembly is a more rapid process upfront.

However this is only half the story. The more important attribute of a Wilde system is that the architect can make changes to the application architecture model that have a direct effect on the software system, without requiring modification of an architectural code base. This is because with Wilde, application architecture is not committed to code at all, but instead is retained in its original UML form. Modifying the model is modifying the system implementation. The Wilde platform assembles software systems directly from this modeling. There is a one to one mapping between the code necessary to assemble loosely coupled components into a software system, and the model of the application architecture of that system. Implementing an architectural code base to instantiate and configure a component based software system is unnecessary and risky, when compared to a platform approach that automates that task. I t is faster and safer than rolling your own.

System assembly is one side of the loose coupling problem. The other is the technical skill set needed to build loosely coupled components. To make component development easier, Wilde provides a component skeleton assembly technology, which delivers compiled. NET assemblies that can be used as the basis for loosely coupled .NET components. Skeleton assemblies contain a simple set of classes that provide an Object oriented view of the required component's symmetric component type. This isolates the developer from the component technologies, and deployment decisions enforced in the application architecture of the specific software system, and indeed the application architecture itself. I t is actually easier to build a loosely coupled component with Wilde than to build a traditionally coupled component, or a loosely coupled component with Gateway component in C# using a skeleton generated from the Gateway type. Note how access to external services is object based, and independent of the implementation of those services.

But most importantly for the architect, it ensures that the components specified are the components delivered, without any unknown dependencies that have to be hunted down. Simplicity is the promise.

Architects define architectures and component types; developers implement components. So, if we briefly consider the filter component scenario discussed above we see that with Wilde, the modified application architecture is used directly in the executing system. Providing that a suitable (i.e. loosely coupled) component implementation of the filter component is available, there is nothing left to do. If we don't yet have a filter component, the architect or developer can generate a skeleton for it, so driving the correct implementation of the component.

We have not considered deployment so far. With Wilde, the application architecture model can specify deployment of components in addition to component relationships. If we executed this system with Wilde, the Wilde runtime would create the necessary distributed infrastructure without programmer intervention. There is no need for programmer intervention, and no requirement for the component development teams to possess distributed systems skill sets. With Wilde, you just model it.

### 4. Summary

Software constructed using traditional development paradigms suffers from an inherent inflexibility, that is due both t o the tight coupling of the components of the system, and to the design disconnect that opens up between the system's actual implementation, and the architect's view of it. Loose coupling is a vital and powerful paradigm for the delivery of flexible enterprise software. It succeeds both by breaking the coupling between components, and by separating out application architectural implementation so that it is less difficult to maintain. However, to implement loose coupling, you need a component model that is symmetrical; that describes components as service providers but also as consumers of services. The component technologies that bind the enterprise together lack inherent support for this kind of symmetrical type model, and thus it is up to the architect to develop and deploy mechanisms that provide loose coupling if he or she wishes to architect for change. This is an expensive and risky under taking.

Wilde reduces this risk and cost by supporting a loose coupling paradigm that is driven directly from application architectural modeling. I t is built on and supports component technologies deployed today. It delivers more rapidly constructed, better defined and more easily maintained software than any technology currently available. It's available now for you to try.

## Design for Manufacturibity The impact on the Physical Design Stage and flow

# Dr. Danny Rittman danny@tayden.com

### Abstract

In this paper I present the impact of sub-wavelength optical lithography for new EDA tools, IC Layout Design flows and manufacturability. We discuss the necessity of corrections for optical process effects (optical proximity correction (OPC) and phase-shifting masks (PSM)) and will focus on the implications of OPC and PSM for layout design and verification methodologies. Our discussion addresses the necessary changes in the design-to-manufacturing flow, including infrastructure development in the mask and process communities as well as opportunities for research and development in IC physical layout and verification stage.

Reticle enhancement technologies (RET) like optical proximity correction (OPC) and phase shift masking (PSM) have significantly increased the cost and complexity of submicron nanometer photomasks. The photomask layout is no longer an exact replica of the design layout. As a result, reliably verifying RET synthesis accuracy, structural integrity, and conformance to mask fabrication rules are crucial for the manufacture of nanometer regime VLSI designs. New EDA systems were recently developed consists of efficient wafer-patterning simulators that is able to solve the process physical equations for optical imaging, resist development and hence can achieve high degree accuracy required by mask verification tasks. These tools are able to efficiently evaluate mask performance by simulating edge displacement errors between wafer image and the intended layout. I'll discuss the capabilities for hot spot detection, line width variation analysis, and process window prediction capabilities with a sample practical layout. I'll also elaborate the potential of the new physical model simulator for improving circuit performance in physical layout synthesis.

### 1. Introduction

Reticle enhancement technologies for VDSM (Very Deep Sub Micron) integrated circuit manufacturing has dramatically complicated the mask data and increased the cost of advanced photomasks. The increase in pattern complexity due to optical proximity correction (OPC), the tight requirements for Critical Dimension (CD) control, and the difficulties in defect inspection and repair all contribute to the manufacturing cost increase. For phase shift masks (PSM), the problems are compounded by additional requirements such as controlling the etching of multiple materials, alignment of multiple layers, and inspecting small defect with weak signals. In addition to the added complexities in mask making, the growing array of Reticle Enhancement Technologies (RET) also put more constraints on the physical layout design and verification as

physical layouts must be RET compliant and conform to the mask fabrication rules. For instance, the avoidance of phase conflicts in alternating PSM and generating OPCfriendly design layout are examples of those new constraints. Physical design and verification flow nowadays have to be overhauled to address various wafers and photomasks manufacturing issues explicitly early in the design flow to achieve high quality fabricated silicon at a reasonable point on the price-performance curve. There are tremendous amount of research efforts from the industry and academia for this issue. The complexities in mask data and manufacturing make it highly desirable to verify and optimize the mask data independently before committing to the costly fabrication process. An effective method for post-RET mask data verification is to simulate its image on the silicon wafer and compare it with the original design intent. This method places mask data in its intended operating environment and evaluate its performance metrics that have direct impact on wafer imaging. A simulation based verification system can evaluate the process for a product and give warning on certain performance limiting spots on the layout and thus significantly reduce the risk of mask data errors. Once the troubling spots are identified, localized corrections can be applied to extend the process window in an intelligent way.

The existing model based mask layout verification systems have a few areas that require further improvement. First, they are typically implemented with the same simulation engine with model based OPC. Sharing the simulation engine with OPC, the verification also inherits the errors of the OPC model. The logical dependency jeopardizes the probability of finding OPC errors, and reduces the reliability of the verification. A process window is the range of process parameter variations under which the line width remains within limits Secondly; they employ empirical modeling approaches that cannot easily track acceptable variations in process conditions. In order to sample a different condition in the process window, a different set of models has to be developed, which consumes significant effort and time.

In addition, there is no inherent reason why one set empirical models can judge the result of another if they are derived from the same set of mathematical formulation and training patterns. A full-featured photolithography simulator for mask data verification has been developed for the past decade by the major EDA vendors. (Mentor Graphics, Cadence) This type of simulators has been used extensively in lithography process development where they have demonstrated high accuracy for process predictions.

A mask data verification flow around the physical lithography simulation core that is independent from the OPC engine, thus free from the logical dependency between OPC and its verification. The use of physical models opens the possibility for achieving higher prediction accuracy on complex layout configurations. In addition, physical model can naturally predict the pattern transfer behavior under process variations such as focus change. Furthermore, a physical layout design can efficiently leverage this physical model simulator to improve circuit performance and reduce the manufacturing variations.

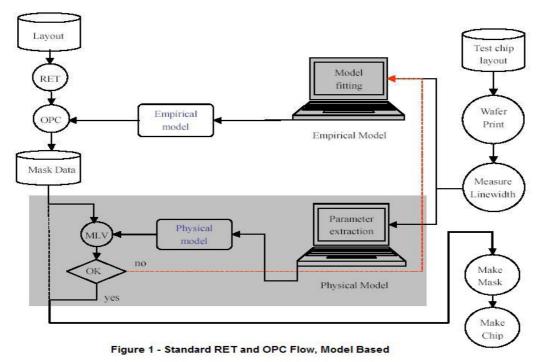

### 2. Physical Model Based Mask Layout Verification Flow

A standard flow for reticle enhancement and optical proximity correction with model based mask data verification block outlined with gray shading is shown in Figure 1. Here we consider model based OPC as an independent module because it is also needed for all other reticle enhancement techniques as well as standard binary masks. The main manufacturing flow is shown on the left hand side. The design layout from a customer is modified with reticle enhancement, followed by model based OPC to produce a set of mask geometry data that is suitable for mask manufacturing. The model generation flow is shown on the right, where a test layout is printed with the same pattern transfer process to produce an experimental data set for empirical model fitting. The resulting model can then be used in the OPC engine to predict the wafer CD error. From that, the amount of mask correction can be calculated.

To implement physical model based mask data verification, one must calibrate the physical model by extracting the process parameters from the same data set used for empirical model fitting. The main task here is to obtain resist-processing parameters such as development rate parameters and the post exposure bake diffusion length. The model can then be used in the mask layout verification (MLV) block to check the post-OPC mask data.

The verification can be performed on the entire mask or, to save processing time, on sections of the mask that are most likely to have pattern transfer problems. In case such problems are found, the simulation pattern produced by the physical model and the corresponding mask section can be added to the data set for recalibrating the empirical model. This feed back system will gradually make the empirical model to become more predictive over time as more and more cases are added to the training set. At some point,

the confidence level on the empirical model will reach a point when only occasional verification is needed in the full production mode.

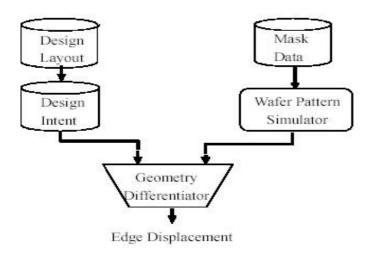

A detailed Physical Model based mask verification (PM-MLV) block is sown in Figure 2. The intended layout is derived from the design data by applying appropriate geometry operations such as scaling and sizing. This design intent is used as the standard for comparison. The other path of the verification process takes the mask layout as input and run through the wafer - patterning simulator. It simulates the wafer pattern by solving the equations describing image formation; resist exposure, post exposure bake, development and etching.

The simulation parameters are set such that the resist and etching processes are accurately captured in the model. By doing so, any changes on the RET type, exposure tools settings, and thin film stack can be predicted by the physical simulator.

The output of the high accuracy wafer-patterning simulator is the outline of wafer image. The pattern differentiator in Figure 2 compares this with the design intent and outputs the difference between the two patterns. The system characterizes the pattern difference by calculating the displacement of a line segment on the intended layout to its counterpart on the wafer image.

Positive edge displacement indicates that the wafer pattern falls outside the original design polygon, and is larger than the design intent. Similarly, a negative edge displacement indicates that wafer pattern is smaller than the design intent. In order to better capture the variations along a polygon edge, the edges of the design intent polygons are subdivided into shorter segments for edge displacement calculation. The subdivided edge segments are classified in a feature specific way in the data representing the design intent. For example, the segment located on a line end will carry a special flag indicating that line end pull back will be measured for this segment. Similarly, segments

at long line edge may carry another flag indicating that transistor gate or local interconnect variations will be measured at these segments. The feature specific classification flags help a user to impose different verification tolerance for each feature class of edges. By doing so, the verification process can be customized to better reflect the yield and performance of the product.

### 3. Hotspot Detection

Processing hotspots are the locations in the design where the magnitude of edge displacement is exceptionally large. Hotspots can form under a variety of conditions such as the original design being unfriendly to the RET that is applied to this chip, unanticipated pattern combinations in rule based OPC, or inaccuracies in model based OPC. When these hotspots fall on locations that are critical to the electrical performance of a device, they can reduce the yield and performance of the device.

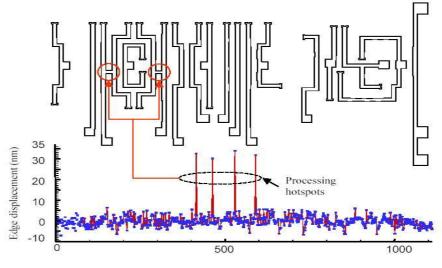

Figure 3 – Hot Spots Detection

Physical model based mask layout verification (PMMLV) can identify the hot spots and subsequently repair them by applying physical model based OPC (PM-OPC) at these locations. (Shown on Figure 3) The layout is for the poly gate layer with 90 nm target line width and dominating pitch of 300 nm. The cell size is approximately 11 um by 6.6 um. The mask layout is created by model based OPC using aerial image model only.

After OPC, the standard deviation of edge displacement error is calculated to be 0.71 nm, which confirms that the wafer pattern as predicted by the aerial image simulation is in good agreement with the design intent. The performance of this OPC mask created with simple aerial image model is verified using an optimized isofocal2 resist recipe that is a more realistic description of the patterning process. Also shown in Figure 3 is the output of the pattern differentiator. The edge displacements are evaluated on 887 line segments on this cell.

Our PMMLV process discovers four segments with large edge displacement as shown in Figure 3. Interactive exploration shows that these points are located on either side of the short horizontal bars in "H" shaped patterns. The standard deviation for edge displacement also increased 240% from 0.71 nm to 1.7 nm. This set of verification result shows that the mask data created by OPC with simple aerial image model would result in worse process and circuit performance than that suggested by the small correction residual.

### 4. Proximity Induced Line Width Variation Statistics

Variations in line width due to lithography and etching often limit the performance of a circuit. The line width variation pattern changes as focus varies within allowed process control limits. Existing OPC methodology is aimed at reducing the line width variability at a nominal focus point, without considering the potential impact of focus change.

In this case, physical model can be applied to obtain more complete and meaningful line width variation statistics by considering focus and other process parameter variations, the result of which can be used for performance optimization.

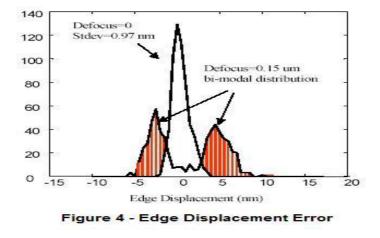

Figure 4 show the histogram for the edge displacement under defocus for a mask produced by physical model based OPC. At best focus, the mean edge displacement is zero, indicating an on-target CD distribution at 90 nm. The standard deviation of the edge displacement is 0.97 nm, which represents the residual of PM-OPC process. When this mask is printed under 0.15 um of defocus, the distribution broadens into a bi-modal form. We can clearly see the increase in the edge displacement envelope under defocus.

The mean of the edge displacement, however, still stays at near zero, as in the best focus case. On average, the line width is not changed under defocus, as the number of edges with positive displacement roughly equals the number of edges with negative edge displacement. This behavior is consistent with theis focal process model we developed for this circuit. On the other hand, if the same circuit layout is corrected with aerial image model and verified using aerial image model, a -14 nm average edge displacement will result with 0.15 um defocus. The range of variation also increases by nearly a factor

of 7 from 0.71 to 3.5nm. The large difference in response between this and physical model based OPC and verification shows the strong influence of models on the OPC and verification results. The edge displacement statistics produced by the physical model based OPC and verification process can be used in physical design flow to make ECAD tools manufacturability aware such that process variations can be reduced and circuit performance can be improved. This concept is illustrated in the following section.

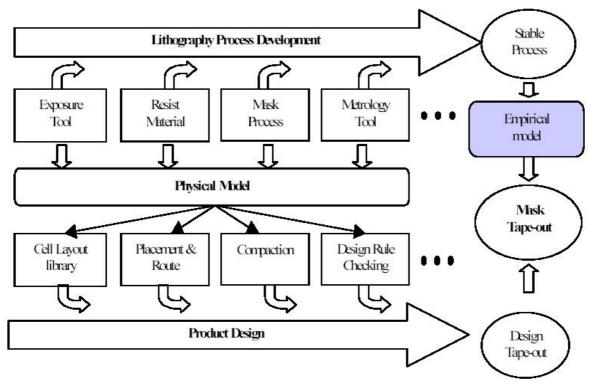

### 5. Impacts on Physical Design Stage and Flows

The circuit design and mask processing are still basically separated from each other in current design and manufacturing flow. The design and process development team communicate only through a set of design rules. As we moving into VDSM technologies, we have to explicitly addressing various manufacturing issues early in the physical design flow to attain the best design performance, process window and uniformity in manufacture. Recent approach to this change in design-manufacturing interaction is through advanced process simulation that is transparent to circuit designers. Figure 5 shows recent mode of design-process interaction. For each new technology node, the equipment community publishes tool specifications early in the process development cycle. These parameters are used to construct physical models well before an intended process becomes stable. These physical models are applied early in the design phase to ensure that the layout can be optimized for the target processing technology.

Figure 5 - Recent Design and Process Flow

Now designers can pre-characterize OPC related information for each cell and use this

information during placement to produce more OPC-friendly layouts. Specifically, we need to know how sensitive (*sensitive factor*) the critical dimensions (CDs) in a cell to its neighborhood patterns and how difficult to compensate the CDs in the cell. If an aggressive OPC is needed (like sub-resolution assistant features which may be outside of original cell layout), then the cell layout area has to be bloated. Now we can build different *OPC configurations* for each cell in the library, each of them has different layout area and OPC performance in terms of statistic errors on CDs.

### 6. Power Leakage

In the following, I'll show how different OPC configurations can affect the power leakage of a CMOS device. Static power leakage becomes a major concern for designers today, as it accounts for an increasing and significant portion of the total power budget in high-end microprocessors. This situation will become even worse with further reduction of threshold voltage (Vth) of MOS devices. CMOS device leakage currents *Isub* varies exponentially with the change of channel length *L* as shown in the formula below:

Isub = K(1/L)exp(-CL)

where *K* and *C* are device dependent constants. As a result, the sub-threshold leakage currents are extremely sensitive to the channel length variations. The mean leakage current of a chip under process variations can deviate significantly from the nominal leakage current in a typical 0.18 um COMS process. The mean leakage current and the standard deviation of a PMOS transistor vary with the changes of its channel lengths due to different OPC configurations. The process used here is TSMC high-performance 0.13 um technology. Table 1 shows our calculated mean leakage and standard deviation of mean leakage of sub-threshold current of PMOS device under different OPC configurations.

| OPC<br>Cfg       | Stdev. of<br>L<br>σ (nm) | %<br>Variation<br>(3σ) | Mean<br>Isub<br>(nA) | Stdev.<br>Of<br>Isub<br>(nA) |

|------------------|--------------------------|------------------------|----------------------|------------------------------|

| Phy-Model<br>OPC | 0.5                      | 1.8%                   | 4.0205               | 0.48                         |

| Std. OPC         | 2                        | 7.5%                   | 4.4661               | 1.88                         |

| No OPC           | 5                        | 18.8%                  | 6.9614               | 3.84                         |

### Table 1 - Leakage Current Variation - PMOS Device Channel Length Variation Range: L=0.08 um W/L=5

It is shown that average leakage will significantly deviate from nominal value if no OPC is used. If OPC is employed, but is not optimized due to poor modeling or unexpected presence of neighborhood patterns, the average leakage will still %10 higher than the

nominal value. With physical model based OPC and predictable neighborhood patterns, the channel length variation can be well controlled. As a result, the mean leakage current and its variation are reduced. The statistical performance information of library cells can be leveraged during physical layout synthesis. For example, in the detailed placement phase, all the timing critical or leakage cells (called *critical cells* in the sequel), which are also OPC sensitive are instantiated with their best OPC configurations. Placement will legalize the added areas of those cells during refinement. If a cell is no longer a critical cell, its original layout will be used again. For OPC high sensitive critical cells, a fast on-line OPC process can be invoked to estimate the statistic errors for its neighborhood patterns. If the errors are still too large, some local cell swapping may be applied to get different neighborhood patterns or get more open area (adding dummy cells) around the critical cells or even re-synthesis the corresponding logics to make the resulting cell less OPC sensitive.

This process is repeated until OPC CD errors on all the high sensitive critical cells are under control. Such cell-based OPC and the manufacturability-aware placement strategy bring many advantages: First, it will improve the circuit performance and reduce the performance variations and thus unnecessary guard-banding, and lead to much more predictable circuit performances and manufacture yield. Second, with each layout precertified and OPC optimized by physical models, the final tape-out process would likely to be much simpler than the whole chip-wide, essentially flattened OPC and verification processes used today.

### 7. Conclusions

We observed mask data verification flow in order to prevent data problems to propagate to the expensive mask making and wafer printing stage. New flows, presented to the industry by the major EDA vendors leverages the high accuracy of a wafer patterning simulator that predicts the wafer image by solving the equations that describe the physics and chemistry of the pattern transfer process. These systems address the problems of the existing empirical model based OPC/RET flow and can be applied in parallel to improve the reliability and quality of the mask data. We discussed how edge displacement statistical information obtained from the new model simulator can be leveraged during physical synthesis flow to reduce the performance variations and improve the device manufacturability. No Doubt, There is a tremendous impact on the IC Physical Design and verification phase due to the sub-wavelength optical lithography and this will get more critical as progressing towards ultra sub-micron process. EDA vendors are in constant race to implement manufacturability flows for advanced process. In the next decade we will witness a major increase in efforts from industry and academy in the RET arena.

### References

[1] P. Gilbert et al., A High Performance 1.5V, 0.10um Gate Length CMOS Technology with Scaled Copper Metalization, IEDM 1998, pp. 1013-1016.

[2] W. B. Glendinning and J. N. Helbert, Handbook of VLSI Microlithography: Principles, Technology, and Applications, Noyes Publications, 1991.

[3] L. Gwennap, IC Vendors Prepare for 0.25-Micron Leap, Micro-

processor Report, September 16 (1996), pp. 11{15.

[4] F. O. Hadlock, Finding a Maximum Cut of a Planar Graph inPolynomial Time, SIAM J. Computing, 4 (1975), pp. 221 {225.

[5] A. B. Kahng, S. Muddu, E. Sarto, and R. Sharma, InterconnectTuning Strategies for High-Performance ICs, in Proc. Confer-ence on Design Automation and Test in Europe,.

[6] A. B. Kahng, G. Robins, A. Singh, H. Wang, and A. Zelikovsky, Filling and Slotting : Analysis and Algorithms, in Proc. Inter-national Symposium on Physical Design, 1998, pp. 95{102.

[7] A. B. Kahng, H. Wang, and A. Zelikovsky, Automated Layoutand Phase Assignment Techniques for Dark Field Alternatingtomask Technology, 1998.

[8] H. Landis, P. Burke, W. Cote, W. Hill, C. Hoffman, C. Kaanta,C. Koburger, W. Lange, M. Leach, and S. Luce, Integration of Chemical-Mechanical Polishing into CMOS Integrated CircuitManufacturing, Thin Solid Films, 220 (1992), pp. 1 {7.

[9] M. D. Levenson, Wavefront engineering from 500 nm to 100nm CD, in Proceedings of the SPIE - The International Societyor Optical Engineering, vol. 3049, 1997, pp. 2 {13.

[10] M. D. Levenson, N. S. Viswanathan, and R. A. Simpson,Improving Resolution in Photolithography with a Phase-Shifting Mask, IEEE Trans. on Electron Devices [11] L. Liebmann, A. Molless, R. Ferguson, A. Wong, and S. Mans-field, Understanding Across Chip Line Width Variation: TheFirst Step Toward Optical

Proximity Correction, in SPIE, vol. 3051, 1997, pp. 124{136.

[12] L. W. Liebmann, T. H. Newman, R. A. Ferguson, R. M. Martino, A. F. Molless, M. O. Neisser, and J. T. Weed, A Comprehen-sive Evaluation of Major Phase Shift Mask Technologies forIsolated Gate Structures in Logic Designs, in SPIE, vol. 2197,1994,

[13] H.-Y. Liu, L. Karklin, Y.-T. Wang, and Y. C. Pati, The Ap-plication of Alternating Phase-Shifting Masks to 140 nm GatePatterning (II): Mask Design and Manufacturing Tolerances, in SPIE Optical Microlithography XI, vol. 3334, Feb. 1998, pp.1-14.

[14] H.-Y. Liu, L. Karklin, Y.-T. Wang, and Y. C. Pati, The Appli-cation of Alternating Phase-Shifting Masks to 140 nm GatePatterning: Line Width Control Improvements and DesignOptimization, in SPIE 17th Annual BACUS Symposium on Pho-tomask Technology, vol. SPIE 3236, 1998, pp. 328{337.[15] Y. Liu, A. Zakhor, and M. A. Zuniga, Computer-Aided PhaseShift Mask Design with Reduced Complexity, IEEE Transac-tions on Semiconductor Manufacturing, 9 (1996), pp. 170{181.

[16] W. Maly, Computer-aided design for VLSI circuit manufac-turability, Proceedings of IEEE, 78 (1990), pp. 356{392.[17] W. Maly, Moore's Law and Physical Design of ICs, in Proc.International Symposium on Physical Design, Monterey, Califor-nia, April 1998. special address.

[18] SEMATECH, Workshop Notes, in 3rd SEMATECH Litho-Design Workshop, Skamania Lodge, February 1996.

[19] A. Moniwa, T. Terasawa, N. Hasegawa, and S. Okazaki, Algo-rithm for Phase-Shift Mask Design with Priority on ShifterPlacement, Jpn. J. Appl. Phys., 32 (1993),

[20] A. Moniwa, T. Terasawa, K. Nakajo, J. Sakemi, and S. Okazaki, Heuristic Method for Phase-Conict Minimization in Auto-matic Phase-Shift Mask Design, Jpn. J.

[21] J. Nistler, G. Hughes, A. Muray, and J. Wiley, Issues Asso-ciated with the

Commercialization of Phase Shift Masks, inSPIE 11th Annual BACUS Symposium on Photomask Technol-ogy, vol. SPIE 1604, 1991, pp. 236{264.

[22] K. Ooi, S. Hara, and K. Koyama, Computer Aided Design Soft-ware for Designing Phase-Shifting Masks, Jpn. J. Appl. Phys., 32 (1993), pp. 5887 [5891.

[23] K. Ooi, K. Koyama, and M. Kiryu, Method of Designing Phase-Shifting Masks Utilizing a Compactor, Jpn. J. Appl. Phys., 33(1993), pp. 6774{6778.

[24] G. I. Orlova and Y. G. Dorfman, Finding the Maximum Cutin a Graph, Engr. Cybernetics, 10 (1972), pp. 502{506.

[25] P. Rai-Choudhury, Handbook of Microlithography, Microma-chining, and Microfabrication, vol. 1: Microlithography, SPIEOptical Engineering Press, Bellingham,

[26] F. M. Schellenberg, H. Zhang, and J. Morrow, Evaluation of OPC E\_cacy, in Proc. Intl. Symp. on Aerospace/Defense Sens-ing and Dual-Use Photonics, vol. 2726, 1996.

[27] Alfred Wong, "Resolution enhancement techniques in optical lithography", SPIE Oct. 2001

[28] M. Rieger, L. Stirniman, "TCAD physical verification for reticle enhancement techniques", Solid State Technology Vol. 43, No 7, (134) 2000.

[29] W. G. Oldham, S. N. Nandgaonkar, A. R. Neureuther, and M. O'Toole, "A general simulator for VLSI lithography and etching processes: Part I – application to projection lithography," IEEE Trans. Electron Devices ED-26, No. 4 (717) 1979.

[30] C. A. Mack, "PROLITH: a comprehensive optical lithography model," Proc. SPIE. [31] Qi-De Qian, F. A. Leon, "Fast Algorithms for 3D high NA lithography simulation", Proc. SPIE Vol. 2440 (372) 1995.

[32] Chris A. Mack, Ching-Bo Juang, "Comparison of scalar and vector modeling of image formation in photoresist", Proc. SPIE Vol. 2440 (381) 1995.

[33] A. Sekiguchi, M. Isono, and T. Matsuzawa, "Measurement of parameters for simulation of 193 nm lithography using Fourier transform Infrared baking system." Jpn. J. Appl. Phys. Vol 38 4936 1999

[34] A.B. Kahng and Y.C. Pati, "Subwavelength optical lithography: challenges and impact on physical design", Proc. ACM intel. Symp. On Physical Design, pp.112—119, April 1999.

[35] W. Grobman, M. Thompson, R. Wang, C. Yuan, R. Tian and E. Demircan, "Reticle Enhancement Technology: Implications and Challenges for Physical Design", Proc. ACM/IEEE 38th Design Automation Conference. pp.73-78, June 2001.

[36] W. Maly, "Computer-aided design for VLSI circuit manufacturability", Proc. of IEEE, 78, pp.356—392, 1999.

[37] A. Srivastava, R. Bai, D. Blaauw and D. Sylvester, "Modeling and analysis of leakage power considering within-die process variations", Proc. Intl. Symp. on Low Power Electronics and Design (ISLPE), pp.64—67, Aug. 2002.

[38] F.M. Schellenberg, L. Capodieci and B. Socha, "Adoption of OPC and the impact on design and layout", Proc. ACM/IEEE 38th Design Automation Conference. Pp.89 --92, June 2001.

[39] TSMC 0.13um CMOS Process Technology

## Fundamentals of Web Site Acceleration Performance Starts at the Web Server

By Port80 Software

### Abstract

his paper outlines a common sense, cost-effective approach to lowering total cost of ownership and improving Web site and Web application performance according to two simple principles:

- Send as little data as possible

- Send it as infrequently as possible

We will explore "best practice" strategies that can be systematically employed in Web front-end source code and at the origin server in order to achieve performance improvements. These basic strategies, which all avoid expensive hardware solutions in favor of software and business process enhancements, include:

- <u>Code optimization</u>

- <u>Cache control</u>

- <u>HTTP compression</u>

We assume that our typical reader is responsible in some way for development and/or management of a Web site or application running on one or more Windows servers with Internet Information Services (<u>IIS</u>) and that he or she has an interest in improving its performance as much as possible without deploying additional hardware (such as dedicated acceleration appliances) or services (such as Content Distribution Networks).

As we examine each strategy, we will explore the potential benefits to a variety of different Web sites and applications in terms of three vital metrics:

- Faster Web page loads and an improved user experience, translating into higher revenue and increased efficiencies

- Reduction of bandwidth utilization and increased, ongoing savings

- Consolidation of the number of server resources required to deliver existing sites and applications

We will suggest relatively inexpensive software tools that will leverage common Web standards in order to maximize hardware and network resources, thus improving Web site and application performance while lowering the total cost of ownership of Web infrastructure.

### Measuring Web Site Performance

The most valuable measurement of Web site performance from an end user's perspective

is the amount of time needed to display a requested Web page. The most important metric of page load time is Time to First Byte (<u>TTFB</u>). Defined as the amount of time it takes to deliver the first byte of the requested page to the end user, TTFB represents the visitor's initial confirmation that a Web site or application is responding. Following Time to First Byte is the metric of <u>Throughput</u>, or how many requests can be served by a Web site or application in a given time period. A user expects text, images, and other elements to load swiftly and methodically — failure in any of these metrics results in the perception of poor performance, which can very quickly lead to visitor frustration and abandonment of the site.

With a large enough budget for heavy infrastructure improvements, any server's connection to the Internet can always be improved. However, we are interested in cases in which these common measures of Web site performance degrade due to uncontrollable network conditions and in which expensive, complex hardware solutions are not feasible or desirable. As Web sites and applications grow increasingly complex with bulky code and third party applications, users — many of whom are still using dial-up connections — must download an increasing amount of data to access a Web site or application. Even when highly efficient applications are made available on fast Wide Area Networks (WANs) like corporate extranets, segments of the network will always be susceptible to bottlenecks, and the user may experience unacceptably long page load times. If the Web server's source code and management software are not optimized to keep pace with rising site traffic and application complexity, administrators will waste server resources and bandwidth, and users will be presented with slower, easier-to-abandon Web sites.

Optimizing content and content delivery has been proven to improve Web page delivery speed in case studies conducted by the <u>World Wide Web Consortium</u> and has been espoused by Web optimization experts such as <u>Andy King</u>. Until recently, content optimization required difficult and time-consuming manual coding, but this can now be achieved through the implementation of inexpensive software tools and unobtrusive changes in development and deployment processes. Similarly, while optimizing content delivery once demanded expensive hardware and infrastructure investments, today it can be accomplished with affordable, easy-to-deploy server software tools.

<u>Code optimization</u>, <u>cache control</u>, and <u>HTTP compression</u> are strategies that focus on sending as little data as necessary as infrequently as possible to optimize performance in an existing Web application's front-end code and on the origin Web server delivering that content to Web browsers.

### **Code Optimization**

Source code optimization is an important but often overlooked application of the "send as little data as possible" principle. As a Web site or application acceleration strategy, its chief benefit is that the technique can provide substantial reductions in network payloads without requiring any additional processing on the origin server. Source code optimization should be implemented as a pre-deployment step through which all additions and changes to the front-end source code (including <u>markup</u>, <u>style sheets</u>, and

<u>client-side scripts</u>) normally pass before being uploaded to the "live" production site or application.

### Beyond White Space Removal

While traditional "white space removal" (the elimination of superfluous spaces, tabs, new lines, and comments) can result in modest savings of 10 to 15 percent in typical HTML and CSS files, a code optimizer modeled after a traditional software compiler can achieve a much higher level of optimization on all text-based files. Because it possesses a site-wide contextual awareness, such a tool can employ more aggressive tactics, including condensing function and variable names, re-mapping lengthy identifiers and <u>URL or URI</u> paths, and through the use of a real JavaScript parser, even streamline lines of code.

Until recently, this approach has been the exclusive domain of JavaScript experts with the time and patience to write very terse code. In addition, hand coding still presented limitations to site expansion and code readability because it maintains a single optimized code base for both development and deployment. It is both safer and more efficient to use next generation development tools like the <u>w3compiler</u> that preserve developer-friendly versions of Web site files as well as the highly optimized versions exclusively for delivery on the Web.