## 实现低漏电流同时保证 EMI 性能的电源设计

在 AC-DC 开关电源中,漏电流最主要的来源是 Y 类电容。通过使用变压器屏蔽绕组或在输入级加入一个扼流圈,可以显著地降低 Y 电容的数值或在某些场合去除它,从而降低漏电流并且仍满足有一定裕量的传导 EMI 限制。实现这些目标的解决方案会在本文得到分析。

大多数 AD/DC 电源都在高压的交流输入端与低压的直流输出端之间实现了隔离。诸如 UL1950 之类的安全标准会同时指定了绝缘强度(例如 3 千伏 VAC 耐冲电压)和最大漏电流。漏电流是指当设备的可接触部分以一定的阻抗连接到保护地时流经初级与次级绝缘屏障之间的电流。漏电流标准确保了人员的安全,防止当使用者碰触到输出端或电源外壳时其身体成为电流泄放至大地的路径的一部分。

允许流过的最大漏电流基于应用场合有着具体的分类。过去,仅对诸如医疗设备(患者极有可能或确定必须接触设备的带电部分)等特殊应用场合有低的漏电流要求。在那些应用场合中的设备不得不满足比 IT 设备严格得多的要求。针对医疗和 IT 设备的漏电流限制规范分别是 IEC60601-1、IEC60950。

但是,如今还有其它理由需要去进行低漏电设计。例如,现在很多移动电话都有金属的外壳,与其配套的充电器必须满足手持设备制造商们制订的比现行安全标准要低的漏电流规范。这是为了防止消费者(特别是在像充满蒸汽的浴室之类的潮湿环境中)拿着正在充电的手机时有触电感。与电话设备(无绳电话、电话答录机、DSL modem 等)配套的电源通常必须有很低的工频泄漏以避免可听得见的嗡嗡声耦合到电话线路中。进行低漏电设计还可潜在地节省成本,例如减小电源中必需的 EMI 滤波元件的尺寸和/或数量。

追根溯源:漏电流究竟从何而来?

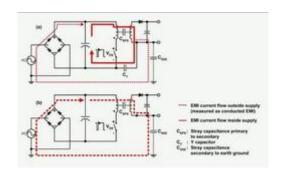

在 AC-DC 开关电源中,漏电流最主要的来源是 Y 类电容。Y 类电容是经过安全机构认证(外表常为橙色或蓝色)、可以用于将绝缘屏障桥接起来的电容(参见图 1a),为位移电流(产生于开关过程)提供返回路径以防止 EMI。任何能流出电源的高频电流(通过许多我们将在后面讲到的途径)都将通过交流进线返回,并产生传导 EMI。在图 1a 中,Y 电容避免了许多 EMI 电流,使得其中绝大多数都局限在电源内部,而在图 1b 中,这些 EMI 电流必定全部流出到电源之外。

一般而言,电源中的Y电容的容量值越大,电源产生的EMI就越小,与此相反,流过绝缘屏障的漏电流则越大。

$$C_{Y(MAX)} = \frac{I_{LEAK(MAX)}}{V_{AC(MAX)} \cdot 2 \cdot \pi \cdot f_{LINE}} - C_{SPS}$$

$$= \frac{0.25 \cdot 10^{-3}}{265 \cdot 2 \cdot \pi \cdot 50} - C_{SPS}$$

$$= 2.95nF$$

公式 1 可以用来估算在不超出安全界限的情况下允许使用的 Y 电容最大值。对于一个两线(没有保护地)、带浮动输出的通用输入电源,向下舍入到标准数值就得到 Y 电容最大值大约为 2.2nF。而对于仅适用于 100/115VAC 的设计,此数值会提升到 3.3nF。

仅是简单地将 Y 电容从电路中移除或减小其数值一般情况下不太可行,因为这样做会显著增加 EMI (见图 2b)。而在电路中增加共模扼流圈或其它滤波元件又会增加成本。因此,我们必须将注意力集中到如何降低 EMI 电流上。

降低共模 EMI 电流的技巧

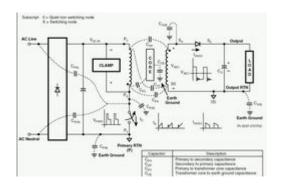

虽然详尽地分析 EMI 电流所有的来源已经超出了本文的范围,但图 3 还是给出了被初级与次级开关波形驱动的 EMI 电流典型路径概览。目前已有一些减小共模 EMI 电流的方法。尽管在变压器绕线层之间使用带状物增加绕线层间距离可以减小层间电容,但单独使用这一方法只能很有限地减小 EMI 电流。长期以来在工频变压器中一直应用屏蔽绕组来降低噪声与耦合,在开关变压器中这一方法同样有效。如图 5 中 EMI 图形所示,在开关变压器中使用屏蔽绕组是降低共模 EMI 电流最有效的方法,而且对电源总体成本的影响最小。

以下是在 3W AC-DC 电源中使用变压器屏蔽绕组的例子:

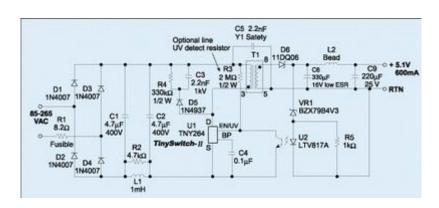

图 4 是一个 5. 1V、600mA 电源的电路图,它基于 Power Integrations 公司 TinySwitch-II 芯片,具有一个简单的 双绕组变压器。由于这款芯片可以自供电,所以变压器中就不需要辅助绕组。此设计是蜂窝电话、PDA 或数码相机充电器的典型电路。

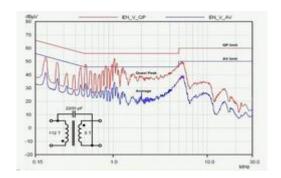

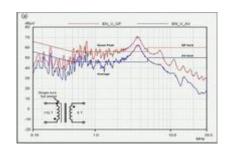

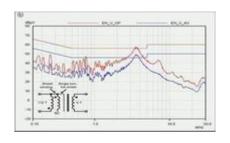

TinySwitch-II 芯片通过调制其开关频率(称为频率抖动)来降低 EMI, 但如果没有变压器中的屏蔽绕组, 此电路就需要一个 2. 2nF 的 Y 电容以满足 EMI 要求(参见图 2a)。移除 Y 电容后引起的 EMI 如图 2b 所示,这样的结果显然让人无法接受。

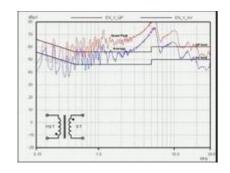

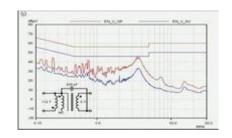

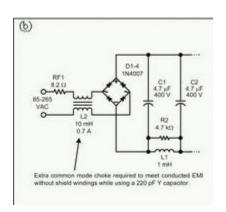

在变压器初级与次级绕组之间加入一个单匝箔屏蔽绕组,使得测量到的 EMI 下降了大约 10dB(见图 5a)。用一个额外的屏蔽绕组进行补充,可进一步下降 10dB(见图 5b)。这样仅使用一个 220pF 的 Y 电容就可获得一个有 10dB 余量的好方案(图 5c),将漏电流从 183uA 降到 18uA。不使用屏蔽绕组的电路可获得几乎同样的 EMI 性能(图 6a),但必须在输入级(图 6b)加入一个扼流圈 L2(除了已有的差模滤波电感 L1 之外)。根据每个应用电路的不同需求,可以给变压器再加入第三个屏蔽绕组,从而进一步降低 Y 电容的数值。

由于屏蔽绕组与初级侧开关电路和次级侧整流电路之间的相互作用,使得共模位移电流得以削弱或彻底抑制,让详尽的分析变得不再必要。但是,每一个设计的需求各不相同,这是由诸如 PCB 板上的元件布局、电路板及磁性元件和机壳金属板之间的接近程度、变压器的尺寸以及伏-秒率、匝数范围、匝数比等因素决定的。因此,在优化每一个设计的屏蔽绕组时试验与失误是在所难免的。即便如此,关于屏蔽绕组布局的基本规律一贯以来一般还是适用的。

这些关于屏蔽绕组的技巧对于任何功率水平的电源都很有效,在www.powerint.com/appcircuits 这个网址上可以找到更多的在变压器上使用屏蔽绕组的例子。

## 本文小结

由于人与电源供电设备之间的交互操作关系,许多当今的电源规范都要求更低的漏电流值。因此,就要求电源设计者从电路中移除用以保证 EMI 性能的安全 Y 电容或降低其数值。通过使用变压器屏蔽绕组,可以显著地降低 Y 电容的数值或在某些场合去除 Y 电容,同时降低漏电流并且仍然满足有一定裕量的传导 EMI 限制。如今已经有了可以用来达到上述目标并且成本可以接受的解决方案。