# **SS-11X Application Notes**

Sony corporation

Semiconductor Business Unit

## **CONTENTS**

| 1.   | Syste | m Outline                                                 | 1  |

|------|-------|-----------------------------------------------------------|----|

| 1.1. | SS-   | 11X System Outline                                        | 1  |

| 2.   | Syste | m Configuration                                           | 2  |

| 2.1. | Inte  | rnal System                                               | 2  |

| 2.2. | Line  | Lock System                                               | 2  |

| 2.3. | Inte  | rnal / Line Lock Switching System                         | 3  |

| 2.4. | SS-   | 11X System Setting Method                                 | 4  |

| 2.   | 4.1.  | Internal System Settings                                  | 4  |

| 2.   | 4.2.  | Line Lock System Settings                                 | 5  |

| 2.   | 4.3.  | Internal / Line Lock Switching System Settings            |    |

| 2.5. | ICs   | Comprising the System                                     | 10 |

| 3.   | -     | neral Circuits                                            |    |

| 3.1. | Initi | ally Occupied Terminals                                   | 11 |

| 3.   | 1.1.  | If No Valid Data in EEPROM                                | 11 |

| 3.   | 1.2.  | Port Driver pin Specification                             | 11 |

| 3.2. | Pro   | cessing of Empty Pins                                     | 12 |

| 3.   | 2.1.  | Processing of Empty Pins in case DAC is not used          | 12 |

| 3.   | 2.2.  | Processing of Empty Pins in case Internal EVR is not used | 12 |

| 3.3. | Osc   | illator Circuit Periphery                                 | 13 |

| 3.   | 3.1.  | Internal System                                           | 13 |

| 3.   | 3.2.  | Line Lock System                                          | 14 |

| 3.   | 3.3.  | Internal/Line Lock Switching System                       | 15 |

| 3.4. | Out   | put Circuit Periphery                                     | 16 |

| 3.   | 4.1.  | Analog Output (YCMIX Output, YC Separated Output)         | 16 |

| 3.   | 4.2.  | Digital Output                                            | 19 |

| 3.   | 4.3.  | BPF Circuit Example                                       | 19 |

| 3.5. | H-D   | river Voltage Step-up Circuit                             | 21 |

| 3.6. | Cor   | nmunication Circuit                                       | 22 |

| 3.   | 6.1.  | RS-232C Communication                                     | 22 |

| 3.   | 6.2.  | External Microcomputer Communication                      | 22 |

| 3.7. | Res   | et Circuit                                                | 23 |

| 3.   | 7.1.  | Outline                                                   | 23 |

| 3.   | 7.2.  | Example Reset Circuit and Timing Chart                    | 23 |

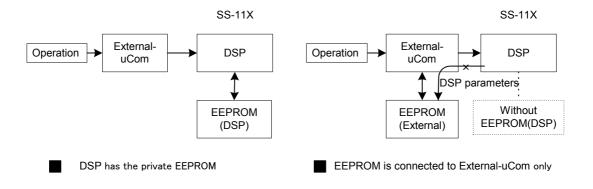

| 3.8. | EEF   | PROM Connection                                           | 24 |

| 3.   | 8.1.  | Outline                                                   | 24 |

| 3.   | 8.2.  | Connection Method                                         | 24 |

| 3.9. | Inte  | rnal EVR                                                  | 25 |

| 3.   | 9.1.  | Outline                                                   | 25 |

| 3.   | 9.2.  | Internal EVR Initial Settings                             | 25 |

| 3.   | 9.3.  | Internal EVR User Setting Method.                         | 25 |

| 3.10 | ). C  | ptical Filters                                            | 26 |

| 3.   | 10.1. | Outline                                                   | 26 |

| 4.   | Paran | neter Control Priority Ranking                            | 27 |

| 4. | .1. Pa  | rameter Priority Ranking                                      | 27 |

|----|---------|---------------------------------------------------------------|----|

|    | 4.1.1.  | Communication Categories                                      | 27 |

| 4. | .2. EE  | PROM Write Method                                             | 28 |

|    | 4.2.1.  | Initial Write (EEPROM Empty State)                            | 28 |

|    | 4.2.2.  | Second and Subsequent Write (when not including CAT12)        | 29 |

| 5. | Powe    | er Source                                                     | 30 |

| 5. | .1. Su  | pply Voltage                                                  | 30 |

|    | 5.1.1.  | Supply Voltage Accuracy                                       | 30 |

|    | 5.1.2.  | Power Consumption                                             | 31 |

|    | 5.1.3.  | Power-on Sequence                                             | 31 |

| 6. | CCD     | Type Selection                                                | 32 |

| 6. | .1. CC  | CD type                                                       | 32 |

| 6. | .2. Op  | eration Mode Selection for Each CCD                           | 33 |

|    | 6.2.1.  | System Configuration and MODESEL                              | 33 |

| 6. | .3. lm  | portant Information on Wiring                                 | 34 |

|    | 6.3.1.  | Drive Circuit Changes                                         | 34 |

|    | 6.3.2.  | Frequency Response Changes                                    | 36 |

| 6. | .4. CC  | D Primary Color Separation Matrix                             | 37 |

|    | 6.4.1.  | Recommended Parameter's Value                                 | 37 |

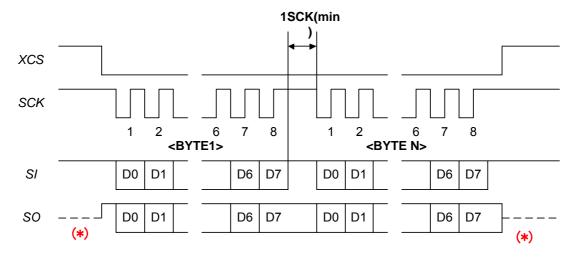

| 7. | Com     | munication Methods                                            | 38 |

| 7. | .1. RS  | 232C Communication                                            | 38 |

|    | 7.1.1.  | Interface                                                     | 38 |

|    | 7.1.2.  | Control Software Communication Method                         | 39 |

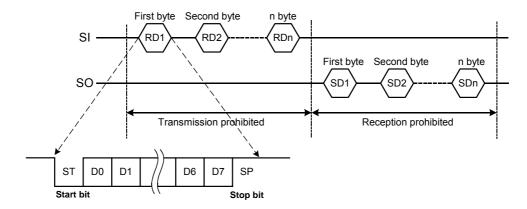

|    | 7.1.3.  | Communication Timing                                          | 40 |

|    | 7.1.4.  | Communication Format                                          | 41 |

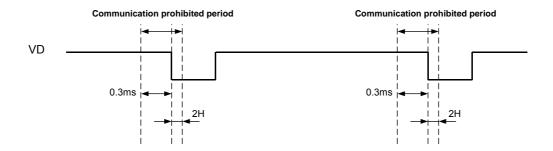

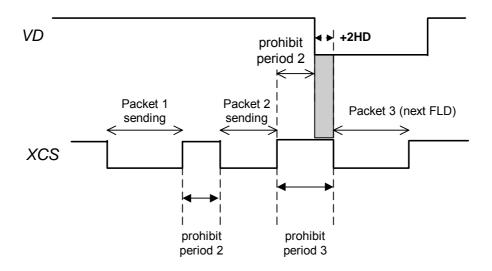

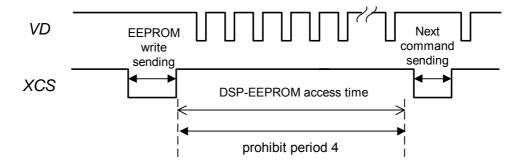

|    | 7.1.5.  | Serial Communication Prohibited Period                        | 42 |

| 8. | Basic   | c Adjustments                                                 | 43 |

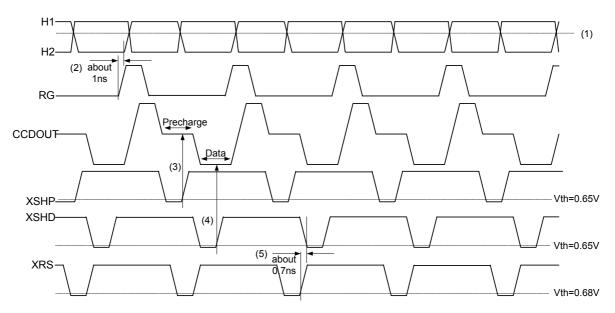

| 8. | .1. TG  | Phase Adjustment                                              | 43 |

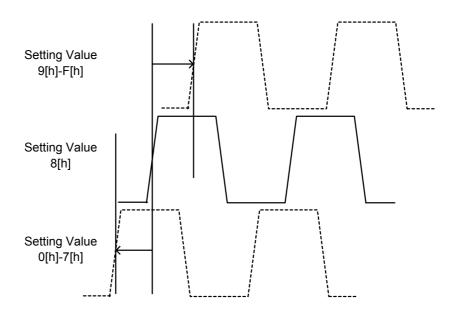

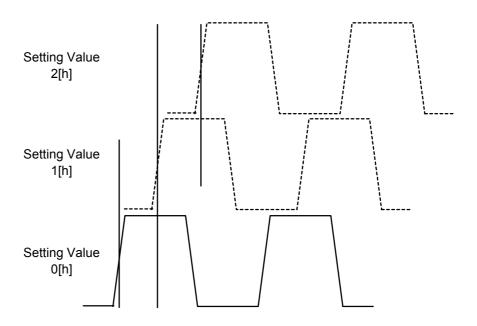

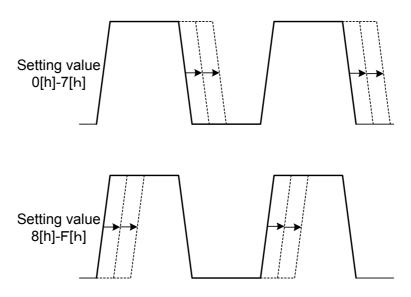

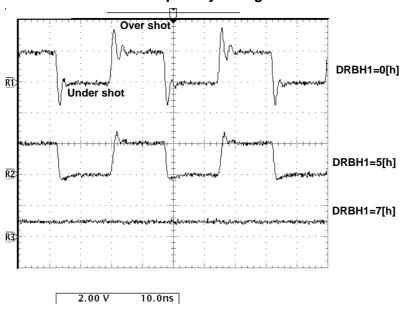

|    | 8.1.1.  | Phase and Drive Ability Adjustment Method                     | 44 |

| 8. | .2. AG  | C Minimum Adjustment                                          | 49 |

|    | 8.2.1.  | AGC Minimum Adjustment Method                                 | 49 |

| 8. | .3. Pre | e-White Balance Adjustment                                    | 50 |

|    | 8.3.1.  | Pre-White Balance Adjustment Method                           | 50 |

|    | 8.3.2.  | Operation Frame Offset Setting                                | 51 |

| 8. | .4. CC  | D Blemish Detection and Compensation                          | 52 |

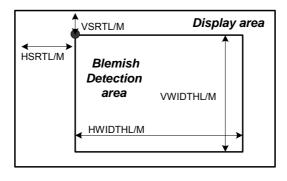

|    | 8.4.1.  | CCD Blemish Detection Method Types and Setting Procedures     | 52 |

|    | 8.4.2.  | Blemish Detection Setting Parameters                          | 53 |

| 9. | Desc    | ription of Each Functions                                     | 57 |

| 9. | .1. Po  | rt Driver Function                                            | 57 |

|    | 9.1.1.  | Port Driver Function Description                              | 57 |

|    | 9.1.2.  | Port Driver Initial Settings, Depending on Presence of EEPROM | 57 |

|    | 9.1.3.  | Description of Port Driver Parameters                         | 58 |

|    | 9.1.4.  | Port Driver Setting Method                                    | 60 |

|    | 9.1.5.  | Shift Function using the Port Drivers                         | 63 |

|    | 916     | Precautions for Port Driver Configuration                     | 65 |

| 9.1  | 1.7.  | Port Driver Setting Reflection Method         | 65  |

|------|-------|-----------------------------------------------|-----|

| 9.1  | 1.8.  | Conditions for Disabling the Port Drivers     | 66  |

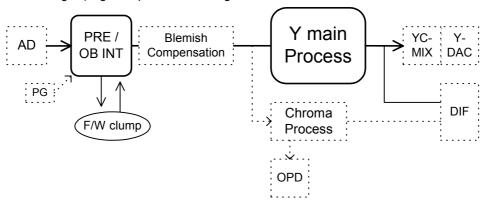

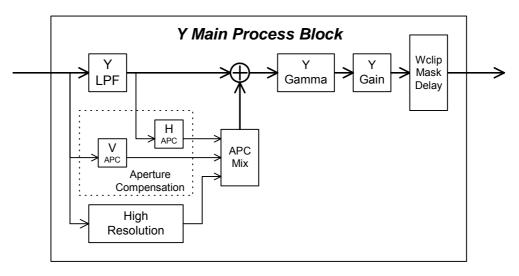

| 9.2. | Y (l  | Luminance Signal) Processing Flow             | 67  |

| 9.2  | 2.1.  | Pre-Block Signal Processing                   | 67  |

| 9.2  | 2.2.  | Y Signal Main Process                         | 68  |

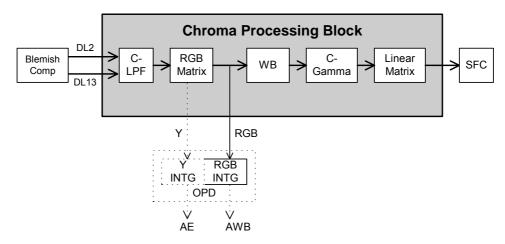

| 9.3. | Chr   | roma Signal Processing Block diagram          | 71  |

| 9.3  | 3.1.  | Block Description                             | 71  |

| 9.3  | 3.2.  | Complementary Color Pixel Clipping            | 72  |

| 9.3  | 3.3.  | Highlight Edge Color Compensation Function    | 73  |

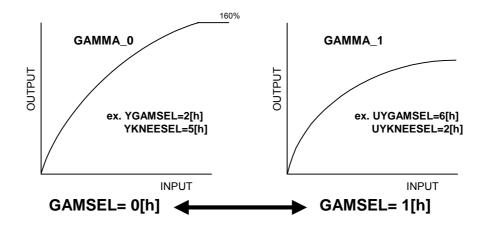

| 9.4. | Gar   | mma Function                                  | 74  |

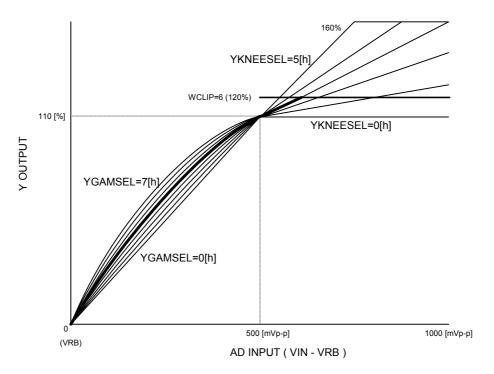

| 9.4  | 4.1.  | Gamma Knee Curve Selection                    | 74  |

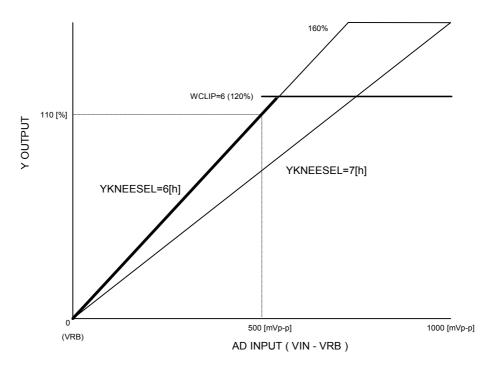

| 9.4  | 4.2.  | Y gamma Knee Curve Setting Method             | 75  |

| 9.4  | 4.3.  | Y Gamma OFF                                   | 77  |

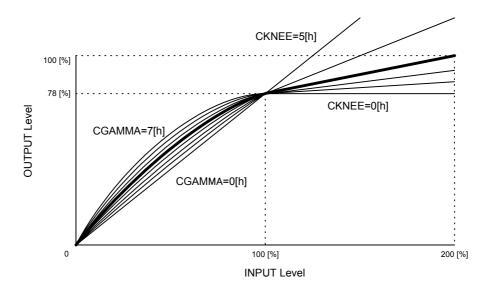

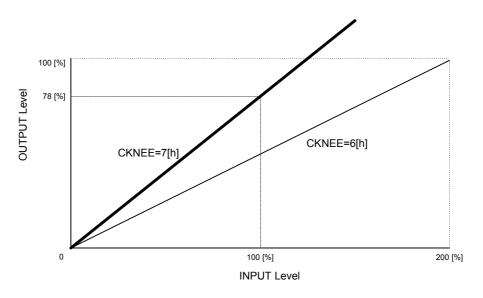

| 9.4  | 4.4.  | Chroma Gamma Knee Curve Setting Method        | 78  |

| 9.4  | 4.5.  | Chroma Gamma OFF                              | 79  |

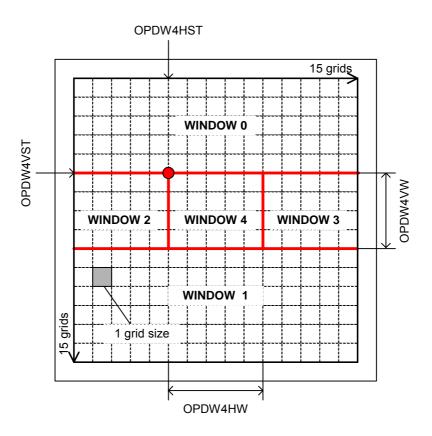

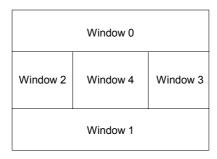

| 9.5. | OP    | D Window Setting and Display                  | 80  |

| 9.5  | 5.1.  | Detection Window Setting Method               | 80  |

| 9.5  | 5.2.  | Detection Window Screen Display               | 81  |

| 9.5  | 5.3.  | Detection Window Setting Method               | 81  |

| 9.6. | ΑE    | Operation                                     | 83  |

| 9.6  | 3.1.  | AE Modes                                      | 83  |

| 9.6  | 6.2.  | Normal AE                                     | 84  |

| 9.6  | 6.3.  | Fixed Shutter                                 | 86  |

| 9.6  | 6.4.  | Backlight Compensation                        | 88  |

| 9.6  | 6.5.  | Flickerless Function                          | 91  |

| 9.6  | 3.6.  | AE Hysteresis Function                        | 92  |

| 9.6  | 3.7.  | AE Mechanical Iris Mode                       | 93  |

| 9.6  | 3.8.  | AE Reference                                  | 95  |

| 9.6  | 3.9.  | ME Mode                                       | 96  |

| 9.6  | 3.10. | Detailed Description of AE Operation          | 97  |

| 9.7. | WB    | 3 Operation                                   | 99  |

| 9.7  | 7.1.  | WB Modes                                      | 99  |

| 9.7  | 7.2.  | ATW                                           | 99  |

| 9.7  | 7.3.  | MWB (Manual White Balance)                    | 100 |

| 9.7  | 7.4.  | Push                                          | 101 |

| 9.7  | 7.5.  | Hold                                          | 102 |

| 9.7  | 7.6.  | User Fixed Value                              | 102 |

| 9.7  | 7.7.  | Monitor Function                              | 103 |

| 9.7  | 7.8.  | ATW Related Parameters                        | 104 |

| 9.7  | 7.9.  | Convergence Point Shift                       | 110 |

| 9.7  | 7.10. | Anti Color-Rolling Mode                       |     |

| 9.7  | 7.11. | Color-rollingless AWB mode Related Parameters |     |

| 9.7  | 7.12. | Detailed Description of WB Operation          |     |

| 9.8. | Арє   | erture Correction                             | 121 |

| 9.9. | Sur   | press                                         | 123 |

| 9.9.1. Aperture Correction Suppress                           | 123 |

|---------------------------------------------------------------|-----|

| 9.9.2. Chroma Suppress                                        | 125 |

| 9.10. Using Four-Quadrant Independent Control                 | 127 |

| 9.11. False Color Suppress Function                           | 129 |

| 9.12. OUTGAIN Function                                        | 130 |

| 9.13. Mirror Function                                         | 131 |

| 9.14. Privacy Masking                                         | 132 |

| 9.14.1. Setting Procedure                                     | 132 |

| 9.14.2. Important                                             | 133 |

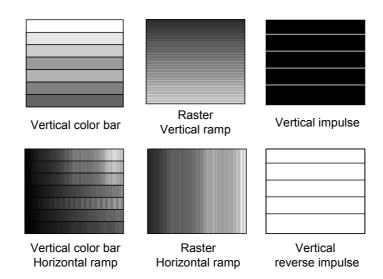

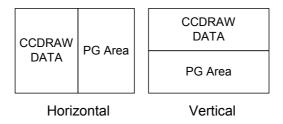

| 9.15. Pattern Generator (PG)                                  | 134 |

| 9.15.1. Pattern Generator (PG) Usage Method                   |     |

| 9.15.2. Pattern Settings                                      | 135 |

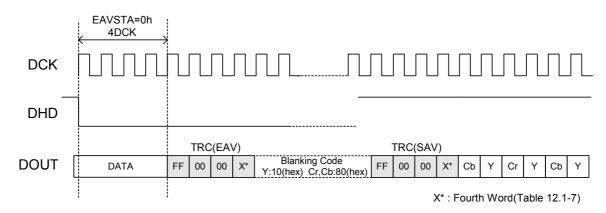

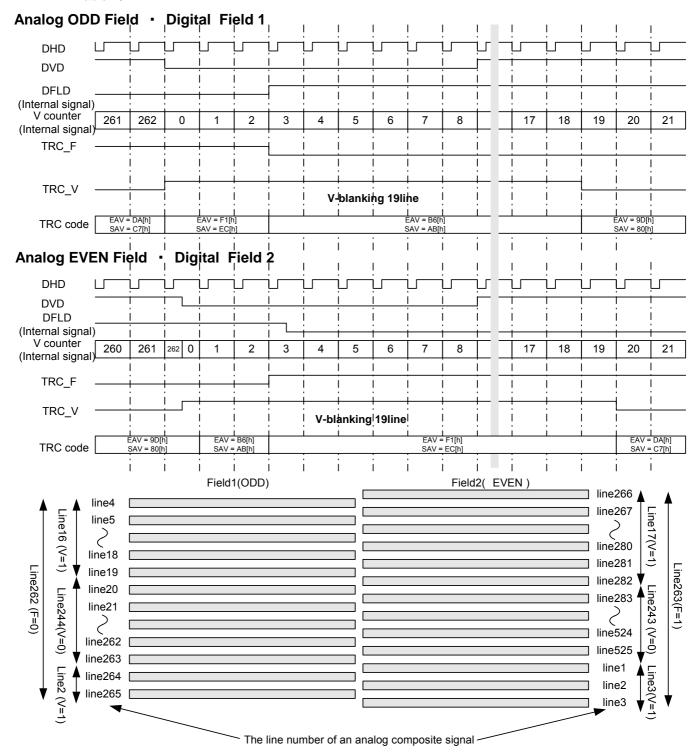

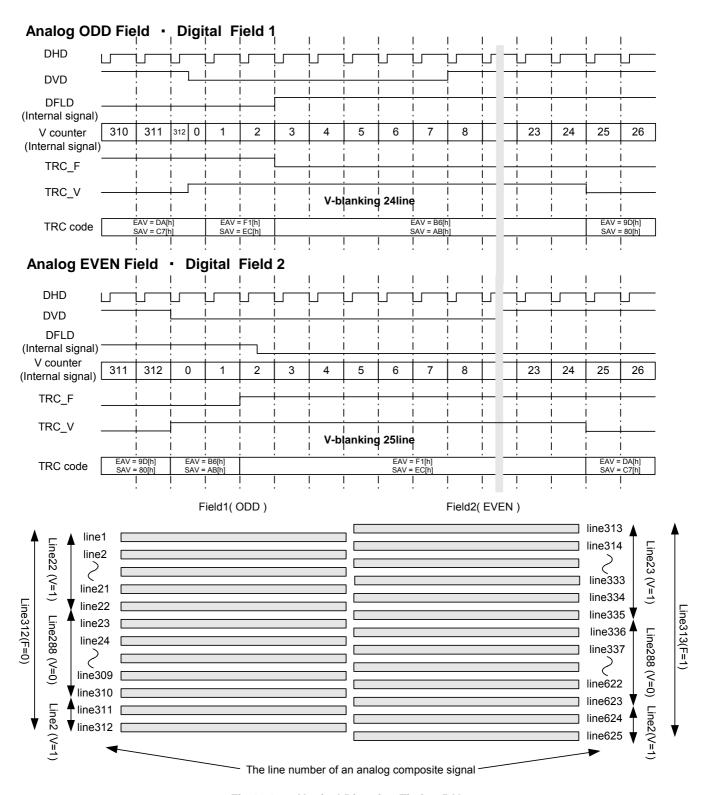

| 10. Supporting Functions for Applications (Digital Output)    |     |

| 10.1. SS-11X Digital Output                                   | 139 |

| 10.1.1. Digital Output (ITU-REC656-Compliant Output) Settings |     |

| 10.1.2. Parameters for Setting Digital Output                 | 140 |

| 10.1.3. Details of Digital Output                             | 141 |

| 10.2. Sync Signal Output Setting Method                       | 145 |

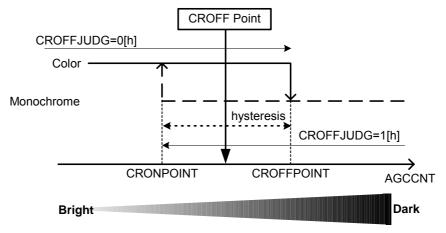

| 10.3. Color/Black-and-White Switching Function                |     |

| 10.3.1. Outline                                               | 146 |

| 10.3.2. Setting Method                                        |     |

| 10.4. When Using the External Microcomputer                   |     |

| 10.4.1. External Microcomputer-SS-11X System Interface        |     |

| 10.4.2. Communication Protocol with External Microcomputers . |     |

| 11. Appendix                                                  |     |

| 11.1. Parameters Subject to Priority1 Control                 |     |

## 1. System Outline

## 1.1. SS-11X System Outline

Table 1.1-1 SS-11X System Outline

| Features                                              | Description of functions                                       | Detailed description                                                                                                                         |  |

|-------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Supported CCDs                                        | Type 1/3, Type 1/4<br>510H, 760H<br>NTSC, PAL                  | -                                                                                                                                            |  |

| System Configuration                                  | 3-chip configuration                                           | 3-chip configuration (DSP, AFE, V-Dr)                                                                                                        |  |

| Mirror function                                       | Video right/left inversion                                     | Right/left inversion of the video signal output                                                                                              |  |

| Color-rollingless<br>mode                             | Color rolling suppression                                      | In addition to high accuracy and high-speed pull-in control, a dedicated color rolling pull-in window can be set.                            |  |

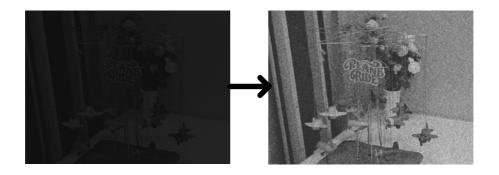

| Flickerless                                           | Flicker suppress function                                      | This function suppresses flicker by shutter fixing and AGC modulation.                                                                       |  |

| MODESEL control                                       | Automatic control of system related parameters                 | This function automatically changes parameters that are set differently for each clock system.                                               |  |

| Port driver function                                  | Easy changing of parameter setting values by external switches | This function directly operates the internal parameters from the outside using switches assigned to the DSP ports. (16 ports)                |  |

| Private masking                                       | Masking function                                               | This function hides optional locations in the video screen.  (Up to 8 masks can be output.)                                                  |  |

| Automatic blemish detection and compensation function | Pixel blemish detection and compensation                       | Automatically detects and corrects spot blemishes which are CCD pixel blemishes. (up to 8 points max.) (Static detection, Dynamic detection) |  |

| Internal A/D converter                                | 10bit A/D converter                                            | 10-bit ADC realizes high performance image reproductivity.                                                                                   |  |

| Analog output                                         | Composite video and Y/C component video both supported         | -                                                                                                                                            |  |

| Digital output                                        | Conforms to ITU-Rec.656                                        | -                                                                                                                                            |  |

| Built-in LPF                                          | Elimination of excess modulation components                    | Improved built-in LPF performance eliminates need for external LPF.                                                                          |  |

## 2. System Configuration

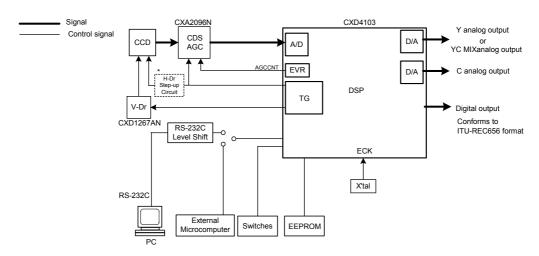

#### 2.1. Internal System

The internal system (hereafter "INT system") is the system to which external synchronization is not applied. The output configuration supports YCMIX analog output, YC separated analog output, and digital output.

\* When using a Type 1/3 CCD, an external H-Dr voltage step-up circuit is required for H1, H2 and RG clock voltage step-up (3.3 V -> 5.0 V).

Fig 2.1-1 Internal System Block Diagram

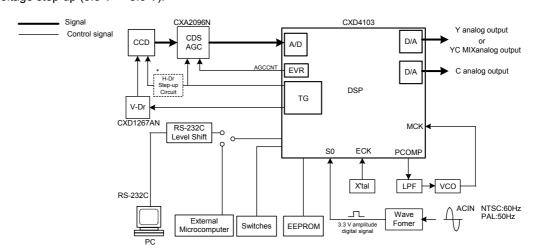

## 2.2. Line Lock System

The line lock system synchronizes the camera's vertical phase to the AC power supply. The power supply frequency is 60 Hz for NTSC and 50 Hz for PAL. The line lock system can also be used to synchronize multiple cameras and as a countermeasure against color rolling.

The output configuration supports YCMIX analog output and YC separated analog output.

\* When using a Type 1/3 CCD, an external H-Dr voltage step-up circuit is required for H1, H2 and RG clock voltage step-up (3.3 V -> 5.0 V).

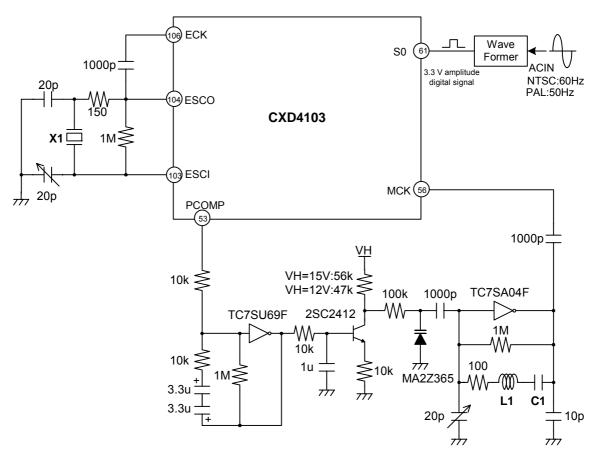

Fig 2.2-1 Line Lock System Block Diagram

The specification changed.

Please refer to "INT/LL Combined System" in "Technical Document" of the homepage for details.

## 23. Internal / Line Lock Switching System

The internal/line lock switching system (hereafter "INT/LL system") discriminates the VD input and automatically switches between the internal system and the line lock system.

The output configuration supports YCMIX analog output and YC separated analog output.

- \*1 When using a Type 1/3 CCD, an external H-Dr voltage step-up circuit is required for H1, H2 and RG clock voltage step-up (3.3 V 5.0 V).

- \*2 The MCK input clock is switched by the INT system and the LL system using the signals output from the port pins.

Fig 2.3-1 Internal / Line Lock Switching System Block Diagram

### 2.4. SS-11X System Setting Method

The setting method for each system is shown below.

See "3.3 Oscillator Circuit Periphery" under "3 Peripheral Circuits" for the circuits composition each system.

#### 2.4.1. Internal System Settings

The setting procedure is as follows.

- 1. Select the crystal used for ECK input according to the TV system and the CCD type. (See "Table 2.4-1".)

- 2. Set the MODESEL value according to the crystal selected in step 1. (See"Table 2.4-1".)

- 3. Set SGMODE to 0[h]. (Selects INT mode.) (See "Table 2.4-2".)

Table 2.4-1 INT System Crystal and MODESEL Selection

| TVsystem | Number of Pixels | MODESEL | X'tal(ECK)  |

|----------|------------------|---------|-------------|

| NTSC     | 510H             | 0[h]    | 38.13986MHz |

| NISC     | 760H             | 6[h]    | 28.63636MHz |

| PAI      | 510H             | 3[h]    | 37.87500MHz |

| FAL      | 760H             | 9[h]    | 28.37500MHz |

Table 2.4-2 INT / LL Switching Parameter

|        | Parameter         | Description                                       |

|--------|-------------------|---------------------------------------------------|

| SGMODE | CAT17_Byte17_bit1 | 0[h] : Internal system<br>1[h] : Line lock system |

<sup>\*</sup> When the video cannot be synchronized, check the following items.

- · Check again that the settings were made according to the procedure above.

- · Check that the MODESEL value matches the TV standard and CCD type.

- The combination of MODESEL and the crystal used for ECK input may not be appropriate, so recheck this combination.

- · Check that the ECK frequency is appropriate.

#### 2.4.2. Line Lock System Settings

The setting procedure is as follows.

- 1. Set the crystal used for ECK input to 27.00000 MHz.

- 2. Set the MODESEL value according to the TV system and the CCD type. (See "Table 2.4-3".)

- 3. Input a 3.3 V rectangular wave to the S0 pin. (This 3.3 V rectangular wave is obtained by converting the AC power supply using a WAVE FORMER.)

- (The 3.3 V rectangular wave frequency is 60 Hz for NTSC or 50 Hz for PAL.)

- 4. Configure the LPF and VCO (LC) for the external PLL according to the CCD type. (See "3.3.2 Line Lock System ".)

- 5. Set SGMODE to 1[h]. (Selects line lock system.) (See "Table 2.4-2".)

- 6. Adjust the VCO (LC) frequency to lock the PLL. (See "Line Lock System PLL".)

Table 2.4-3 LL System Crystal and MODESEL Selection Table

| TV<br>system | Number of Pixels | MODESEL | X'tal(ECK)    |

|--------------|------------------|---------|---------------|

| NTSC         | 510H             | 2[h]    |               |

| NISC         | 760H             | 8[h]    | 27.00000MHz   |

| PAL          | 510H             | 5[h]    | 27.00000IVIH2 |

| FAL          | 760H             | B[h]    |               |

<sup>\*</sup> When the video cannot be synchronized, check the following items.

- Check again that the settings were made according to the procedure above.

- · Check that the MODESEL value matches the TV standard and CCD type.

- · Check that the ECK frequency is appropriate.

- Check that the S0 pin input frequency is 60 Hz for NTSC or 50 Hz for PAL.

- Check the VCO and LPF circuit constants. For details, see "3.3.2 Line Lock System".

- · Adjust the VCO frequency and check that the PLL locks.

<sup>\*</sup> In the line lock system, the sub-carrier does not lock.

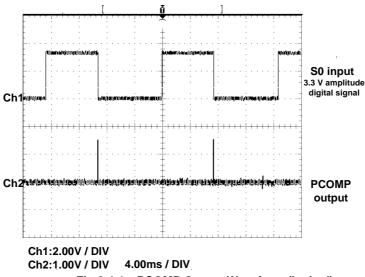

#### **Line Lock System PLL**

In the line lock system, the CXD4103 internally compares the phases of the external power supply rectangular wave signal (S0 input) and the VD (MCK-VD) signal obtained by frequency-dividing MCK. These phase comparison results are output through PCOMP. The V direction PLL is configured by applying the PCOMP signal to an external LPF (for the V-PLL) and then feeding it back to VCO circuit in the MCK side.

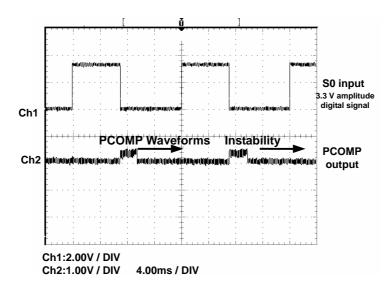

"Fig 2.4-1" shows the PCOMP output waveform when a lock is applied, and "Fig 2.4-2" shows the PCOMP output waveform without a lock. Apply a trigger to the external power supply rectangular wave signal (S0 input) using an oscilloscope and adjust the VCO frequency while checking the PCOMP output waveform so that a lock is applied as shown in "Fig 2.4-1".

Fig 2.4-1 PCOMP Output Waveform (locked)

Fig 2.4-2 PCOMP Output Waveform (unlocked)

- \* The PCOMP signal polarity can be switched by PCMPINV (CAT7\_Byte2\_bit4).

- \* The PCOMP signal polarity can be switched by PCMPINV (CAT7\_Byte2\_bit4).

- \* Either active filtering or passive filtering can be selected for the external PLL LPF, but active filtering is recommended since it provides higher performance. (See "3.3.1 Internal System".)

#### **Line Lock System Phase Adjustment**

In the line lock system, the vertical phase can be adjusted by the shift function.

See "9.1 Port Driver Function" for a description of the shift function setting and operation methods.

#### **Parameters Affected by the Shift Function**

The parameter values shown in "**Table 2.4-4**" are changed by the shift function when the line lock system phase is adjusted.

Table 2.4-4 Parameters Affected by the Shift Function

| Р                     | arameter           | Description                           |

|-----------------------|--------------------|---------------------------------------|

| CTRLSFTVL CAT17_Byte3 |                    | Vertical phase adjustment value (LSB) |

| CTRLSFTVM             | CAT17_Byte4_bit0-1 | Vertical phase adjustment value (MSB) |

#### **Phase Adjustment Parameters when Preset**

When the shift function is preset, the parameter setting values in "Table 2.4-5" are reflected.

Table 2.4-5 Phase Adjustment Parameters when Preset

| P         | arameter            | Description                          |

|-----------|---------------------|--------------------------------------|

| PRSTSFTVL | CAT17_Byte15        | SFTV setting value (LSB) when preset |

| PRSTSFTVM | CAT17_Byte16_bit0-1 | SFTV setting value (MSB) when preset |

#### The specification changed.

Please refer to "INT/LL Combined System" in "Technical Document" of the homepage for details.

#### 2.4. Internal / Line Lock Switching System Settings

The setting procedure is as follows.

- 1. Set the crystal used for ECK input to 27.00000 MHz.

- 2. Set the crystal for INT MCK input according to the TV system and the CCD type. (See "Type 2.4-6".)

- 3. Configure the external LPF and VCO (LC) for LL according to the CCD type. (See "3.3.3 Internal/Line Lock Switching System ".)

- 4. Set the MONESEL value according to the crystal selected in step 2. (See "Table 2.46".)

- 5. Assign the HVPLL parameter to the port driver (See Pn in "Fig 2.3-1"). See "9.1 Port Driver Function" for a description of the setting method.

- 6. Set ATMODEON 1[h]. (Auto mode ON) (See "Table 2.4-7".)

- 7. The system switch is to the line lock system when the 3.3 V rectangular wave obtained by passing the AC power supply through a WAVE FORMER is input to the S0 pin. When there is no input, the system operates as the internal system.

- (The 3.3 V rectangular wave frequency is 60 Hz for NTSC or 50 Hz for PAL.)

8. In line lock system mode, adjust the VCO to lock the PLL. (See "Line Lock System PLL".)

9. In internal system mode, adjust the VCXO to lock the PLL. (See "Internal/Line Lock Switching System (Internal System Mode) PLL".)

Table 2.4-6 INT/LL Switching System Crystal and MODESEL Selection

| TV<br>syste | n | Number of Pixels | MODESEL | X'tal(/ZCK)    | X'tal(MCK)  |

|-------------|---|------------------|---------|----------------|-------------|

| NTC         |   | 510H             | 2[h]    |                | 38.13986MHz |

| NTSC        | , | 760H             | 8[h]    | 21.00000MHz    | 28.63636MHz |

| PAL         |   | 510H             | 5[h]    | 27.00000IVITI2 | 37.87500MHz |

| PAL         |   | 760H             | B[h]    |                | 28.37500MHz |

Table 2.4-7 INT/LL Switching System Setting Parameters

| Pa       | arameter   |         | Description                                     |

|----------|------------|---------|-------------------------------------------------|

| ATMODEON | CAT17_Byte |         | 0[h]; Auto mode OFF<br>1[h]: Auto mode ON       |

| HVPLL    | CAT7_Byte  | e1_bit1 | 0[h]: Internal system<br>1[h]: Lina lock system |

<sup>\*</sup> When the video cannot be synchronized, check the following item

[When synchronization cannot be achieved in internal mode]

- Check again that the settings were made according to the procedure above.

- Check that the MODESE value matches the TV standard and CCD type

- Check the VCO and Lef circuit constants. See "3.3 Oscillator Circuit Perphery" for details.

- The combination of MODESEL and the crystal used for MCK input may not be appropriate, so recheck this combination.

- Adjust the VCX frequency and check that the PLL locks.

[When synchrodization cannot be achieved in line lock mode]

- Check again that the settings were made according to the procedure above.

- Check that the MODESEL value matches the TV standard and CCD type.

- · Check the VCO and LPF circuit constants. See "3.3 Oscillator Circuit Periphery" for detail

- Check that the S0 pin input frequency is 60 Hz for NTSC or 50 Hz for PAL.

- djust the VCO frequency and check that the PLL locks.

- ne sub-carrier does not lock in the INT/LL switching system.

The specification changed.

Please refer to "INT/LL Combined System" in "Technical Document" of the homepage for details.

#### Internal/Line Lock Switching System (Internal System Mode) PLL

When the INT/LL switching system is set to INT, the CXD4103 internally compares the phases of the ECK-HD signal obtained by frequency-dividing the ECK clock and the MCK-HD signal obtained by frequency-dividing MCK. These phase comparison results are output through PCOMP. Apply the PCOMP signal to the LPP (for H-PLL) and feed it back to the MCK side VCXO.

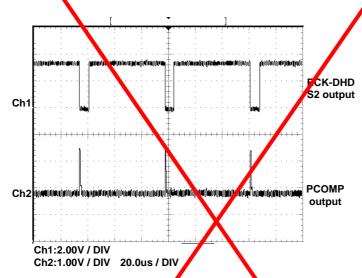

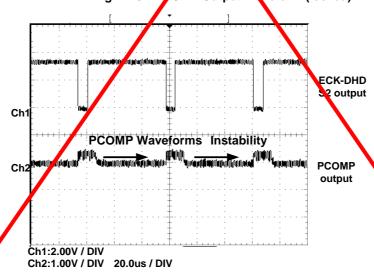

"Fig 2.4-3" shows the PCOMP output waveform when a lock is applied, and "Fig 2.44" shows the PCOMP output waveform whout a lock. Apply a trigger to the ECK-HD output from S2 using an oscilloscope and adjust the VCXO frequency while viewing the PCOMP output waveform so that a lock is applied as shown in "Fig 2.4-3".

Fig 2.4-3 PCOMP Output Waveform (locked)

Fig 2.4-4 PCOMP Output Waveform (unlocked)

\* The PCOMP signal polarity can be switched by PCMPINV (CAT7 Byte2 bit4).

\* Either active filtering or passive filtering can be selected for the external PLL LPF, but active filtering is recommended since it provides higher performance. (See "3.3.3 Internal/Line Lock Switching System".)

## 2.5. ICs Comprising the System

The SS-11X is a digital signal processing system for single-panel CCD color cameras, and is comprised of the following three main LSIs.

Table 2.5-1 Main LSIs

| Main LSIs | Type name | Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Package         |

|-----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| DSP       | CXD4103   | -Luminance signal and chroma signal processing -Built-in digital encoder -Built-in microcontroller with AE/AWB -Built-in AE/AWB integral circuit -Built-in external synchronization function -Built-in 10-bit A/D converter -Built-in 10-bit D/A converter (Y/C 2ch) -Built-in phase comparator -Built-in EVR 3ch -Built-in timing generator -Built-in serial communication circuit that supports RS-232C and microcomputer communication -Built-in ITU REC656 conformity digital output function | LQFP<br>120 pin |

| CDS/AGC   | CXA2096N  | Built-in correlated double sampling (CDS) circuit Built-in AGC circuit Built-in interface circuit for A/D converter                                                                                                                                                                                                                                                                                                                                                                               | SSOP<br>24 pin  |

| V-Dr      | CXD1267AN | Built-in CCD vertical clock driver     Built-in shutter pulse driver                                                                                                                                                                                                                                                                                                                                                                                                                              | SSOP<br>20 pin  |

For details, see the product specifications of each LSI.

The peripheral ICs shown in "Table 2.5-2" are needed to configure the system in addition to the above-mentioned 3 LSIs.

Table 2.5-2 Peripheral ICs

| Recommended peripheral IC | Type name (Manufacturer)                                        | Description and applications                                                                                   |

|---------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| EEPROM                    | AK6480A<br>(Asahi Kasei Microsystems)<br>or<br>BR9080<br>(ROHM) | 8k-bit EEPROM (Note that other substitutions are not possible due to limitations in the communication format.) |

| RS-232C<br>Transceiver    | MAX3232 (or equivalent) (Maxim Integrated Products, Inc.)       | PC control I/F                                                                                                 |

| System Reset              | PST9127 (or equivalent)<br>(MITSUMI ELECTRIC CO., LTD.)         | Vth 2.7 V                                                                                                      |

## 3. Peripheral Circuits

## 3.1. Initially Occupied Terminals

#### 3.1.1. If No Valid Data in EEPROM

If no EEPROM is connected or there is no valid data in the EEPROM, data is read from the internal memory of the CXD4103.

At this time parameters are assigned from CXD4103 internal memory for the terminals indicated in the following table (the port driver). Thus, setup does not apply user-designated settings.

Table 3.1-1 Initially Occupied Terminals

| Pin Name | Pin No | Parameter Name | Description                                            |

|----------|--------|----------------|--------------------------------------------------------|

| P0       | 109    |                |                                                        |

| P1       | 110    | AWBMODE        | AWB operation mode switching                           |

| P2       | 111    |                |                                                        |

| P3       | 112    | CRLESSON       | Switches anti-color rolling mode ON and OFF            |

| P4       | 116    | BLCOFF         | Switches backlight compensation ON and OFF             |

| P5       | 117    | AEREF          | Switches AE reference ON and OFF                       |

| P6       | 118    | NORMFLC        | Switches the flickerless function ON and OFF           |

| P7       | 119    | AGCMAX         | Switches the AGC maximum value ON and OFF              |

| P8       | 91     | AEME           | Switches between AE and ME                             |

| P9       | 92     | AESHUT         | Switches the electronic shutter fixed speed ON and OFF |

| P10      | 93     | MIRROR         | Switches MIRROR function ON and OFF                    |

| P11      | 94     | GAMSEL         | Switches the gamma parameters                          |

| P12      | 97     |                |                                                        |

| P13      | 98     | MODESEL        | DSP operation mode switching                           |

| P14      | 99     | MODESEL        | DOF operation mode switching                           |

| P15      | 100    |                |                                                        |

#### 3.1.2. Port Driver pin Specification

During reset (XRST = L), the port driver pins (P0 - P7) become output pins. Please note that when using thise pins (P0 - P7) their value is unknown during the reset period.

Use of the port driver pins as INPUT requires a pull-up resistor.

Table 3.1-2 Port Driver pin Specification

|          | During reset(XRST=L) | Outside reset(XRST=H) |

|----------|----------------------|-----------------------|

| P0 – P7  | OUTPUT (Unspecified) | INPUT                 |

| P8 – P15 | INPUT                | INPUT                 |

## 3.2. Processing of Empty Pins

#### 3.2.1. Processing of Empty Pins in case DAC is not used

When DAC are not used by YCMIX output (DACMODE=0[h]), digital output, etc. perform pin processing for the CXD4013 as follows.

Table 3.2-1 Processing of Empty Pins in case DAC is not used

| Pin Name | Pin No | Digital<br>output | YCMIX<br>output |

|----------|--------|-------------------|-----------------|

| IOC      | 81     | 3.3V              |                 |

| VREFC    | 82     | CND               |                 |

| IREFC    | 85     | GND               |                 |

| IOY      | 90     | 3.3V              | -               |

| VREFY    | 89     | GND -             |                 |

| IREFY    | 86     | GIND              | -               |

#### 3.2.2. Processing of Empty Pins in case Internal EVR is not used

When Internal EVR is not used, perform pin processing for the CXD4103 as follows.

However, supply power to the power supply pin AVD even when there are channels that do not use the internal EVR.

Table 3.2-2 Processing of Empty Pins in case Internal EVR is not used

|   | Pin Name | Pin No | When Internal EVR is not used              |

|---|----------|--------|--------------------------------------------|

|   | EVR0     | 74     |                                            |

|   | EVR1     | 76     | Connects with GND through 0.1µF capacitor. |

| Ì | EVR2     | 77     |                                            |

See the Application Circuit of each system for the processing of other open pins.

## 3.3. Oscillator Circuit Periphery

In the SS-11X, the oscillator circuit configuration differs for the internal system, the line lock system, and the internal/line lock switching system. The circuit configurations for each oscillator circuit periphery are shown below. Select the configuration to match the system used.

The circuit constants are scheduled to be verified in operation using a Sony evaluation board equipped with the crystal oscillator shown in "**Table 3.3-2**". No guarantee of performance is implied for different board layouts, component selection, or temperature characteristics.

| Component name     | Manufacturer                | Model     | Frequency   | Load capacitance |  |  |             |  |

|--------------------|-----------------------------|-----------|-------------|------------------|--|--|-------------|--|

| Crystal oscillator |                             |           | 28.63636MHz |                  |  |  |             |  |

|                    | RIVER ELETEC<br>CORPORATION |           | 28.37500MHz |                  |  |  |             |  |

|                    |                             | HC-49/U03 | 38.13986MHz | 12pF             |  |  |             |  |

|                    |                             |           |             |                  |  |  | 37.87500MHz |  |

|                    |                             |           | 27.00000MHz |                  |  |  |             |  |

Table 3.3-1 Crystal Oscillator Used on the Evaluation Board

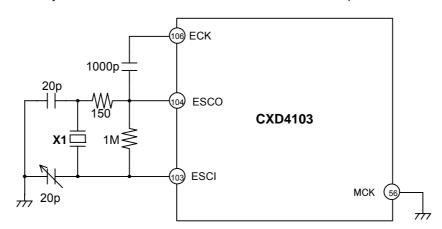

#### 3.3.1. Internal System

The internal system can operate by connecting only a single clock (crystal).

The frequency of the crystal oscillator connected to the ECK pin of the CXD4103 differs according to the CCD type and the TV system. "Table 3.3-2" shows the connected oscillator frequencies.

Fig 3.3-1 Example Internal System Oscillator Circuit

Number of Pixels

TV system

X1

510H

NTSC

38.13986MHz

PAL

37.87500MHz

NTSC

28.63636MHz

PAL

28.37500MHz

Table 3.3-2 Crystal Oscillator Frequency

#### 3.3.2. Line Lock System

The line lock system is a 2-clock system that inputs different frequencies to the ECK pin and the MCK pin. Input a crystal oscillated clock to the ECK pin, and a LC (VCO) oscillated clock to the MCK pin. Use a crystal oscillator frequency of 27.00000 MHz. The LC (VCO) constant differs according to the CCD type. See "**Table 3.3-3**".

Fig 3.3-2 Example Line Lock System Oscillator Circuit

Table 3.3-3 Crystal Oscillator Frequency and LC Oscillator Circuit Constants

| Number of<br>Pixels | TV system | X1           | L1    | C1   |

|---------------------|-----------|--------------|-------|------|

| 510H                | NTSC      |              | 1.5uH | 18pF |

| 31011               | PAL       | 27.00000MHz  |       |      |

| 760H                | NTSC      | 27.00000WIHZ | 3.3uH | 12pF |

| 76011               | PAL       |              | J.Jun | 1200 |

<sup>\*</sup> See the "WAVE FORMER Application Circuit" for the WAVE FORMER.

#### The specification changed.

Please refer to "INT/LL Combined System" in "Technical Document" of the homepage for details.

#### 3.3.3. Internal/Line Lock Switching System

The internal/line lock switching system is a 2-clock system that inputs different frequencies to the ECK pin and the MCK pin, and switches the MCK input clock in internal mode and line lock mode.

Pn (port driver pin) outputs low in internal system mode, and high in line lock system mode. The MCK input clock is switched between crystal oscillation and LC oscillation using this signal.

Use 27.00000 MHz as the crystal oscillator frequency input to ECK. The crystal oscillator frequency input to MCK and the LC (VCO) constant differ according to the CCD type. See "**Table 3.3-4**".

\*Please substitute 88 to P15 for Pn\*. Refer to "3.1.2 Port Driver pin Specification" or more information.

Fig 3.3-3 Internal/Line Lock Switching System Oscillator Circuit

\* See the "WAVE FORMER Application Circuit" for the WAVE TORMER.

Table 3.6-4 Crystal Oscillator Frequency and LC Oscillator Circuit Constant

| N    | Numbe, of<br>Pix Is | TV system   | X1          | X2          | L1    | C1   |

|------|---------------------|-------------|-------------|-------------|-------|------|

|      | 510H                | NTSC        |             | 38.13986MHz | 1.5uH | 8pF  |

| STUH | PAL                 | 27.00000MHz | 37.87500MHz | 1.5un       | oht   |      |

|      | 760H                | NTSC        | 27.00000WHZ | 28.63636MHz | 3.3uH | 12pF |

|      |                     | PAL         |             | 28.37500MHz |       | тгрг |

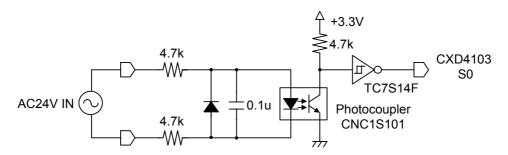

#### **WAVE FORMER Application Circuit**

The application circuit for the external rectangular wave pulse shaping circuit (WAVE FORMER) needed to configure the line lock system and the internal/line lock switching system is shown below.

Fig 3.3-4 WAVE FORMER

### 3.4. Output Circuit Periphery

The SS-11X supports analog output (YCMIX output, YC separated output) and digital output. The peripheral circuits for each output configuration are shown below.

The circuit constants are scheduled to be verified in operation using a Sony evaluation board. No guarantee of performance is implied for different board layouts, component selection, or temperature characteristics.

#### 3.4.1. Analog Output (YCMIX Output, YC Separated Output)

The analog signal output system can be selected from YCMIX output and YC separated output by the parameter in "**Table 3.4-1**". Select the parameter setting that matches the circuit configuration.

Parameter

Setting value

Description

DACMODE

CAT1\_Byte3\_bit2

0[h]

YCMIX output

1[h]

YC separated output

Table 3.4-1 DAC Mode Selection Method

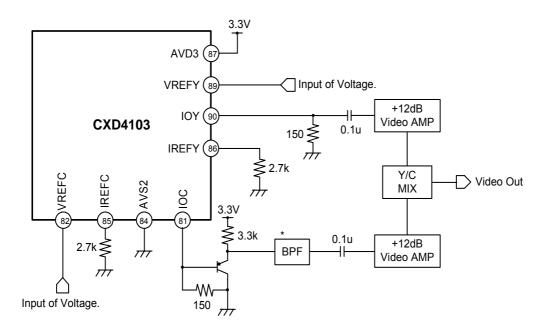

#### Circuit Configuration during YC Separated Output (DACMODE = 1[h])

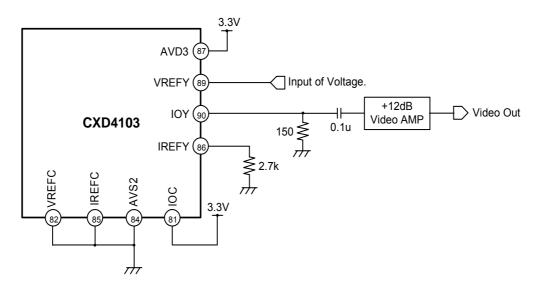

During YC separated output, the Y and C signals from the CXD4103 internal DAC are output from the IOY pin and the IOC pin, respectively." **Fig 3.4-1**" shows the circuit example during YC separated output.

The signal level output from the IOY and IOC pins is decided depending on the voltage input to the VREFY and VREFC pins. So input the desired voltage value and adjust the level. The voltage value is input and adjusted so that Sync and Burst may become prescribed signal levels because of the following Video output of Video AMP of latter part.

When AMP of +12dB is connected like "Fig 3.4-1", the input voltage to the VREFY and VREFC pins becomes about 1 to 1.1V (As for the input voltage value, it is scheduled to evaluate it in the future). The input voltage is 1.1V (typ) in the CXD4103 internal DAC specifications. So use a configuration with an amplification circuit (Video AMP of +12dB) in the final stage. Do not use Video AMP other than +12dB. Note that the operation in that case cannot be guaranteed because the VREF input voltage might become outside the specification range of the CXD4103 internal DAC.

Fig 3.4-1 Example Circuit During YC Separated Output

<sup>\*</sup> See "3.4.3BPF Circuit Example" for a description of the BPF.

#### Circuit Configuration during YCMIX Output (DACMODE = 0[h])

During YCMIX output, the Y and C signals are mixed inside the CXD4103 and output from the IOY pin. The IOC pin is not used at this time. "Fig 3.4-2"shows the circuit example during YCMIX output.

The BPF is not connected during YCMIX output, so note that the digital component of the sub-carrier signal cannot be completely eliminated. The signal level output from the IOY pin is decided depending on the voltage input to the VREFY pin. So input the desired voltage value and adjust the level. The voltage value is input and adjusted so that Sync and Burst may become prescribed signal levels because of the following Video output of Video AMP of latter part.

When AMP of +12dB is connected like "Fig 3.4-2", the input voltage to the VREFY pin becomes about 1 to 1.1V (As for the input voltage value, it is scheduled to evaluate it in the future). The input voltage is 1.1V (typ) in the CXD4103 internal DAC specifications. So use a configuration with an amplification circuit (Video AMP of +12dB) in the final stage. Do not use Video AMP other than +12dB. Note that the operation in that case cannot be guaranteed because the VREF input voltage might become outside the specification range of the CXD4103 internal DAC.

Fig 3.4-2 Example Circuit During YCMIX Output

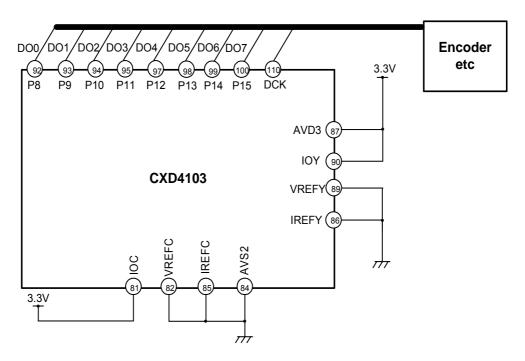

#### 3.4.2. Digital Output

Digital output can be used by the internal system. See "10.1.2 Parameters for Setting Digital Output" for the parameter setting method. Note that analog output is also possible when performing digital output in the internal system.

The circuit configuration below shows the case when using only the digital output.

Fig 3.4-3 Example Circuit During Digital Output (when not using analog output)

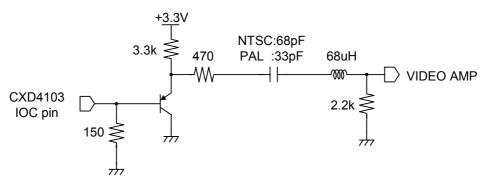

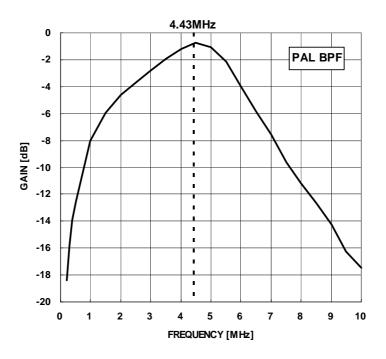

#### 3.4.3. BPF Circuit Example

When outputting an analog chroma signal from the IOC pin, add a band pass filter circuit to ensure that signal components other than the sub-carrier component are eliminated. This filter also shapes the sub-carrier signal, in which digital components remain, into a sine wave. An example of BPF Circuit is shown in "Fig 3.4-4".

Fig 3.4-4 Example BPF Circuit

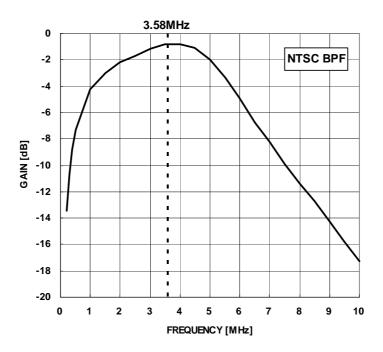

#### **Example BPF Characteristics**

The following graph shows example characteristics measured using the BPF formed in "Fig 3.4-4".

Fig 3.4-5 Example BPF Frequency Characteristics (NTSC)

Fig 3.4-6 Example BPF Frequency Characteristics (PAL)

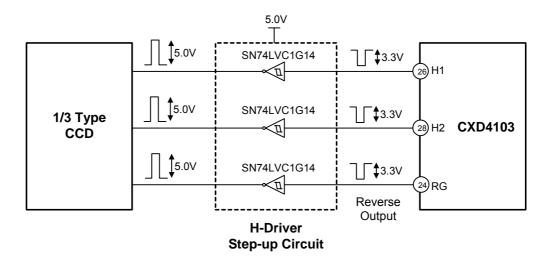

## 3.5. H-Driver Voltage Step-up Circuit

When using a Type 1/3 CCD with the SS-11X, the H1, H2 and RG clocks must be converted from 3.3 V -> 5 V.

"Fig 3.5-1" shows the circuit configuration. Each specification of the following product (SN74LVC1G14 made by TI) or the H level input voltage to power-supply voltage (5.0V), the response speed, and the drive ability must use equal to the following product goods for the pressure circuit.

In this example of the circuit, the H1, H2, and RG clocks are reversed from CXD4103 and it outputs it. Normal rotation/reversing clocks can be switched according to the parameter. (See "**Table 3.5-1**".)

Fig 3.5-1 H-Driver Voltage Step-up Circuit Block Diagram

Parameter Description 0[h]: Normal H1INV CAT6 Byte19 bit0 Reverse Control of H1 clock. 1[h]: Reverse 0[h] : Normal H2INV CAT6\_Byte19\_bit1 Reverse Control of H2 clock. 1[h]: Reverse 0[h] : Normal Reverse Control of RG clock. **RGINV** CAT6 Byte19 bit2 1[h]: Reverse

**Table 3.5-1 Clocks Reversed Parameters**

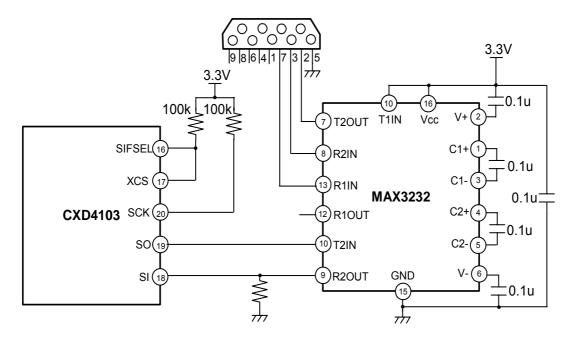

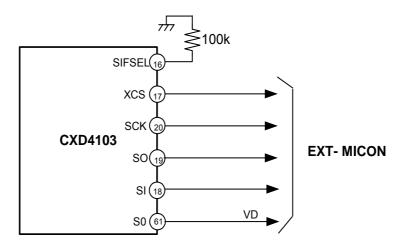

#### 3.6. Communication Circuit

In SS-11X, the parameter is set according to the RS-232C communication and external microcomputer communication. "Fig 3.6-1" and "Fig 3.6-2" show the peripheral circuits for each type of communication.

#### 3.6.1. RS-232C Communication

Fig 3.6-1 Example RS-232C Communication Circuit

#### 3.6.2. External Microcomputer Communication

Fig 3.6-2 Example External Microcomputer Communication Circuit

#### 3.7. Reset Circuit

#### 3.7.1. Outline

This circuit performs system reset to enable stable operation when the CXD4103 and peripheral ICs start up after power is supplied. However, problems may also be caused by a transient power supply.

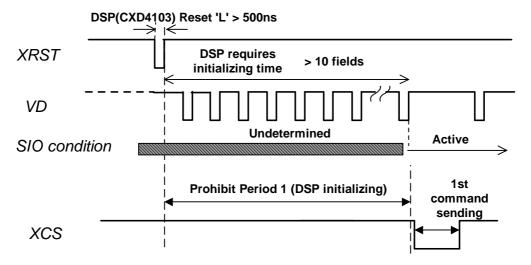

For a reliable way to avoid such problems, add a circuit that meets the following conditions (Timing chart). The only IC used by the SS-11X system that requires reset is the CXD4103.

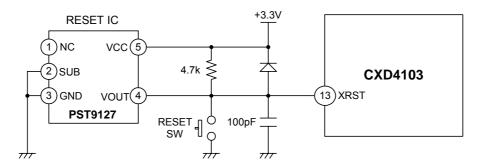

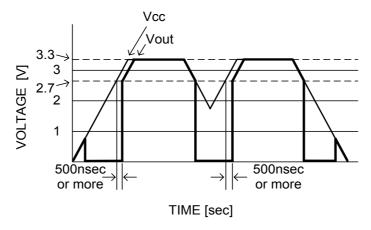

#### 3.7.2. Example Reset Circuit and Timing Chart

The sample reset circuit is shown in "Fig 3.7-1".

Fig 3.7-1 Example Reset Circuit

If the 3.3V voltage supply surges to exceed 2.7V after power is supplied or other events, set the CXD4103 XRST terminal to Low (at least 500ns) and be sure to reset it. Additionally, if the 3.3V power supply falls under 2.7V, set the XRST terminal to Low and be sure to reset it.

\* The guaranteed voltage for DSP operation is 3.0 to 3.6V. For details refer to the product specifications.

Fig 3.7-2 Timing Chart

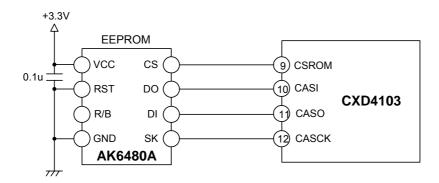

#### 3.8. EEPROM Connection

#### 3.8.1. Outline

The SS-11X can connect an EEPROM for data storage. The AK6480A made by Asahi Kasei Microsystems or the BR9080 made by ROHM are recommended as the EEPROM due to limitations in the communication format.

#### 3.8.2. Connection Method

When connecting the CXD4103 and the EEPROM, make the pin connections as shown in "Fig 3.8-1".

Fig 3.8-1 EEPROM Connections

#### 3.9. Internal EVR

#### 3.9.1. Outline

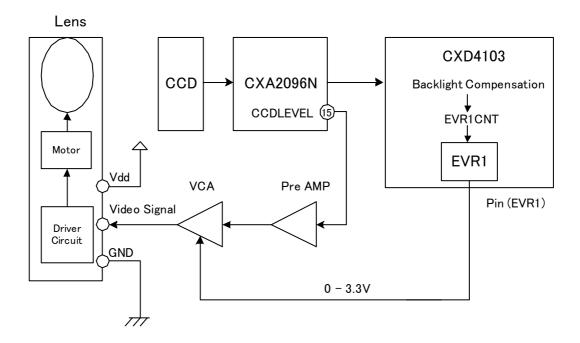

The CXD4103 has a built-in 3-channel, 8-bit D/A converter (EVR), and can output nearly linear voltage from approximately 0 V to 3.3 V.

#### 3.9.2. Internal EVR Initial Settings

The internal EVR initial settings are as shown in "Table 3.9-1".

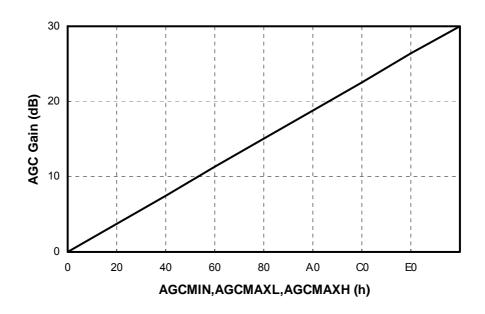

The CXD4103 performs AGC gain control for the CXA2096N, so EVR0 should be connected to AGCCNT (Pin 14) of the CXA2096N.

The 2 channels of EVR1 and EVR2 can be set optionally by the user.

Table 3.9-1 Internal EVR Initial Settings

| ch   | Parameter |            | Control details  |

|------|-----------|------------|------------------|

| EVR0 | AGCCNT    | CAT8_Byte3 | AGC gain control |

| EVR1 | EVR1CNT   | CAT8_Byte4 | User setting     |

| EVR2 | EVR2CNT   | CAT8_Byte5 | User setting     |

#### 3.9.3. Internal EVR User Setting Method

When using EVR0 with a user setting, AE control must be stopped. Make the parameter setting shown in "Table 3.9-2", then set AGCCNT to an optional value.

Mechanical iris control can also be performed by the CXD4103. (For details, see "9.6.7 AE Mechanical Iris Mode".) However, when using EVR1 with a user setting, make the parameter setting shown in "Table 3.9-2" in the same manner as for EVR0, then set EVR1CNT to an optional value.

EVR2 can be used with a user setting by setting an optional value in EVR2CNT, even if other parameters are not set.

Table 3.9-2 Parameters of Note when Using the Internal EVR with User Settings

| ch   | Parameter |                    | Setting value                     |

|------|-----------|--------------------|-----------------------------------|

| EVR0 | AEHOLD    | CAT12_Byte5_bit2   | 1[h]:AE HOLD                      |

| EVR1 | MIRIS     | CAT14_Byte1_bit1   | 0[h]: Mechanical iris control OFF |

| EVR2 |           | Other parameter se | ttings are not required.          |

When not using the internal EVR, set the parameters for each channel to optional values or set each channel to standby as shown in "Table 3.9-3". When set to standby, the status of each channel is undetermined.

Table 3.9-3 When not Using the Internal EVR

| ch   | F       | Parameter       | Setting value                          |

|------|---------|-----------------|----------------------------------------|

| EVR0 | EVR0STB | CAT8_Byte2_bit5 | 011 5 15                               |

| EVR1 | EVR1STB | CAT8_Byte2_bit6 | 0[h]: EVR control<br>1[h]: EVR standby |

| EVR2 | EVR2STB | CAT8_Byte2_bit7 | This Evit stands                       |

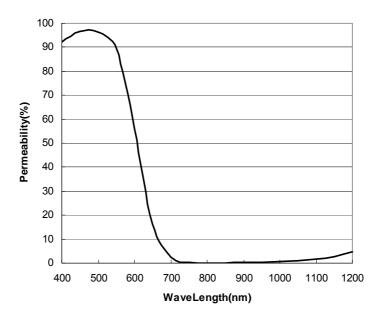

## 3.10. Optical Filters

#### 3.10.1. Outline

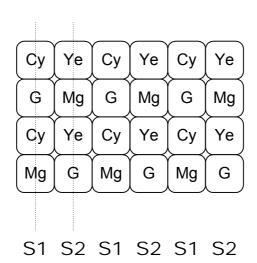

When a subject with a high spatial frequency is shot using a color camera containing CCDs, a moire effect (false signal) occurs. In order to suppress this moire effect (false signal), always use an optical low pass filter (optical LPF) which matches the type of CCD being used.

Sony uses optical LPF with a three-layer configuration for all function and performance evaluations. Note that Sony does not support two-layer configurations or optical LPF lacking an IR cut filter.

"Fig 3.10-1" shows example spectral characteristics of optical filter used by Sony, and "Fig 3.10-2" shows the pixel separation pattern (8 points) specification using optical LPF for your reference.

Fig 3.10-1 Example Spectral Characteristics of Sony Optical Filter

Fig 3.10-2 Pixel Separation Pattern (8 Points) Specification Using Optical LPF

## 4. Parameter Control Priority Ranking

## 4.1. Parameter Priority Ranking

In the SS-11X, the priority ranking in which parameter values are reflected differs according to the category. This priority ranking is as follows.

#### (PORT Driver) > Priority1 > Priority2

- < Details >

- 1. When set by the port driver, changes to the Priority1 and Priority2 parameters are ignored.

- 2. Priority1 changes have priority for parameters that are subject to both Priority1 and Priority2 control. (See "11.1 Parameters Subject to Priority1 Control" for a list of parameters subject to Priority1 control.)

#### 4.1.1. Communication Categories

Table 4.1-1 Priority1 Communication Category Table

| Control subject | Category<br>number | Category name | Description                                            |  |  |  |

|-----------------|--------------------|---------------|--------------------------------------------------------|--|--|--|

|                 | CAT12              | CPU           | Built-in controller setting and operation mode setting |  |  |  |

|                 | CAT13              | PICT2         | Image quality setting parameters 2                     |  |  |  |

|                 | CAT14              | AE2           | AE related parameters 2                                |  |  |  |

|                 | CAT15              | AWB2          | AWB related parameters 2                               |  |  |  |

|                 | CAT16              | OPDWND2       | OPD window related parameters 2                        |  |  |  |

| Priority1       | CAT17              | EXTSYNC2      | External synchronization parameters related 2          |  |  |  |

|                 | CAT18              | FIX           | -                                                      |  |  |  |

|                 | CAT19              | PREADJ        | Adustment related parameters.                          |  |  |  |

|                 | CAT20              | PORT          | Port driver setting parameters                         |  |  |  |

|                 | CAT21              | BLMDET2       | Blemish detection related parameters.                  |  |  |  |

|                 | CAT23              | SOUT2         | Serial output setting parameters 2                     |  |  |  |

<sup>\*</sup> When DSP's CPU processing is not necessary, using an external microcomputer or other, set the Priority1 parameters to OFF and perform adjustments using the Priority2 parameters.

Table 4.1-2 Priority2 Communication Category Table

| Control subject | Category<br>number | Category name | Description                                    |  |

|-----------------|--------------------|---------------|------------------------------------------------|--|

| Priority2       | CAT1               | SYSCON        | Parameters related to general system settings  |  |

|                 | CAT2               | PICT1         | Image quality setting parameters 1             |  |

|                 | CAT3               | FIX           | -                                              |  |

|                 | CAT4               | AWB1          | AWB related parameters 2.                      |  |

|                 | CAT5               | OPDWND1       | Nondisclosure parameters                       |  |

|                 | CAT6               | TG            | High-speed phase adjustment related parameters |  |

|                 | CAT7               | EXTSYNC1      | External synchronization parameters related 1  |  |

|                 | CAT8               | FEADJ(EVRI)   | Internal EVR related parameters.               |  |

|                 | CAT9               | MASKPG        | Mask function and PG related parameters.       |  |

|                 | CAT10              | DIF           | Digital interface related parameters.          |  |

|                 | CAT11              | BLMDETS1      | Blemish detection related parameters.          |  |

|                 | CAT22              | SOUT1         | Serial output setting parameters 1             |  |

|                 | CAT24              | TEST          | Test related parameters                        |  |

#### 4.2. EEPROM Write Method

The write procedure below describes the case when using the SS-11X control software, but the procedure is the same when using an external microcomputer. See "7.1.4 Communication Format" for the external microcomputer command specifications.

#### 4.2.1. Initial Write (EEPROM Empty State)

- 1. Set CPUHOLD (CAT12\_Byte5\_bit0) to 1[h].

- 2. All the parameters (all categories) send and write.

EEPROM sub menu -> Select procedure "Send -> Write -> Read" -> All Select button -> Start button

- \* Verify is executed immediately after EEPROM write, so check that the write results are OK. When write cannot be performed or when the results are NG, check whether trouble occurred in the EEPROM or the serial communication connection (CASI, CASO, CASCK, and CSROM).

- 3. Restart [Power-on reset (XRST: L -> H)].

- 4. Set CPUHOLD (CAT12\_Byte5\_bit0) to 0[h].

- 5. Send and write only CAT12.

EEPROM sub menu -> Select procedure "Send -> Write -> Read" -> Click CAT12 -> Start button

6. Restart [Power-on reset (XRST: L -> H)].

#### < Note >

In the initial process the CXD4103 reads the EEPROM addresses 000[h] and 001[h] and compares the "Chip ID code". When the read data does not match the specified value, the EEPROM is recognized as invalid. Be sure to perform "4.2.1 Initial Write (EEPROM Empty State)" to write the "Chip ID code".

Initial process: The process performed by the DSP internal CPU the first time the power is turned on. Restart: Power-on reset (XRST: L -> H)

#### 4.2.2. Second and Subsequent Write (when not including CAT12)

- 1. Set CPUHOLD (CAT12\_Byte5\_bit0) to 1[h].

- 2. Select, send and write the arbitrary categories.

EEPROM sub menu -> Select procedure "Send -> Write -> Read" -> Select arbitrary CAT -> Start button

- 3. Restart [Power-on reset (XRST: L -> H)].

#### < Note when writing CAT12 >

When CAT12 is written in the EEPROM with CPUHOLD = 1[h], CPU control stops. To use CPU control, set CPUHOLD = 0[h] and write only CAT12 in the EEPROM again.

When the verify process is performed with CPUHOLD = 0[h], the values of parameters subject to Priority1 control may differ from the EEPROM values. When performing control using an external microcomputer, CPU control must be stopped. See" 11.1 Parameters Subject to Priority1 Control" for the parameters subject to Priority1 control.

#### < Procedure for note when writing CAT12 >

- 1. Set CPUHOLD (CAT12\_Byte5\_bit0) to 1[h].

- 2. Select, send and write the arbitrary categories including CAT12.

- 3. Set CPUHOLD (CAT12\_Byte5\_bit0) to 0[h].

- 4. Send and write only CAT12.

- 5. Restart [Power-on reset (XRST: L -> H)].

## 5. Power Source

## 5.1. Supply Voltage

The SS-11X requires the following five types of power sources as the system power supplies.

+1.8V: I/O power source for CXD4103R

+3.3V: Analog power source for CXD4103R

I/O power source for CXD4103R Power source for CXA2096N Power source for EEPROM

Power source for RS-232C transceiver

+5.0V : Power source of voltage regulator for 1/3 CCD image sensor

VH : Power source for CXD1267AN (V driver, shutter driver, Vsub generation circuit)

Power source for CCD image sensor

VL : Power source for CXD1267AN (V driver, shutter driver)

Protective transistor input voltage for CCD image sensor

\*Care should be taken as the voltage (+5.0V, VH, VL) differs according to the drive specification of the CCD image sensor.

#### 5.1.1. Supply Voltage Accuracy

When using SS-11X, the power source tolerances are as follows.

Table 5.1-1 SS-11X Supply Voltage and Accuracy

| Supply Voltage (typ.) | Tolerance                             |  |

|-----------------------|---------------------------------------|--|

| +1.8V                 | ±0.15V                                |  |

| +3.3V                 | ±0.3V or Refer to the CCD data sheet  |  |

| +5.0V                 | ±0.25V or Refer to the CCD data sheet |  |

| VH                    | Refer to the CCD data sheet           |  |

| VL                    | Refer to the CCD data sheet           |  |

#### 5.1.2. Power Consumption

Examples of measured current consumption values when driving ICX408AK are shown in the table below. These values were measured using a Sony Semiconductor evaluation board, and should be used as reference values.

Table 5.1-2 Power Consumption Measurements (when driving ICX408AK)

|                   | Pin name         | Voltage<br>[V]  | PIN number        | Current consumption [mA] | Power consumption [mW] |

|-------------------|------------------|-----------------|-------------------|--------------------------|------------------------|

| CXD4103R          | DVDD 0,1,4,5,6,8 |                 | 7,21,50,57,72,109 | 12.51                    | 218.887                |

|                   | DVDD 2,3         | 1.8             | 29,33             | 1.66                     |                        |

|                   | DVDD 7           |                 | 101               | 9.04                     |                        |

|                   | VDE 0            |                 | 15                | 0.00                     |                        |

|                   | VDE 10,11,2,3,4  | 3.3<br>(Logic)  | 23,27,35,39,45    | 4.87                     |                        |

|                   | VDE 50,51        |                 | 54,66             | 0.01                     |                        |

|                   | VDE 6,7          |                 | 96,105            | 7.72                     |                        |

|                   | VDE 8            |                 | 115               | 0.00                     |                        |

|                   | AVD 0            | 3.3<br>(Analog) | 6                 | 26.55                    |                        |

|                   | AVD 1            |                 | 79                | 0.50                     |                        |

|                   | AVD 2            |                 | 83                | 7.75                     |                        |

|                   | AVD 3            |                 | 87                | 6.27                     |                        |

| CXA2096N          | Vcc 1,2,3        | 3.3             | 5,16,23           | 47.88                    | 158.004                |

| CXD1267AN         | VH               | 15              | 2                 | 0.83                     | 26.100                 |

|                   | VL               | -7              | 6                 | 1.95                     |                        |

| CCD<br>(ICX408AK) | VDD              | 15              | -                 | 4.20                     | 63.000                 |

|                   | VL               | -7              | -                 | 0.00                     |                        |

#### 5.1.3. Power-on Sequence

In order to properly power up the CCD input VL last. DSP power-up requires +1.8V followed by +3.3V to be applied with a 2-3 msec delay between applications.

The VH and +5V may be applied at any time before VL.

\*Depending on the type of CCD sensor being used the voltage levels may change Please check the documentation.

# 6. CCD Type Selection

# 6.1. CCD type

Note that the types shown below are the types supported at the time these Application Notes were prepared. Some types may be added or eliminated due to CCD version upgrades or discontinued production.

Table 6.1-1 CCD Image Sensors Supported by the SS-11X

| Optical size | Number of pixels | TV system                                                                                                                                                       | Product name |

|--------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|              |                  | NTSC                                                                                                                                                            | ICX404AK     |

|              | 510H             | NTSC                                                                                                                                                            | ICX254AK     |

|              | 31011            | DΛΙ                                                                                                                                                             | ICX405AK     |

| Type 1/3     |                  | NTSC ICX404/<br>ICX254/<br>ICX254/<br>ICX255/<br>ICX408/<br>ICX258/<br>ICX409/<br>ICX259/<br>ICX206/<br>ICX226/<br>PAL ICX207/<br>ICX227/<br>ICX227/<br>ICX228/ | ICX255AK     |

| Type 1/3     |                  | NTSC                                                                                                                                                            | ICX408AK     |

|              | 760H             | NTSC                                                                                                                                                            | ICX258AK     |

|              |                  |                                                                                                                                                                 | ICX409AK     |

|              |                  |                                                                                                                                                                 | ICX259AK     |

|              | 510H             | NTSC                                                                                                                                                            | ICX206AK     |

|              |                  |                                                                                                                                                                 | ICX226AK     |

|              |                  | PAL                                                                                                                                                             | ICX207AK     |

| Type 1/4     |                  |                                                                                                                                                                 | ICX227AK     |

| Type 1/4     |                  | NTSC                                                                                                                                                            | ICX228AK     |

|              | 760H             | INTOC                                                                                                                                                           | ICX278AK     |

|              | 7 0011           | PAL                                                                                                                                                             | ICX229AK     |

|              |                  | IAL                                                                                                                                                             | ICX279AK     |

<sup>\*</sup> Inquiry about CCD types not listed above may be answered by SONY Sales.

### 6.2. Operation Mode Selection for Each CCD

#### 6.2.1. System Configuration and MODESEL

The basic clock system for the SS-11X basic consists of a clock system configured by the single oscillator (ECK) used by the internal system and a PLL clock system that uses the two types of oscillators (ECK and MCK) used by the line lock system.

In addition, a clock system can be configured for each type of CCD as an operation mode. The clock frequency (oscillator frequency) combinations for each CCD type are shown in "**Table 6.2-1**".

The MODESEL function switches the above-mentioned clock system operation modes using the P12 to P15 pins of the CXD4103 which are assigned as the initial settings ( "Table 3.1-1") and the pins for the port driver described hereafter ( "Table 9.1-1").

Number TV P15 P14 P13 P12 **ECK MCK MODESEL** of system pixels Low Low Low 38.13986MHz 0[h]Low 510H High 27.00000MHz 38.13986MHz Low Low Low 2[h] **NTSC** Low High High Low 28.63636MHz 6[h] 760H High Low Low Low 27.00000MHz 28.63636MHz 8[h] Low High High 37.87500MHz Low 3[h] 510H Low High Low High 27.00000MHz 37.87500MHz 5[h] PAL High Low Low High 28.37500MHz 9[h] 760H High Low High High 27.00000MHz 28.37500MHz B[h]

Table 6.2-1 Relationship between CCD Type and Clock Frequencies

The internal clock of the CXD4103 is switched according to the operation mode. Set the P12 to P15 pins of the CXD4103 by wiring to the VDD or GND side and pulling up/down according to the system conditions to be used (TV system, supported CCD). Be sure to make these settings correctly as the clock system does not operate normally when the above setup is incorrect.

MODESEL is controlled by the CXD4103, and operation is determined and reflected to the parameter in "Table 6.2-2" by making the P12 to P15 pin settings. Therefore, there is no need to set the parameter in the table below.

Table 6.2-2 MODESEL Parameter

| P       | arameter           | Description                                                               |

|---------|--------------------|---------------------------------------------------------------------------|

| MODESEL | CAT12_Byte1_bit0-3 | 0[h] to B[h]: DSP operation mode For details, see " <b>Table 6.2-1</b> ". |

# 6.3. Important Information on Wiring

The drive circuit must be changed according to the type of CCD used. The main differences are as follows.

- 1. Changes in the drive circuit due to different CCD image sensor drive specifications

- 2. Changes in the clock system due to different CCD types and TV systems (NTSC/PAL)

- 3. Changes in the frequency response due to different CCD types

- 4. Changes in the modes due to different CCD types and TV systems (NTSC/PAL)

# 6.3.1. Drive Circuit Changes

The drive specifications of CCD image sensors that can be driven by the SS-11X are shown in the Table below.

Table 6.3-1 CCD Image Sensors and Drive Conditions

| Optical |        |          | DC voltage specifications        |                          | AC voltage specifications             |       |       | Drive<br>circuit |

|---------|--------|----------|----------------------------------|--------------------------|---------------------------------------|-------|-------|------------------|

| size    | pixels | name     | Vsub<br>voltage                  | RG voltage               | н                                     | RG    | V     | example          |

|         |        | ICX254AK |                                  | Generated internally,    |                                       |       |       |                  |

|         | 510H   | ICX255AK |                                  | adjustment<br>free       |                                       |       |       |                  |

|         |        | ICX404AK |                                  | Clamped high, adjustment |                                       |       |       | Fig 6.3-1        |

| Туре    |        | ICX405AK |                                  | free                     | 5.0V                                  | 5.0V  | -7.0V |                  |

| 1/3     |        | ICX258AK | Generated internally, adjustment | Generated internally.    | Generated internally, adjustment free |       |       |                  |

|         | 760H   | ICX259AK |                                  | adjustment               |                                       |       |       |                  |

|         |        | ICX408AK |                                  | Clamped high, adjustment |                                       |       |       |                  |

|         |        | ICX409AK |                                  | free                     |                                       |       |       |                  |

|         |        | ICX206AK | free                             |                          |                                       | 2 2)/ | -7.0V | Fig 6.3-2        |

|         | 510H   | ICX207AK |                                  |                          |                                       |       |       |                  |

|         | 31011  | ICX226AK |                                  | 0                        |                                       |       |       |                  |

| Туре    | Type   | ICX227AK |                                  | Generated internally,    | 3.3V                                  |       |       |                  |

| 1/4     |        | ICX228AK |                                  | adjustment<br>free       | 3.3V 3.3V                             | 3.3V  |       |                  |

|         | 760H   | ICX229AK |                                  |                          |                                       |       |       |                  |

|         | 7 0011 | ICX278AK |                                  |                          |                                       |       |       |                  |

|         |        | ICX279AK |                                  |                          |                                       |       |       |                  |

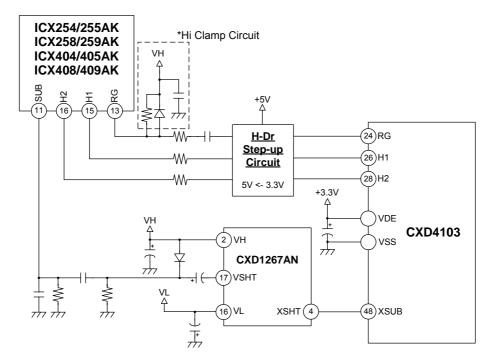

Fig 6.3-1 Example 1/3 Type CCD Drive Circuit

"Fig 6.3-1" shows the drive circuit when using 1/3 type CCD image sensors (ICX254/255AK, ICX404/405AK, ICX228/229AK, ICX408/409AK).

Both Vsub voltage and RG voltage are adjustment-free. Vsub is a voltage generated inside the CCD and is used to clamp the shutter pulse, so an external clamping circuit is not required. The SUB output is input via a capacitor to the CCD's SUB pin.

As for H1, H2, and RG, because the output of CXD4103 is 3.3V, the level conversion circuit of "3.3V -> 5.0V" is needed between CXD4103 and CCD.

RG is input to the CCD after its DC component is cut by a capacitor. The high clamp circuit might be needed.

<sup>\*</sup>Please refer to CCD specification sheet.

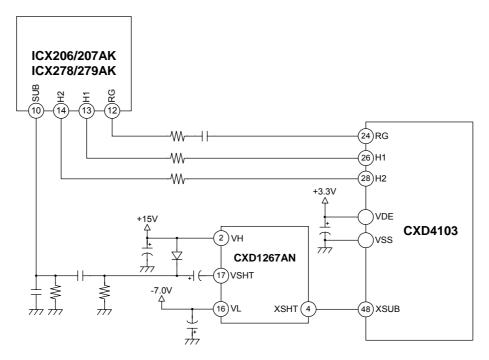

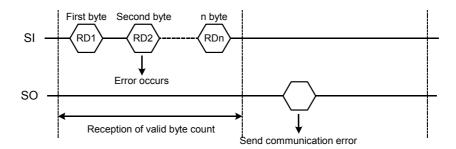

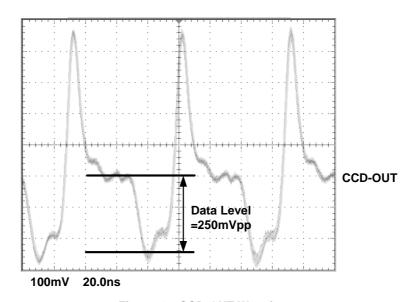

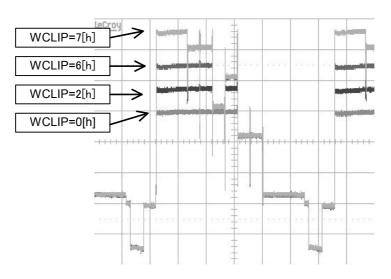

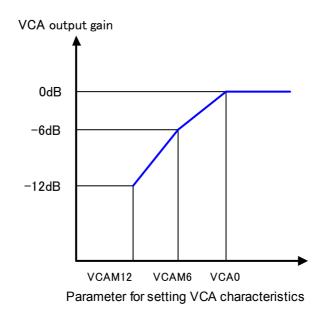

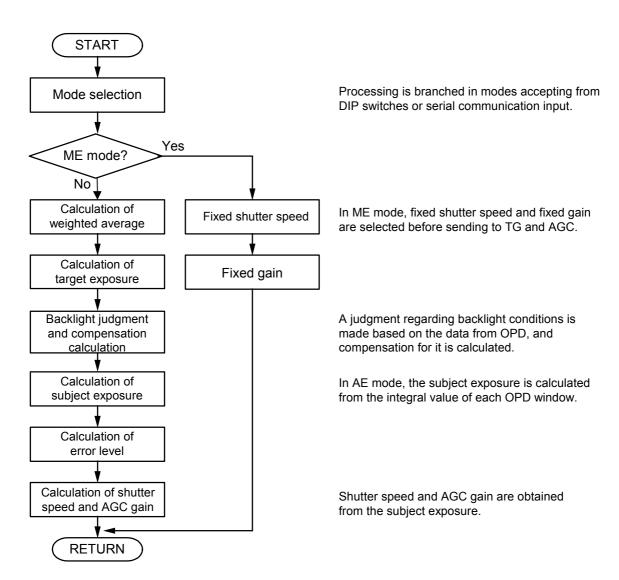

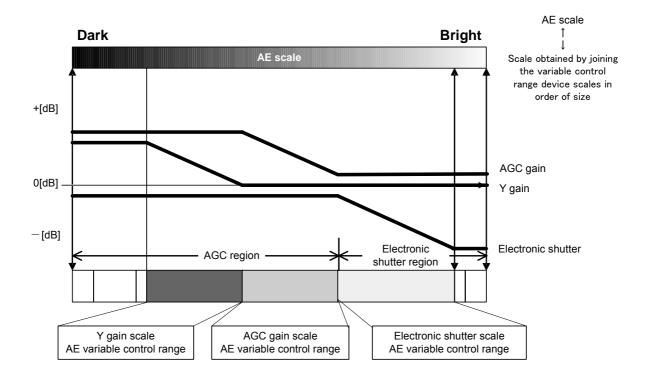

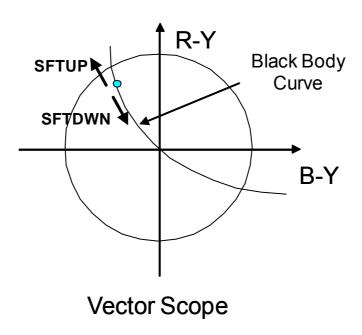

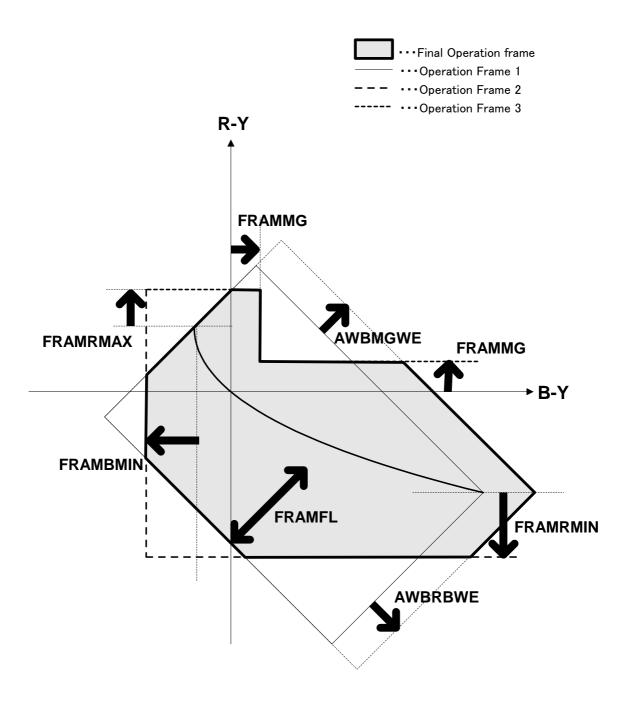

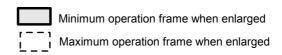

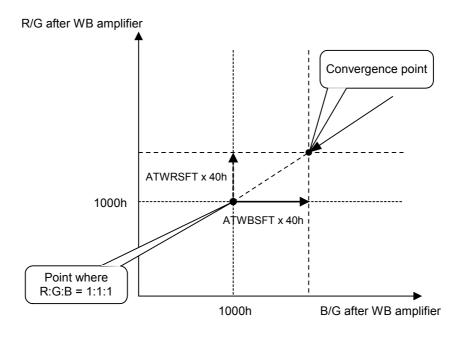

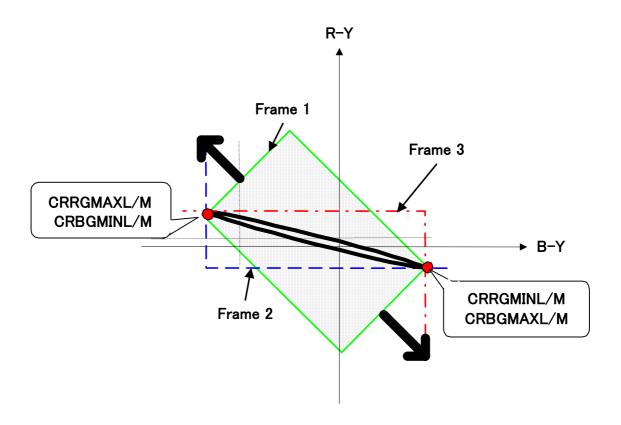

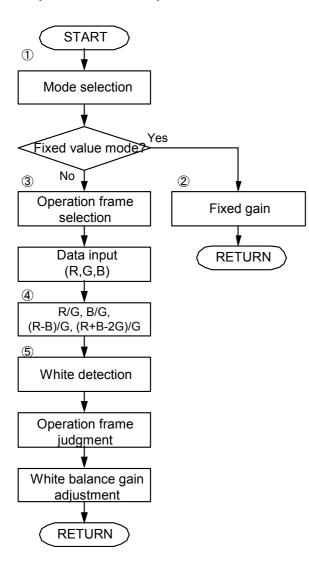

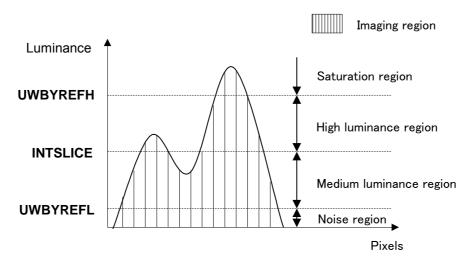

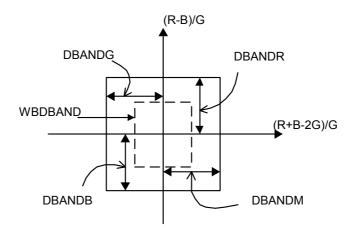

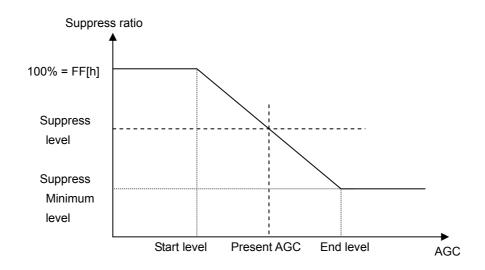

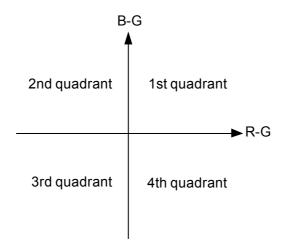

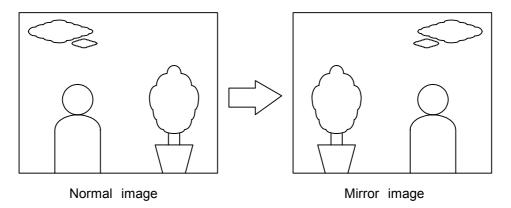

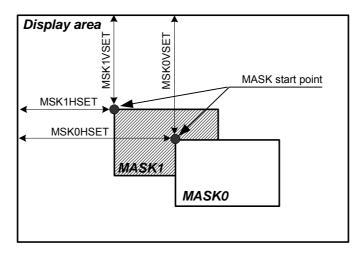

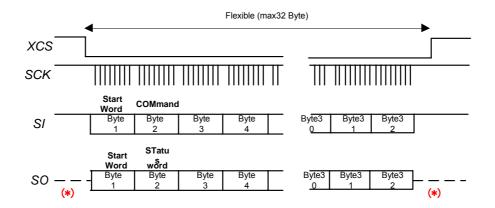

Fig 6.3-2 Example 1/4 Type CCD Drive Circuit