# IN-PLUG® series: IPS25 Self-Powered Precision Feedback Controller

for Very Low Cost, Low Power Switching Power Supplies

- REVISION 10 -

#### INTRODUCTION

#### DESCRIPTION

The IN-PLUG® IPS25 Integrated Circuit is a self-powered precision feedback controller for fly-back off-line switching power supply applications. It can be powered from the load voltage even under short-circuit conditions, therefore saving the auxiliary circuitry normally required to power it. Especially designed to address very low-cost, low-power fly-back power supplies which output current does not exceed approximatly 800 mA. It can be used for:

- Voltage regulation / current limiting or

- Current regulation / voltage limiting. It contains the following features:

- Trimmed band-gap references.

- Voltage & current error amplifiers.

- Loop compensation circuitry for both V & I.

- Opto drivers.

This low-cost IC has been optimized to operate in conjunction with the IN-PLUG<sup>®</sup>IPS10/IPS15 primary SMPS off-line driver ICs, for domestic and international inputs ranging from 85V to 264V AC.

The IPS25 feedback controller can also be used for different applications where the primary circuitry is built around discrete components or standard ICs other than AAI's IPS10/IPS15 ICs.

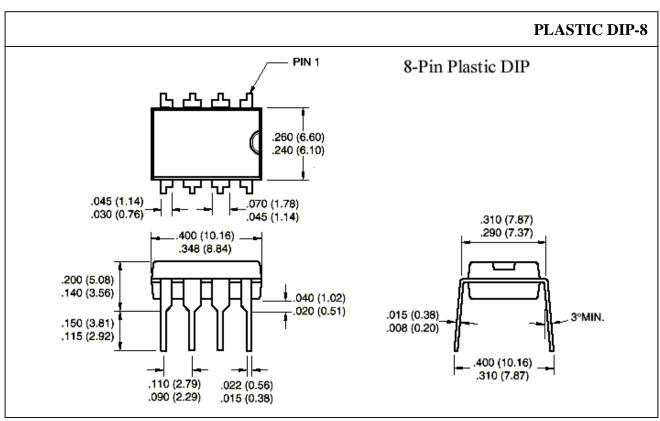

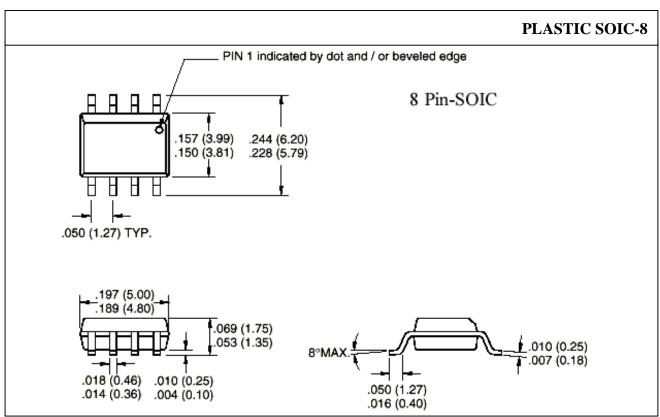

## PIN CONFIGURATION: DIP-8 / SOIC-8

#### **FEATURES**

- Lowest cost solution for low-power off-line flyback applications.

- High performance SMPS.

- Full flexibility for loop stability control.

- Operates with optocoupler for maximum isolation from line voltage.

#### **APPLICATIONS**

- Standby power supplies for TV, VCR and IR remotely-controlled appliances.

- Cordless and feature phones.

- Cellular phone chargers.

- Power tools fast chargers with trickle and on/off.

- Laptops and personal digital assistants.

- Utility meters.

- Cost-effective replacements for bulky plug-in transformers.

#### ORDERING INFORMATIONS

| Part No.  | ROHS /  | Package    | Temperature Range |            |  |

|-----------|---------|------------|-------------------|------------|--|

|           | Pb-Free |            |                   |            |  |

| IPS25C-D  | -G-LF   | 8-Pin PDIP | 0°C to +70°C      | Commercial |  |

| IPS25I-D  | -G-LF   | 8-Pin PDIP | -40°C to +85°C    | Industrial |  |

| IPS25C-SO | -G-LF   | 8-Pin SOIC | 0°C to +70°C      | Commercial |  |

| IPS25I-SO | -G-LF   | 8-Pin SOIC | -40°C to +85°C    | Industrial |  |

For detailed ordering information, see page 12

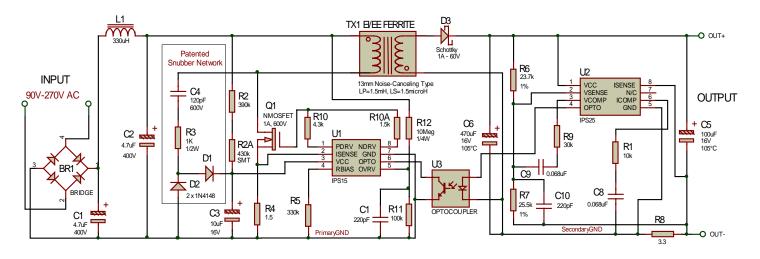

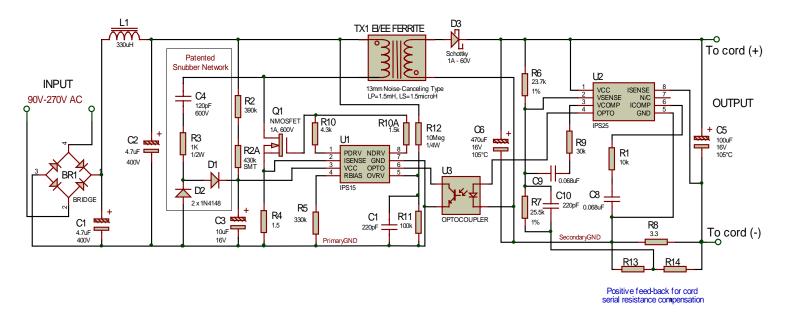

## **BASIC APPLICATION SCHEMATIC**

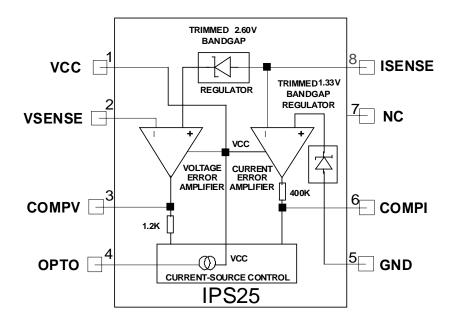

#### **FUNCTIONAL BLOCK DIAGRAM**

# PIN DESCRIPTION

| Number | Name   | Description                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1      | VCC    | IC positive supply pin.  The IC is powered from this pin which is connected to the positive output of the SMPS and powers the chip during both normal operation and short-circuit conditions.                                                                                                                                   |  |  |  |  |

| 2      | VSENSE | Voltage sensing pin.                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|        |        | Inverting input of the voltage error amplifier which positive input is connected to an internal trimmed 2.57V voltage reference. An external voltage divider connected to this point sets the output voltage. This pin is also used for voltage loop compensation when required.                                                |  |  |  |  |

| 3      | COMPV  | Voltage loop compensation pin.                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|        |        | This is the output of the voltage error amplifier. The loop compensation network, when required, is connected between this point and VSENSE pin. Please note that this pin is not a zero-impedance node.                                                                                                                        |  |  |  |  |

| 4      | OPTO   | Optocoupler driver pin.                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|        |        | This pin drives and external optocoupler connected to GND. A current-mode drive is used for maximum noise rejection.                                                                                                                                                                                                            |  |  |  |  |

| 5      | GND    | Ground pin.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|        |        | This is the most negative IC pin. The first output decoupling capacitor should return to it.                                                                                                                                                                                                                                    |  |  |  |  |

|        |        | Do not confuse this pin with the ISENSE pin which is connected to the negative output of the SMPS.                                                                                                                                                                                                                              |  |  |  |  |

| 6      | COMPI  | Current loop compensation pin.                                                                                                                                                                                                                                                                                                  |  |  |  |  |

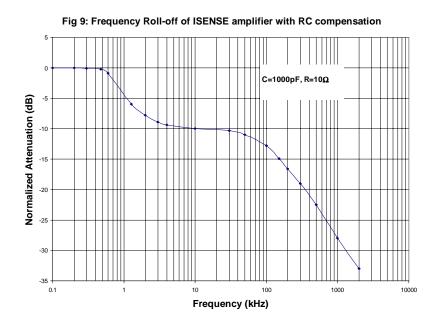

|        |        | This pin is used to compensate the current-limiting loop. In order to prevent conflicts with the voltage loop, this compensation is performed on an intermediate stage which impedance is approximately $400 \text{K}\Omega$ .                                                                                                  |  |  |  |  |

| 7      | NC     | Not connected pin (spare).                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|        |        | This pin is not internally connected in the IPS25. It is available to provide additional features when ordering custom variations of the basic IPS25.                                                                                                                                                                           |  |  |  |  |

| 8      | ISENSE | Current sensing pin.                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|        |        | This pin is connected to the negative output of the SMPS. A current-sensing resistor connected between this point and GND is used to sense the output current. Current limiting occurs when the voltage developed reaches 1.33V. Please note that the second output decoupling capacitor should return to this pin, not to GND. |  |  |  |  |

# IN-PLUG® IPS25 FUNCTIONAL DESCRIPTION

The IN-PLUG $^{\$}$  IPS25 Integrated Circuit was especially designed for voltage regulation / current limiting or current regulation / voltage limiting in very low-cost, low-power fly-back power supply applications which output current does not exceed approximately 800 mA.

It is a self-powered precision feedback controller for fly-back off-line switching power supply applications. It can be powered from the load voltage even under short-circuit conditions, therefore saving the auxilliary circuitry normally required to power it.

It provides precise and temperature-stable voltage and current regulations that can be fully and independently adjusted.

It sources the current necessary to drive a ground-referred optocoupler for maximum noise rejection and low output ripple.

## The principal features are:

- Trimmed band-gap references.

- Voltage & current error amplifiers.

- Loop compensation circuitry for both V & I.

- Opto drivers.

## **Secondary circuitry:**

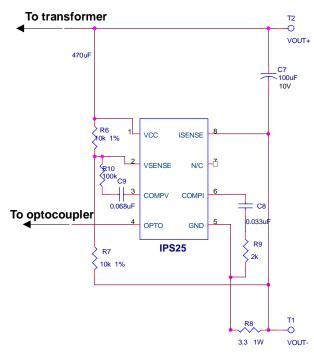

(please refer to the application schematic on page 2)

- 1) The chip is powered through the forward operation of the flyback transformer which ensures proper operation on a dead short-circuit on the output.

- 2) The current limiting is adjustable through R8

- 3) The regulated voltage is adjustable through R6/R7

- 4) COMPI & COMPV pins are available for loop compensations. Current loop compensation is always required whereas voltage loop compensation can usually be omitted when operating in conjunction with the IN-PLUG® IPS10/IPS15 flyback controller ICs.

# **Application informations:**

# ■ Determination of V<sub>out</sub> (Output Voltage):

$V_{out} = VSENSE \times (R6+R7)/R7$ (Typical VSENSE = 2.60V)

# Determination of I<sub>limit</sub> (Current Limit):

$I_{limit} = ISENSE threshold / R8$

(Typical ISENSE threshold = 1.33V)

## **ELECTRICAL CHARACTERISTICS**

| ABSOLUTE MAXIMUM RATING                      |             |       |  |  |  |

|----------------------------------------------|-------------|-------|--|--|--|

| Characteristics                              | Value       | UNITS |  |  |  |

| Max V <sub>CC</sub>                          | 30          | V     |  |  |  |

| Operating junction temperature               | - 40 to 150 |       |  |  |  |

| Storage temperature range                    | - 55 to 150 | °C    |  |  |  |

| Lead temperature (3 mm from case for 5 sec.) | 260         |       |  |  |  |

| PARAMETER                                   | TEST CONDITIONS                                          | PARAMETERS |       |        | UNITS   |

|---------------------------------------------|----------------------------------------------------------|------------|-------|--------|---------|

| Voltage Regulation                          |                                                          |            | TYP.  | MAX.   |         |

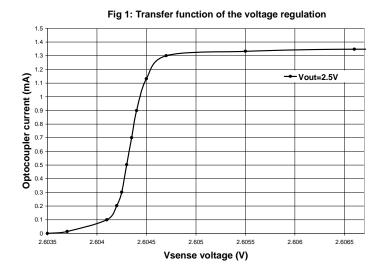

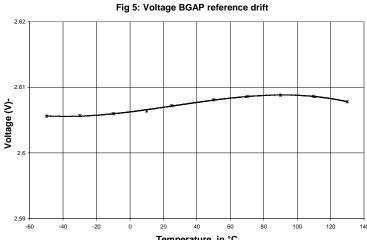

| VSENSE threshold (note1)                    | I <sub>CC</sub> = 1 mA<br>(see figure 1, 2 & 5)          | 2.58       | 2.60  | 2.62   | V       |

| VSENSE threshold variation with temperature | I <sub>cc</sub> = 1 mA, -40°C to +85°C<br>(see figure 5) | -          | +/- 6 | +/- 12 | mV/°C   |

| Output impedance of COMPV                   |                                                          | -          | 1.2   | -      | ΚΩ      |

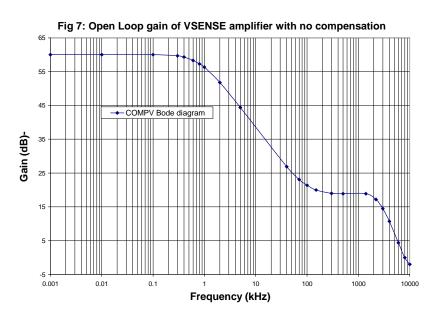

| Voltage gain to COMPV                       | (see figure 7)                                           | -          | 60    | -      | dB      |

| Unity gain bandwidth                        | (see figure 7)                                           | -          | 7     | -      | MHz     |

| Phase margin in unity gain                  |                                                          | -          | 70    | -      | Degrees |

| VSENSE Input current                        |                                                          | -          | -     | 0.6    | μΑ      |

| Transconductance from VSENSE to OPTO        | @ V <sub>CC</sub> = 2.5V<br>(see figure 1)               | -          | 3.5   | -      | mA/mV   |

| Max OPTO output sourcing current            | @ V <sub>CC</sub> = 5V<br>(see figure 1)                 | 2          | 2.8   | -      | mA      |

| Max OPTO output sourcing current            | @ V <sub>CC</sub> = 2.5V<br>(see figure 2)               | 1          | 1.3   | -      | mA      |

| Current Limiting                            |                                                          |            | 1     | 1      | ,       |

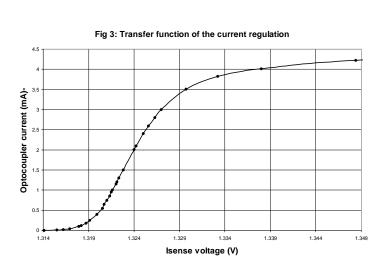

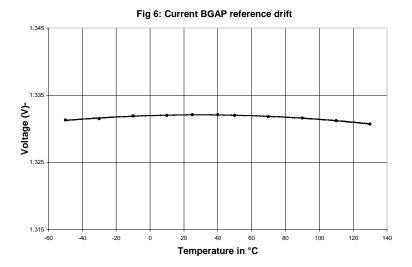

| ISENSE threshold (note1)                    | I <sub>CC</sub> = 1 mA<br>(see figure 3 & 6)             | 1.31       | 1.33  | 1.35   | v       |

| ISENSE threshold variation with temperature | I <sub>CC</sub> = 1 mA, -40°C to +85°C<br>(see figure 6) | -          | +/- 3 | +/- 6  | mV      |

| Output impedance of COMPI                   |                                                          | -          | 400   | -      | ΚΩ      |

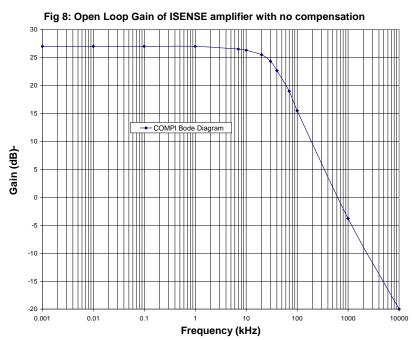

| Voltage gain to COMPI                       | (see figure 8)                                           | -          | 27    | -      | dB      |

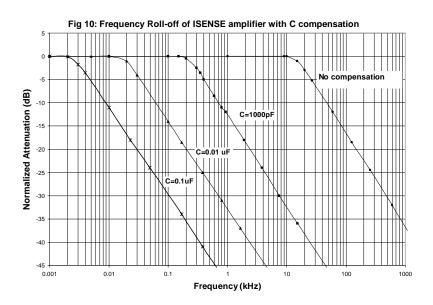

| Unity gain bandwidth to COMPI               | (see figure 10)                                          | -          | 500   | -      | KHz     |

| Phase margin in unity gain                  |                                                          |            | 80    | -      | Degrees |

| Transconductance from ISENSE to OPTO        | (see figure 8)                                           | -          | 0.3   | -      | mA/mV   |

| Max OPTO output sourcing current            | @ V(ISENSE) = 1.33V<br>(see figure 3)                    | 3          | 4     | -      | mA      |

Note1: Tighter tolerances to 0.2% available upon request.

Note2: All values are @ 25°C unless otherwise specified.

Note3: Electrical parameters, although guaranted, are not all 100% tested in production.

Fig 2: Transfer function of the voltage regulation 2.8 2.6 Vout=5V 0.6 0.4 0.2 2.6027 2.6028 2.6029 2.603 2.6031 2.6032 2.6033 2.6034 2.6035 2.6036 Vsense voltage (V)

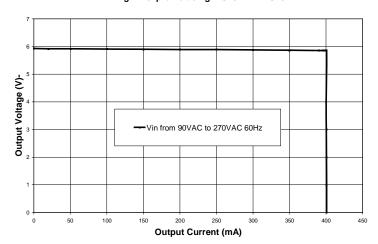

Fig 4: V/I profile using IPS25 with IPS10

Temperature in °C

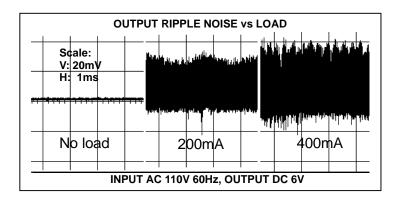

## **OUTPUT RIPPLE Noise**

when the **IPS25** is operating in conjunction with the IN-PLUG<sup>®</sup> **IPS10/IPS15** primary SMPS off-line driver IC.

(see application schematic on page 2)

#### **OUTPUT CORD SERIAL RESISTANCE COMPENSATION**

The voltage drop due to the output serial resistance of the cord can be compensated by adding a voltage positive feedback to the IPS25 input pin VSENSE, proportional to Vdrop. This can be achieved either by splitting R8 (output current sensing resistor) in two or by inserting 2 serial resistors R13 and R14 in parallel to R8 and connect the positive feedback to the intermediate node.

R13 and R14 should be calculated, based on the following conditions:

- $(R13 + R14) \ge 20 \text{ x } R8$  (but should remain low impedance in regards to R7),

- Vint ~ Vdrop, where Vint is the intermediate voltage measured on the common node of R13 and R14, and Vdrop is the voltage drop across the cord serial resistor.

SMPS with output cord

#### PACKAGE DIMENSIONS

#### ORDERING INFORMATION

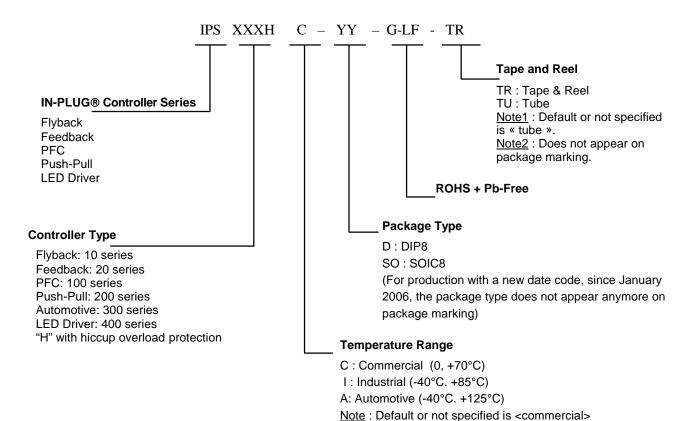

#### **Part-Number**

#### Example of Marking

Non-Green Package Green ROHS + Pb-Free Package

$(\underline{\text{Note}}: \text{For production with a new date code}, \text{ since January 2006, the package type does not appear anymore on package marking)}$

This ordering information is for commercial and industrial standard IN-PLUG® controllers ONLY. For custom controllers or for military temperature range, call AAI's sales representative.

The following is a brief overview of certain terms and conditions of sale of product. For a full and complete copy of all the General Terms and Conditions of Sale, visit our webpage <a href="http://www.asicadvantage.com/terms.htm">http://www.asicadvantage.com/terms.htm</a>.

#### LIMITED WARRANTY

The product is warranted that it will conform to the applicable specifications and be free of defects for one year. Buyer is responsible for selection of, use of and results obtained from use of the product. Buyer indemnifies and holds ASIC Advantage, Inc. harmless for claims arising out of the application of ASIC Advantage, Inc.'s products to Buyer's designs. Applications described herein or in any catalogs, advertisements or other documents are for illustrative purposes only.

#### **CRITICAL APPLICATIONS**

Products are not authorized for use in critical applications including aerospace and life support applications. Use of products in these applications is fully at the risk of the Buyer. Critical applications include any system or device whose failure to perform can result in significant injury to the user.

#### **LETHAL VOLTAGES**

Lethal voltages could be present in the applications. Please comply with all applicable safety regulations.

#### INTELLECTUAL PROPERTY RIGHTS AND PROPRIETARY DATA

ASIC Advantage, Inc. retains all intellectual property rights in the products. Sale of products does not confer on Buyer any license to the intellectual property. ASIC Advantage, Inc. reserves the right to make changes without notice to the products at any time. Buyer agrees not to use or disclose ASIC Advantage Inc.'s proprietary information without written consent.

## **TRADEMARKS AND PATENTS**

- IN-PLUG® is a registered trademark of ASIC Advantage, Inc.

- AAI's modified snubber network is patented under the US Patent # 6,233,165. IN-PLUG® Customers are granted a royalty-free licence for its utilization, provision the parts are purchased factory direct or from an authorized agent.

#### PROTECTION FOR CUSTOM IN-PLUG® SOLUTIONS

When AAI accepts to design and manufacture IN-PLUG® products to Buyer's designs or specifications, buyer has certain obligations to provide defense in a suit or proceeding claiming infringement of a patent, copyright or trademark or for misappropriation of use of any trade secrets or for unfair competition.

#### **COMPLIANCE WITH LAWS**

Buyer agrees that at all times it will comply with all applicable federal, state, municipal, and local laws, orders and regulations. Buyer agrees to comply with all applicable restrictions on exports and re-exports including obtaining any required U.S. Government license, authorization, or approval. Buyer shall pay any duties, levies, taxes, brokerage fees, or customs fees imposed on the products.

#### TITLE AND DELIVERY

All shipments of goods shall be delivered ExWorks, Sunnyvale, CA, U.S.A. Title in the goods shall not pass to Buyer until ASIC Advantage, Inc. has received in full all amounts owed by Buyer.

#### LATEST DATASHEET UPDATES

For the latest datasheet updates, visit our web page: http://www.in-plug.com/datasheets.htm.

#### **WORLDWIDE REPRESENTATIVES**

To access AAI's list of worldwide representatives, visit our web page http://www.in-plug.com/representatives.htm

#### COPYRIGHTS

Copyrights and all other proprietary rights in the Content rests with ASIC Advantage Inc. (AAI) or its licensors. All rights in the Content not expressly granted herein are reserved. Except as otherwise provided, the Content published on this document may be reproduced or distributed in unmodified form for personal non-commercial use only. Any other use of the Content, including without limitation distribution, reproduction, modification, display or transmission without the prior written consent of AAI is strictly prohibited. All copyright and other proprietary notices shall be retained on all reproductions.

ASIC Advantage INC.

1290-B Reamwood Ave, Sunnyvale California 94089, USA Tel: (1) 408-541-8686 Fax: (1) 408-541-8675 Websites: http://www.in-plug.com - http://www.asicadvantage.com