# Phase Shift Resonant Controller

#### **FEATURES**

- Programmable Output Turn On Delay; Zero Delay Available

- Compatible with Voltage Mode or Current Mode Topologies

- Practical Operation at Switching Frequencies to 300kHz

- Four 100mA Totem Pole Outputs

- 10MHz Error Amplifier

- Pin Programmable Undervoltage Lockout

- Low Startup Current 150μA

- Soft Start Control

- Outputs Active Low During UVLO

### **DESCRIPTION**

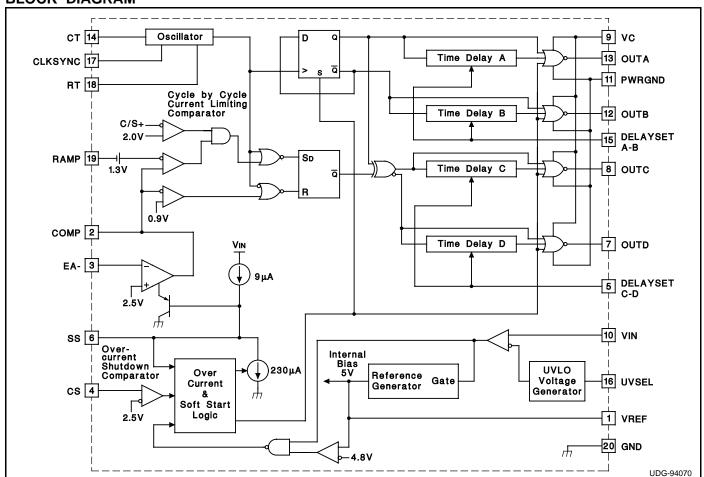

The UC3879 controls a bridge power stage by phase shifting the switching of one half-bridge with respect to the other. This allows constant frequency pulse width modulation in combination with resonant, zero-voltage switching for high efficiency performance. The UC3879 can be configured to provide control in either voltage mode or current mode operation, with overcurrent shutdown for fast fault protection.

Independently programmable time delays provide dead-time at the turn-on of each output stage, allowing time for each resonant switching interval.

With the oscillator capable of operating in excess of 600kHz, overall output switching frequencies to 300kHz are practical. In addition to the standard free running mode, with the CLKSYNC pin, the user may configure the UC3879 to accept an external clock synchronization signal. Alternatively, up to three units can be locked together with the operational frequency determined by the fastest device.

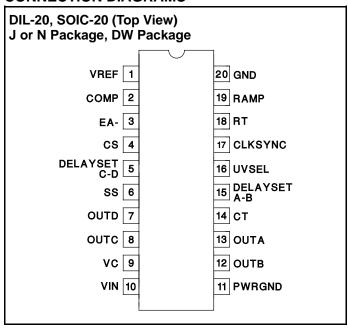

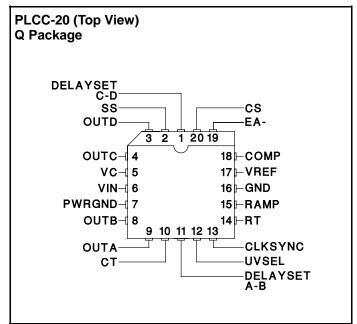

Protective features include an undervoltage lockout and overcurrent protection. Additional features include a 10MHz error amplifier, a 5V precision reference, and soft start. The UC3879 is available in 20 pin N, J, DW, and Q and 28 pin L packages.

### **BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (VC, VIN)                               |

|--------------------------------------------------------|

| (Pins 1, 2, 3, 4, 5, 6, 14, 15, 17, 18, 19)0.3 to 5.3\ |

| (Pin 16)                                               |

| Storage Temperature Range                              |

| Lead Temperature (Soldering, 10 sec.) +300°C           |

Notes: Pin references are to 20 pin DIL and SOIC packages. All voltages are with respect to ground unless otherwise stated. Currents are positive into, negative out of the specified terminal. Consult Packaging Section of Databook for thermal limitations and considerations of packages.

## **CONNECTION DIAGRAMS**

**ELECTRICAL CHARACTERISTICS** Unless specified; VC = VIN = VUVSEL =12V, CT = 470pF, RT = 9.53k, RDELAYSET A-B = RDELAYSET C-D = 4.8k, CDELAYSET A-B = CDELAYSET C-D =  $0.01\mu$ F, TA =  $-40^{\circ}$ C to  $85^{\circ}$ C for the UC2879,  $0^{\circ}$ C to  $70^{\circ}$ C for the UC3879. TA = TJ.

| PARAMETER             | TEST CONDITIONS                                                | MIN   | TYP   | MAX   | UNITS |

|-----------------------|----------------------------------------------------------------|-------|-------|-------|-------|

| Undervoltage Lockout  |                                                                |       |       |       |       |

| Start Threshold       | Vuvsel = VIN                                                   | 9     | 10.75 | 12.5  | V     |

|                       | Vuvsel = Open                                                  | 12.5  | 15.25 | 16.5  | V     |

| UVLO Hysteresis       | VUVSEL = VIN                                                   | 1.15  | 1.75  | 2.15  | V     |

|                       | Vuvsel = Open                                                  | 5.2   | 6     | 7.4   | V     |

| Input Bias, UVSEL Pin | VUVSEL = VIN = 8V                                              |       | 30    |       | μΑ    |

| Supply Current        |                                                                |       |       |       |       |

| Ivin Startup          | VIN = VUVSEL = 8V, VC = 18V, IDELAYSET A-B = IDELAYSET C-D = 0 |       | 150   | 600   | μΑ    |

| Ivc Startup           | VIN = VUVSEL = 8V, VC = 18V, IDELAYSET A-B = IDELAYSET C-D = 0 |       | 10    | 100   | μА    |

| Ivin Operating        |                                                                |       | 23    | 33    | mA    |

| Ivc Operating         |                                                                |       | 4     | 8     | mA    |

| Voltage Reference     |                                                                |       |       |       |       |

| Output Voltage        | T <sub>J</sub> = +25°C                                         | 4.92  | 5     | 5.08  | V     |

| Line Regulation       | 11V < VIN < 18V                                                |       | 1     | 10    | mV    |

| Load Regulation       | IVREF = -10mA                                                  |       | 5     | 20    | mV    |

| Total Variation       | Line, Load, Temperature                                        | 4.875 |       | 5.125 | V     |

| Short Circuit Current | VREF = 0V, TJ = 25°C                                           |       | -60   | -15   | mA    |

**ELECTRICAL CHARACTERISTICS (cont.)** Unless specified; VC = VIN = Vuvsel =12V, CT = 470pF, RT = 9.53k, IDELAYSET A-B = IDELAYSET C-D =  $-500\mu$ A CDELAYSET A-B = CDELAYSET C-D =  $0.01\mu$ F, TA =  $-40^{\circ}$ C to 85°C for the UC2879, 0°C to 70°C for the UC3879. TA = TJ.

| PARAMETER                                    | TEST CONDITIONS                  | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------|----------------------------------|------|------|------|-------|

| Error Amplifier                              |                                  |      |      |      |       |

| Error Amplifier Input Voltage                |                                  | 2.4  | 2.5  | 2.6  | V     |

| Input Bias Current                           |                                  |      | 0.6  | 3    | μΑ    |

| AVOL                                         | 1V < VCOMP < 4V                  | 60   | 90   |      | dB    |

| PSRR                                         | 11V < VIN < 18V                  | 85   | 100  |      | dB    |

| Output Sink Current                          | VCOMP = 1V                       | 1    | 2.5  |      | mA    |

| Output Source Current                        | VCOMP = 4V                       |      | -1.3 | -0.5 | mA    |

| Output Voltage High                          | ICOMP = -0.5mA                   | 4    | 4.7  | 5    | V     |

| Output Voltage Low                           | ICOMP = 1mA                      | 0    | 0.5  | 1    | V     |

| Slew Rate                                    | TA = +25°C                       | 6    | 11   |      | V/μs  |

| PWM Comparator                               |                                  |      |      |      | -     |

| RAMP Offset Voltage                          | T <sub>J</sub> = 25°C, Note 3    | 1.1  | 1.25 | 1.4  | V     |

| PWM Phase Shift,                             | VCOMP > VRAMPpeak + VRAMPoffset  | 98   | 99.7 | 102  | %     |

| TDELAYSET A-B, C-D = 0, Note 1               | VCOMP < Zero Phase Shift Voltage | 0    | 0.3  | 2    | %     |

| Output Skew,                                 | VCOMP > VRAMPpeak + VRAMPoffset  |      | 10   |      | ns    |

| TDELAYSET A-B, C-D = 0, Note 1               | VCOMP < Zero Phase Shift Voltage |      | 10   |      | ns    |

| Ramp to Output Delay, TDELAYSET A-B, C-D = 0 |                                  |      | 115  | 250  | ns    |

| Oscillator                                   |                                  | -    |      | •    |       |

| Initial Accuracy                             | TA = 25°C                        | 180  | 200  | 220  | kHz   |

| Voltage Stability                            | 11V < VIN < 18V                  |      | 1    | 2    | %     |

| Total Variation                              | Line, Temperature                | 160  | 200  | 240  | kHz   |

| CLKSYNC Threshold                            |                                  | 2.3  | 2.5  | 2.7  | V     |

| Clock Out High                               |                                  | 2.8  | 4    |      | V     |

| Clock Out Low                                |                                  | 0.5  | 1    | 1.5  | V     |

| Clock Out Pulse Width                        |                                  |      | 400  | 600  | ns    |

| Ramp Valley Voltage                          |                                  |      | 0.2  | 0.4  | V     |

| Ramp Peak Voltage                            |                                  | 2.8  | 2.9  | 3.2  | V     |

| Current Limit                                |                                  |      |      |      | -     |

| Input Bias                                   | Vcs = 3.0V                       |      | 2    | 10   | μΑ    |

| Threshold Voltage                            |                                  | 2.35 | 2.5  | 2.65 | V     |

| Delay to OUTA, B, C, D                       |                                  |      | 160  | 300  | ns    |

| Cycle-by-Cycle Current Limit                 |                                  |      |      |      |       |

| Input Bias                                   | Vcs = 2.2V                       |      | 2    | 10   | μΑ    |

| Threshold Voltage                            |                                  | 1.85 | 2    | 2.15 | V     |

| Delay to Output Zero Phase                   |                                  |      | 110  | 300  | ns    |

| Soft Start/Reset Delay                       |                                  |      |      |      |       |

| Charge Current                               | Vss = 0.5V                       | -20  | -9   | -3   | μΑ    |

| Discharge Current                            | Vss = 1V                         | 120  | 230  |      | μA    |

| Restart Threshold                            |                                  | 4.3  | 4.7  |      | V     |

| Discharge Level                              |                                  |      | 300  |      | mV    |

| Output Drivers                               |                                  |      |      |      |       |

| Output Low Level                             | IOUT = 10mA                      |      | 0.3  | 0.4  | V     |

| Output High Level                            | IOUT = -10mA, Referenced to VC   |      | 2.2  | 3    | V     |

ELECTRICAL CHARACTERISTICS (cont.) Unless specified; VC = VIN = VUVSEL = 12V, CT = 470pF, RT = 9.53k, IDELAYSET A-B = IDELAYSET C-D =  $-500\mu$ A CDELAYSET A-B = CDELAYSET C-D =  $0.01\mu$ F, TA =  $-40^{\circ}$ C to 85°C for the UC2879, 0°C to 70°C for the UC3879. TA = TJ.

| PARAMETER          | TEST CONDITIONS                      | MIN | TYP | MAX | UNITS |

|--------------------|--------------------------------------|-----|-----|-----|-------|

| Delay Set (Note 5) |                                      |     |     |     |       |

| Delay Time         | RDELAYSET A-B = RDELAYSET C-D = 4.8k | 300 | 450 | 600 | ns    |

| Delay Time         | RDELAYSET A-B = RDELAYSET C-D = 1.9k | 130 | 200 | 250 | ns    |

| Zero Delay         | VDELAYSET A-B = VDELAYSET C-D = 5V   |     | 5   |     | ns    |

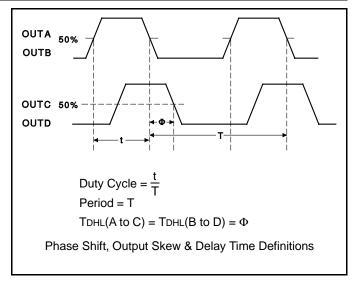

Note 1. Phase shift percentage (0% =  $0^{\circ}$ , 100% = 180°) is defined as

$$\theta = \frac{200}{T} \Phi \%$$

where  $\theta$  is the phase shift, and  $\Phi$  and T are defined in Figure 1. At 0% phase shift,  $\Phi$  is the output skew.

Note 2. Delay time is defined as

$$delay = T \bullet \left(\frac{1}{2} - \text{ duty cycle}\right)$$

where T is defined in Figure 1.

- Note 3. Ramp offset voltage has a temperature coeffecient of about -4mV/°C.

- Note 4. The zero phase shift voltage is the voltage measured at COMP which forces zero phase shift. This condition corresponds to zero effective output power. Zero phase shift voltage has a temperature coeffecient of about -2mV/°C.

- Note 5. Delay time can be programmed via resistors from the delay set pins to ground.

Delay time =

$$[1.04 \cdot 10^{-10} \cdot RDELAY]$$

sec.

The recommended range for RDELAY is 1.9k to 10k.

Figure 1

#### PIN DESCRIPTIONS

CLKSYNC (Bi-directional Clock and Synchronization): Used as an output, CLKSYNC provides a clock signal. As an input, this pin provides a synchronization point. Multiple UC3879s, each with their own local oscillator frequency, may be connected together by the CLKSYNC pin, and they will synchronize to the fastest oscillator. This pin may also be used to synchronize the UC3879 to an external clock, provided the frequency of the external signal is higher than the frequency of the local oscillator. CLKSYNC is internally connected to an emitter follower pull-up and a current source pull-down (300µA typical). Therefore an external resistor to GND can be used to improve the CLKSYNC pin's ability to drive capacitive loads.

COMP (Error Amplifier Output): This pin is the output of the gain stage for overall feedback control. Error amplifier output voltage levels below 0.9 volt forces zero phase shift. Since the error amplifier has a relatively low current drive capability, the output may be overridden by driving it with a sufficiently low impedance source.

CT (Oscillator Frequency Set): After choosing RT to set the required upper end of the linear duty cycle range, the timing capacitor (CT) value is calculated to set the oscillator frequency as follows:

$$CT = \frac{D_{lin}}{1.08 \bullet RT \bullet f}$$

Connect the timing capacitor directly between CT and GND. Use a high quality ceramic capacitor with low ESL and ESR for best results. A minimum CT value of 200pF insures good accuracy and less susceptibility to circuit layout parasitics. The oscillator and PWM are designed to provide practical operation to 600kHz.

CS (Current Sense): This pin is the non-inverting input to the two current fault comparators whose references are set internally to fixed values of 2.0V and 2.5V. When the voltage at this pin exceeds 2.0V, and the error amplifier output voltage exceeds the voltage on the ramp input, the phase shift limiting overcurrent comparator will limit the phase shifting on a cycle-by-cycle basis. When the voltage at this pin exceeds 2.5V, the current fault latch is set, the outputs are forced OFF, and a soft start cycle is initiated. If a constant voltage above 2.5V is applied to this pin the outputs are disabled and held low. When CS

# **PIN DESCRIPTIONS (cont.)**

is brought below 2.5V, the outputs will begin switching at 0 degrees phase shift before the SS pin begins to rise. This condition will not prematurely deliver power to the load.

**DELAYSET A-B, C-D (Output Delay Control):** The user programmed currents from these pins to GND set the turn on delay for the corresponding output pair. This delay is introduced between the turn off of one switch and the turn on of another in the same leg of the bridge to allow resonant switching to take place. Separate delays are provided for the two half-bridges to accommodate differences in the resonant capacitor charging currents.

**EA-** (Error Amplifier Inverting Input): This is normally connected to the voltage divider resistors which sense the power supply output voltage level. The loop compensation components are connected between this pin and COMP.

**GND (Signal Ground):** All voltages are measured with respect to GND. The timing capacitor on CT, and bypass capacitors on VREF and VIN should be connected directly to the ground plane near GND.

**OUT A-OUT D (Outputs A-D):** The outputs are 100mA totem pole output drivers optimized to drive FET driver ICs. The outputs operate as pairs with a nominal 50% duty cycle. The A-B pair is intended to drive one half-bridge in the external power stage and is synchronized to the clock waveform. The C-D pair drives the other half-bridge with switching phase shifted with respect to the A-B outputs.

**PWRGND** (**Power Ground**): VC should be bypassed with a ceramic capacitor from VC to the section of the ground plane that is connected to PWRGND. Any required bulk reservoir capacitor should be connected in parallel. PWRGND and GND should be connected at a single point near the chip to optimize noise rejection and minimize DC voltage drops.

**RAMP (Voltage Ramp):** This pin is the input to the PWM comparator. Connect it to CT for voltage mode control. For current mode control, connect RAMP to CS and also to the output of the current sense transformer circuit. Slope compensation can be achieved by injecting a portion of the ramp voltage from CT to RAMP.

RT (Clock/Sync Duty Cycle Set Pin): The UC3879 oscillator produces a sawtooth waveform. The rising edge is generated by connecting a resistor from RT to GND and a capacitor from CT to GND (see CT pin description). During the rising edge, the modulator has linear control of the duty cycle. The duty cycle jumps to 100% when the voltage on COMP exceeds the oscillator peak voltage.

Selection of RT should be done first, based on the required upper end of the linear duty cycle range (Dlin) as follows:

$$RT = \frac{2.5}{10mA \bullet (1 - Dlin)}$$

Recommended values for RT range from 2.5k to 100k.

**SS:** Connect a capacitor between this pin and GND to set the soft start time. The voltage at SS will remain near zero volts as long as VIN is below the UVLO threshold. Soft start will be pulled up to about 4.8V by an internal 9μA current source when VIN and VREF become valid (assuming a non-fault condition). In the event of a current fault (CS voltage exceeding 2.5V), soft start will be pulled to GND and then ramp to 4.8V. If a fault occurs during the soft start cycle, the outputs will be immediately disabled and soft start must fully charge prior to resetting the fault latch. For paralleled controllers, the soft start pins may be paralleled to a single capacitor, but the charge currents will be additive.

**UVSEL:** Connecting this pin to VIN sets a turn on voltage of 10.75V with 1.5V of UVLO hysteresis. Leaving the pin open-circuited programs a turn on voltage of 15.25V with 6.0V of hysteresis.

**VC** (Output Switch Supply Voltage): This pin supplies power to the output drivers and their associated bias circuitry. The difference between the output high drive and VC is typically 2.1V. This supply should be bypassed directly to PWRGND with a low ESR/ESL capacitor.

VIN (Primary Chip Supply Voltage): This pin supplies power to the logic and analog circuitry on the integrated circuit that is not directly associated with driving the output stages. Connect VIN to a stable source above 12V for normal operation. To ensure proper functionality, the UC3879 is inactive until VIN exceeds the upper undervoltage lockout threshold. This pin should be bypassed directly to GND with a low ESR/ESL capacitor. NOTE: When VIN exceeds the UVLO threshold the supply current (IIN) jumps from about 100μA to greater than 20mA. If the UC3879 is not connected to a well bypassed supply, it may immediately enter the UVLO state again. Therefore, sufficient bypass capacity must be added to ensure reliable startup.

**VREF:** This pin provides an accurate 5V voltage reference. It is internally short circuit current limited. VREF is disabled while VIN is below the UVLO threshold. The circuit is also disabled until VREF reaches approximately 4.75V. For best results bypass VREF with a  $0.1\mu F$ , low ESR/ESL capacitor.