# PJ3401

#### Compact, high efficiency and low voltage step-up DC/DC Converter

#### General Description

The PJ3401 is a compact, high efficiency, and low voltage step-up DC/DC converter with an Adaptive Current Mode PWM control loop. It comprises of an error amplifier, a ramp generator, a PWM comparator, a switch pass element and the driver. It provides stable and high efficient operation over a wide range of load currents without external compensation. The 0.8V start-up input voltage makes PJ3401 suitable for single battery cell applications. The built-in power transistor is able to provide up to 300mA output current while working under Li-Battery Supply. The output voltage is set with two external resistors. The 500KHz high switching rate reduces the size of external components. Besides, the 14µA low quiescent current together with high efficiency maintains long battery lifetime.

#### Features

- Low Quiescent (Switch-off) Supply Current: 14μA

- Low Start-up Input Voltage: typical 0.8V

- High Supply Capability: Deliver 3.3V 100mA with

1Alkaline Cell; 5V 300mA with 1 Li-Cell

Zero Shutdown Mode Supply Current

High efficiency: 90%

Fixed switching frequency: 500KHz

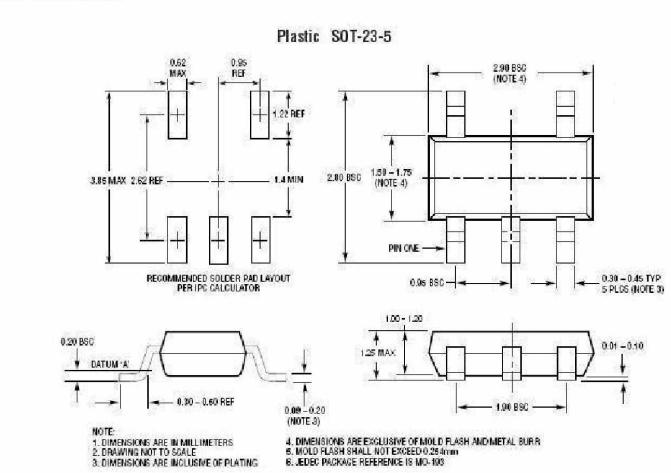

Package type: SOT-23-5

## Application

MP3, PDA, Electronic Dictionary, DSC, LCD, RF-Tag, Portable Devices, Wireless Devices, etc.

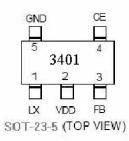

### Pin Assignment

### Pin Description

| Pin No | Symbol | Description                                 |  |

|--------|--------|---------------------------------------------|--|

| 1      | LX     | Output for internal power switch            |  |

| 2      | VDD    | Power Supply                                |  |

| 3      | FB     | Feed back input                             |  |

| 4      | CE     | Enable pin. PT1309 Shut-down when CE is low |  |

| 5      | GND    | Ground                                      |  |

#### Order Information

# PJ3401E23E

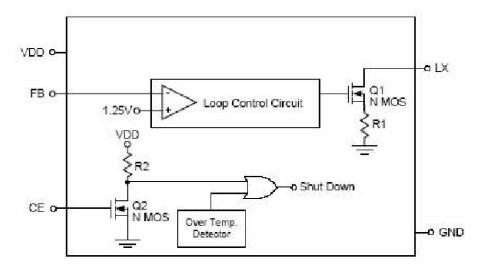

# Block Diagram

**Absolute Maximum Ratings**

| Symbol    | Item                                                            | Rating              | Unit                 |

|-----------|-----------------------------------------------------------------|---------------------|----------------------|

| $V_{DD}$  | Supply Voltage                                                  | -0.3~7.0V           | V                    |

| $V_{LX}$  | LX pin Switch Voltage                                           | -0.3~7.0V           | V                    |

| $V_{IO}$  | Voltage on other I/O pins                                       | -0.3V to (VDD+0.3V) |                      |

| $I_{OUT}$ | LX pin Output Current                                           | 2.5                 | A                    |

| PTR       | Package Thermal Resistance SOT-23-5 $\Theta_{JC}$ $\Theta_{JA}$ | 125<br>256          | °C/W                 |

| Topt      | Operating Temperature Range                                     | -40~125             | $^{\circ}\mathbb{C}$ |

| Tstg      | Storage Temperature Range                                       | -65~150             | $^{\circ}\mathbb{C}$ |

| Tsolder   | Lead Temperature (Soldering)                                    | 260℃, 10s           |                      |

Note: Absolute Maximum Ratings are threshold limit values that must not be exceeded even for an instant under any condition. Moreover, such values for any two items must not be reached simultaneously. Operation above these absolute maximum ratings may cause degradation or permanent damage to the device. These are stress ratings only and do not necessarily imply functional operation below these limits.

#### **Electrical Characteristics**

(V<sub>IN</sub>=1.5V, V<sub>DD</sub>=3.3V, load current=0, TA =25  $^{\circ}\mathrm{C}$  , unless otherwise specified. )

| Symbol                      | Item                                   | Test Condition                                | Min  | Тур  | Max  | Unit                   |

|-----------------------------|----------------------------------------|-----------------------------------------------|------|------|------|------------------------|

| $V_{ST}$                    | Startup Voltage                        | IL = 1mA                                      |      | 0.80 | 1.05 | V                      |

| $V_{DD}$                    | Operating VDD Range                    | V <sub>DD</sub> pin Voltage                   | 2    |      | 6    | V                      |

| $I_{OFF}$                   | Shutdown Current I (V <sub>IN</sub> )  | $V_{CE} = 0V, V_{IN} = 4.5V$                  |      | 0.01 | 1    | μА                     |

| I <sub>SWITCH OFF</sub>     | Switch-Off Current I(V <sub>DD</sub> ) | $V_{IN} = 6V$                                 |      | 14   | 25   | μА                     |

| I <sub>SWITCH</sub>         | Continuous Switching Current           | $V_{IN} = V_{CE} = 3.3V, V_{FB} = GND$        | 0.22 | 0.24 | 0.7  | mA                     |

| I <sub>NO LOAD</sub>        | No Load Current I(V <sub>IN</sub> )    | $V_{IN} = 1.5V, V_{OUT} = 3.3V$               |      | 56   |      | μА                     |

| V <sub>REF</sub>            | Feedback Reference Voltage             | Close loop, V <sub>DD</sub> = 3.3V            | 1.20 | 1.25 | 1.30 | V                      |

| Fs                          | Switching Frequency                    | $V_{DD} = 3.3V$                               |      | 500  |      | KHz                    |

| $D_{MAX}$                   | Maximum Duty                           | $V_{DD} = 3.3V$                               | 85   | 94   |      | %                      |

|                             | On Resistance, LX to V <sub>DD</sub>   | $V_{DD} = 3.3V$                               |      |      | 1.1  | Ω                      |

| I <sub>LIMIT</sub>          | Limit Current                          | $V_{DD} = 3.3V$                               |      | 1.5  |      | A                      |

| $\triangle V_{\text{LINE}}$ | Line Regulation                        | $V_{IN} = 3.5 \sim 6V$ , $IL = 1mA$           |      |      | 5    | mV/V                   |

| $\triangle V_{LOAD}$        | Load Regulation                        | $V_{IN} = 2.5V$ , $IL = 1 \sim 100 \text{mA}$ |      |      |      | mV/mA                  |

|                             | CE trigger Level                       | $V_{DD} = 3.3 V$                              | 0.4  |      | 1.2  | V                      |

| TS                          | Vout Temperature Coefficient           |                                               |      | 100  |      | ppm/℃                  |

| △TSD                        | Thermal Shutdown Hysterises            |                                               |      | 10   |      | $^{\circ}\!\mathbb{C}$ |

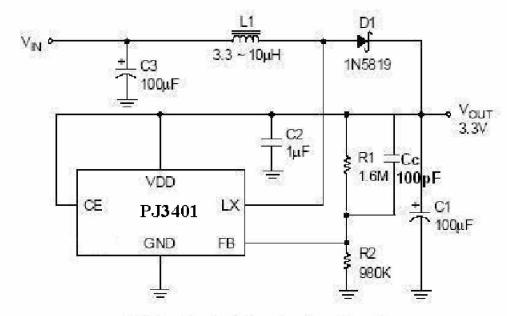

# **Typical Application Circuits**

PJ3401 Typical Application Circuit

Note: Co for better Stability

1.5Vto 3.3V, 100mA Output Current.

#### Application Design Guideline

Output Voltage Setting

Referring to Typical Application Circuit, the output voltage of switching regulator (Vout) is set with following equation:

$$Vout = (1 + \frac{R1}{R2}) \times 1.25V$$

#### Feedback Loop Design

Referring to Typical Application Circuit 1 again, the selection of R1 and R2 is a trade-off between quiescent current consumption and interference immunity besides abiding by the above equation.

- ✓ Higher R reduces quiescent current ( I=1.25V/R2 )

- ✓ Lower R gives better interference immunity, and is less sensitive to interference, layout parasitic, FB node leakage, and improper probing to FB pin.

Hence for applications without standby or suspend modes lower R1 and R2 values are preferred, while for applications concerning the current consumption in standby or suspend modes, higher values of R1 and R2 are needed. Such high impedance feedback loop is sensitive to any interference, which requires careful PCB layout and avoid any interference, especially to FB pin.

To improve the system stability, a proper value capacitor between FB pin and Vout is suggested. An empirical suggestion is around 100pF for M  $\Omega$  feedback resistors and 10nF $\sim$ 0. 1uF for lower R values.

#### PCB Layout Guide

PCB Layout shall follow these guidelines for better system stability:

- ✓ A full GND plane without any gap break.

- ✓ VDD to GND bypass Cap The 1 µ F MLCC noise bypass Cap between pin 5 and pin 3 shall have short and wide connections.

- ✓ Vin to GND bypass Cap Add a Cap close to the inductor when Vin is not an idea voltage source.

- Minimize the FB node copper area and keep it far away from noise sources.

- Minimize the parasitic capacitance connected to LX nodes to reduce the switch loss.

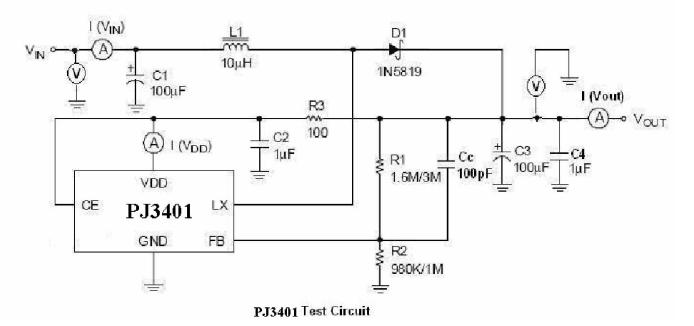

## **Test Circuit**

# **Typical Characteristics**

(Refer to Test Circuit)

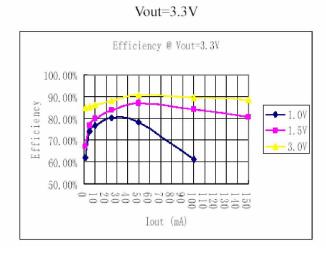

## (1) Efficiency

Vout=5.0V

Efficiency @ Vout=5.0V

100.00%

90.00%

90.00%

60.00%

60.00%

50.00%

30.60.90 15.50.00%

10ut (mA)

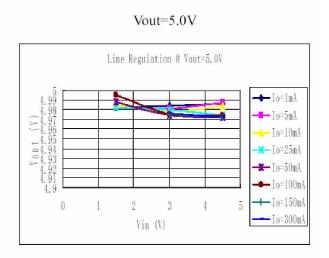

#### (2) Line Regulation

# Typical Characteristics(Contd.)

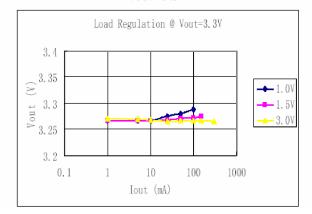

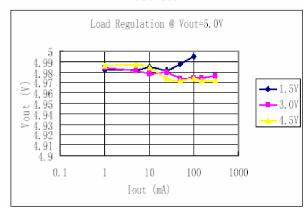

## (3) Load Regulation

Vout=3.3V

Vout=5.0V

## **Outline Dimemsion**