# **Inductor Design Theory**

ACBEL POLYTECH IN

- → 電感器分類

- → 共模電感的工作原理

- → 共模電感器的設計

- → 共模電感器的標準化

## 概述

電感器作為磁性元件的重要組成部分,被廣泛應用於電力電子線路中。尤其在電源電路中更是不可或缺的部分。如工業控制設備中的電磁繼電器,電力系統之電功計量表(電度表)。開關電源設備輸入和輸出端的濾波器,電視接收與發射端之調諧器等等均離不開電感器。電感器在電子線路中主要的作用有:儲能、濾波、扼流、諧振等。

在電源電路中,由於電路處理的均是大電流或高電壓的能量傳遞,故電感器多為"功率型"電感。正是因為功率電感不同於小信號處理電感,在設計時因開關電源的拓撲方式不一樣,設計方式也就各有要求,造成設計的困難。當前電源電路中的電感器主要用於濾波、儲能、能量傳遞以及功率因數校正等。

電感器設計涵蓋了電磁理論,磁性材料以及安規等諸多方面的知識,設計者需對工作情況和相關參數要求(如:電流、電壓、頻率、溫升、材料特性等)有清楚了解以作出最合理的設計。

# 電感器的分類

電感器以其應用環境、產品結構、形狀、用途等可分為不同種類,通常電感器設計是以用途及應用環境作為出發點而開始的。在開關電源中以其用途不同,電感器可分為:

共模濾波電感器 (Common Mode Choke)

常模濾波電感器 (Normal Mode Choke)

功率因數校正電感 (Power Factor Correction - PFC Choke)

交鏈耦合電感器 (Coupler Choke)

儲能平波電感 (Smooth Choke)

磁放大器線圈 (MAG AMP Coil)

共模濾波電感器因要求兩線圈具有相同的電感值,相同的阻抗等,故該類電感均采用對稱性設計,其形狀多為TOROID、UU、ET等形狀。

# **Inductor Design Theory**

## 共模濾波電感器(Common Mode Choke)的設計

共模濾波電感器又稱共模扼流線圈 (以下簡稱共模電感或 CM.M.Choke)或Line Filter。

#### 1. 共模電感的工作原理

在開關電源中,由於整流二极管和濾波電容以及電感中的電流或電壓急劇變化,產生電磁干扰源(noise),同時輸入電源中也存在工頻以外的高次諧波雜訊,這些干扰若不加以扼制,將對負載設備或開關電源本身造成損害,因此若干國家之安規機構對電磁干扰(EMI)發射量均作出了相應的管制規定。當前開關電源的開關頻率日趨高頻化EMI也隨之日益嚴重,所以開關電源中均須設置EMI濾波器,EMI濾波器需對常模及共模雜訊均作出相應的抑制,以達到某一規定標準。常模濾波器負責濾出輸入或輸出端兩根線間之差模干擾信號,共模濾波器負責濾出兩條入線之共模干擾信號。實際共模電感因其工作環境不同,又可分為AC CM.M.CHOKE;DC CM.M. CHOKE和SIGNAL CM.M.CHOKE三種,在設計或選用時應於以區分。但其工作原理完全相同,

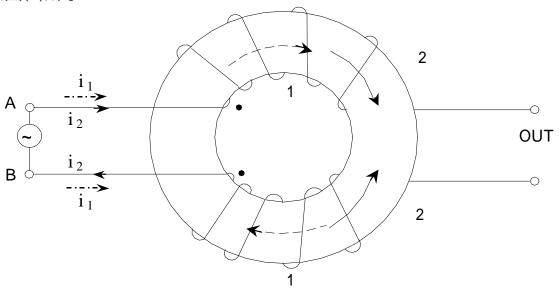

工作原理如圖(1)所示:

圖 1 共模電感的作用

如圖所示,在同一磁環上繞上兩組方向相反的線圈,據右手螺旋管定則可知,當在輸入端 A、B兩端加上极性相反,信號幅值相同的差模電壓時,有實線所示的電流 i<sub>2</sub>,在磁芯中產生實線 所示的磁通 2,只要保證兩繞組完全對稱,則磁芯中兩不同方向之磁通相互抵消。總磁通為零, 線圈電感幾乎為零,對常模信號無阻抗作用。若在輸入端A、B兩端加上极性相同,幅值相等的 共模信 號時,有虛線所示的電流 i1,在磁芯中產生虛線所示的磁通 1,則磁芯中磁通有相同的方向而互相加強,使每一線圈的電感值為單獨存在時的兩倍,而  $X_L = L$ ,因此,此一繞法的線圈對共模干擾有很強的抑制作用。

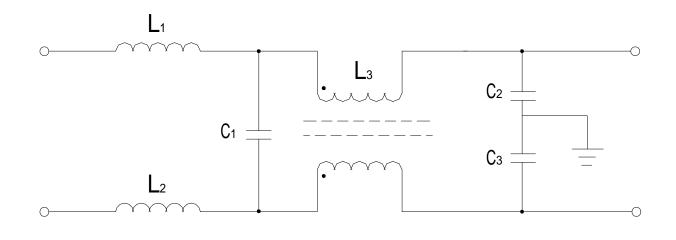

實際的EMI濾波器由L、C組合而成,設計時也常常將差模與共模抑制電路組合在一起(如圖 2),因此,設計時需依據濾波電容的大小以及所需符合的安規標準作出電感值的決定。 圖中L1、L2、C1構成常模濾波器,L3、C2、C3構成共模濾波器。

圖 2 EMI濾波器電路

### 2. 共模電感器的設計

在設計共模電感之前,首先要考量線圈須行符合以下原則:

- 1>正常工作狀態下,不致因通電電源電流而造成磁芯飽和。

- 2>對高頻干擾信號要有足夠大的阻抗,且有一定的頻寬,而對工作頻率之信號電流有最小的阻抗。

- 3>電感的溫度系數應小,而分布電容宜小。

- 4>直流電阻應盡量小。

- 5>感應電感應盡量大,電感值需穩定。

- 6>繞組間之絕緣性須滿足安規要求。

## 共模電感器之設計步驟:

Step 0 SPEC取得: EMI允許級別, 應用位置。

Step 1 電感值確定。

Step 2 core材質及規格確定。

Step 3 繞組匝數及線徑確定。

Step 4 打樣

Step 5 測試

## 3. 設計舉例

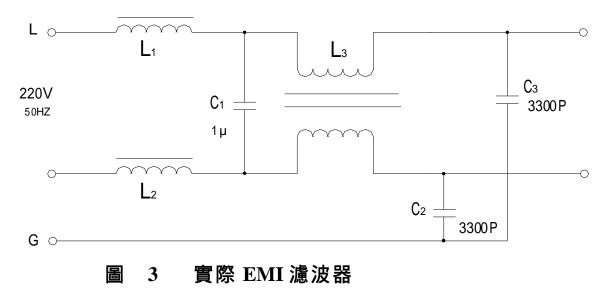

Step 0: 如圖3所示EMI濾波電路

Cx = 1.0 Uf Cy = 3300 PF EMI等級: Fcc Class B

Type: Ac Common Mode Choke

由電路圖可知共模信號由L3和C2、C3組成的共模濾波器抑制,實際L3與C2和C3構成兩路LC串聯電路,分別吸收L和N線上的雜訊。只要確定濾波電路的截止頻率,也已知電容容量C,則可以下式求出電感 L。

$$f_0 = 1/(2$$

LC) — L = 1/(2  $f_0$ )  $^2$ C

通常EMI測試頻寬如下:

傳導干擾: 150KHZ → 30MHZ (注: VDE標準 10KHZ - 30M)

輻射干擾: 30MHZ → 1GHZ

實際的濾波器無法達到理想濾波器那樣陡峭的阻抗曲線,通常可將截止頻率設定在 $50 \mathrm{KHZ}$ 左右。在此,假設  $\mathrm{f}_{o} = 50 \mathrm{KHZ}$ ,則

$$L = 1/(2 - f_0)^2 C = 1/[(2*3.14*50000)^2*3300*10^{-12}] = 3.07 \text{mH}$$

L1、L2、C1組成(低通)常模濾波器,線間電容有1.0uF,則常模電感為:

$$L = 1/[(2*3.14*50000)^2*1*10^{-6}] = 10.14uH$$

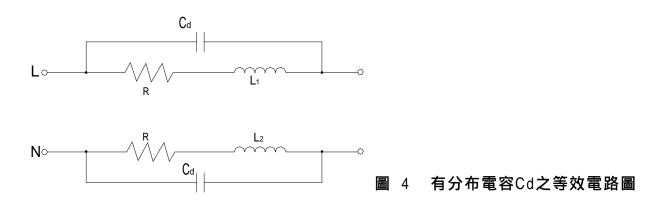

如此,可得到理論要求的電感值,若想獲得更低的截止頻率 fo ,則可進一步加大電感值,截止頻率一般不低於10KHZ。理論上電感量越高對EMI抑制效果越好,但過高的電感將使截止頻率更低,而實際的濾波器只能做到一定帶寬,也就使高頻雜訊的抑制效果變差(一般開關電源的雜訊成分約為5~10MHZ間,但也有超過10MHZ之情形)。另外,電感量愈高,則繞線匝數愈多,或CORE之wi越高,如此將造成低頻阻抗增加(DCR變大)。匝數增加使分布電容也隨之增大(如圖4),使高頻電流全部經此電容流通。過高的wi使CORE极易飽和,同時制作也极困難,成本也較高。

#### Step 2 CORE材質及SIZE確定

從前述設計要求中可知,共模電感器需不易飽和,如此就需要選擇低B-H角形比之材料,因需要較高的電感值,磁芯的ui值也就要高,同時還必須有較低的磁芯損耗和較高的Bs值,符合上述要求之CORE材質,目前以Mn-Zn 鐵氧體材料CORE最為合適。

COEE SIZE在設計時並無一定的規定,原則上只要符合所需電感量,且在允許的低頻損耗範圍內,以所設計的產品體積最小化即可。

因此,CORE材質及SIZE選取應以成本、允許損耗、安裝空間等作考量。共模電感常用CORE之ui約在2000~10000之間。Iron Powder Core 也有低的鐵損,高的Bs和較低的B-H角形比率,但其ui較低,故一般不被應用於共模電感,而該類磁芯卻是常模電感器之優選材料。

#### Step 3 確定匝數N和線徑dw

首先確定CORE之規格,如本例采用T18\*10\*7、A10、AL = 8230±30%,則:

$$N = L/AL = (3.07*10^6)/(8230*70\%) = 23 TS$$

線徑以電流密度 3~5A/mm²為選擇原則,若空間允許可選擇盡量低的電流密度。

假設本例輸入電流  $I_i = 1.2A$ , 取  $J = 4 A / mm^2$

$$Aw = 1.2 / 4 = 0.3 \text{ mm}^2$$

$0.70 \, \mathrm{mm}$

實際的共模電感還必需通過實做樣品進行測試,方可確認設計之可靠性,因為制作工藝的差異也將導致電感參數的差異而影響濾波效果,如分布電容的增加,將使高頻雜訊更易傳遞,兩繞組的不對稱性,使兩組感量差異變大,對常模信號形成一定阻抗。

### 4. 小結

- 1 > 共模電感器的作用是濾除線路中的 共模雜訊,設計時要求兩繞組具有完全對稱的結構,電參數相同。

- 2>共模電感的分布電容對抑制高頻雜訊有負面影響,應盡量減小。

- 3 > 共模電感的感值與須濾除的雜訊 頻帶及配合電容容量有關,通常感值在 2mH ~ 50 mH之間。