# **N-Channel MOSFET**

# Rev. 2.01 – April 2007 SAMWIN SOUTH Semiconductors

# **SAMWIN**

<u>Semiconductors</u> <u>Qualpack</u>

# 1. Content

| 1. Content                         |    |

|------------------------------------|----|

| 1. Content                         |    |

| 2. General Information             |    |

| 3. Technology Information          | 3  |

| 3.1 Wafer Process Technology       | 3  |

| 3.2 Package Technology             |    |

| 3.2.1 Package Information          |    |

| 3.2.2 Other available packages     | 5  |

| 3.3 Test                           |    |

| 3.4 Wafer Process Control          |    |

| 3.5 Assembly Process Control       | 8  |

| 3.6 OQC(Out-going Quality Control) |    |

| 4. Qualification                   |    |

| 4.1 Change Procedure               | 13 |

| 4.2 Qualification Flow             |    |

| 5. Package Dimensions              |    |

| 6. User Information                |    |

| 7. Environmental Information       |    |

| 8. Other Data                      |    |

| 8.1 Approval Certificate           |    |

| 8.2 Datasheet Reference            |    |

| 8.3 Address Reference              |    |

| Remarks:                           | 22 |

# **SAMWIN**

Semiconductors Qualpack

| Semiconductors                       | Qual                                                      | <u>pack</u> |

|--------------------------------------|-----------------------------------------------------------|-------------|

| 2. General Informat                  | tion                                                      |             |

| Product Name:                        | For All Products                                          |             |

| Function:                            | N-Channel MOSFET                                          |             |

| Wafer process:                       | 0.8um VDMOS                                               |             |

| Available plastic packag             | ge types: TO-92 TO-251(252) TO-220(F)                     |             |

| Locations:                           |                                                           |             |

| Product development                  | Samwin South Semiconductors, ShenZhen, China              | Samwin      |

| Wafer plant                          | Silan Semiconductor,Hangzhou, China<br>CSMC               | F1<br>F2    |

| QC responsibility                    | Samwin                                                    |             |

| Assembly                             | Huanshan Electronics, ShanTou, China (TO-220/F, TO-92) A1 |             |

|                                      | Mingxing Electronics, Wuxi, China (TO-251, TO-252)        | А3          |

|                                      | Changjiang Electronics, Jiangying, China (TO-92)          | <b>A2</b>   |

| Probe test                           | F1,F2                                                     |             |

| Final test                           | Huanshan Electronics, ShanTou, China (TO-220/F, TO-92)    |             |

|                                      | Mingxing Electronics, Wuxi, China (TO-251, TO-252)        |             |

| O                                    | Changjiang Electronics, Jiangying, China (TO-92)          |             |

| Quality Assurance                    | Samwin                                                    |             |

| Reliability testing Failure analysis | Samwin, F1<br>Samwin, F1,F2,A1,A2,A3                      |             |

| i allule allalysis                   | Janwin, 1 1,1 2,4 1,42,43                                 |             |

|                                      | Quality Assurance Mana                                    | gement      |

Signed.....

3. Technology Information

# 3.1 Wafer Process Technology

Process type (Name): 0.8um VDMOS

Base material: Silicon

Wafer Thickness (final) XXXµm

Wafer diameter XXXmm

Number of masks XXX

Gate oxide

Material Silicon oxide

Thickness XXXXA

Polysilicon

Number of layers

Thickness XXXXA

Metal

Number of layers 1

Layer 1 material AL

Passivation NONE

## 3.2 Package Technology

#### 3.2.1 Package Information

TO-92 TO-251(252) TO-220(F)

Package weight 0.2 g 2.05g (2.2g)

Chip separation method Sawing

Lead frame

Material Bar Cu

Type TO-92DT(H) KFC-30 SANSUNG TSP

Lead plating Electroplated Sn/100

Die attach Silver paste Soft Solder Soft Solder

Material Pb/Sn/Ag 93.5/5/1.5

Type DAD-87

Wire bonding

Material AU wire AL wire AL wire

Diameter 0.8mil(G) 0.8×2mil(s) 6mil (G) 10mil(s) 6mil(G) 10mil (S)

Method Ultrasonic

Molding

Material EPOXY

Type SI-7200DX2 EK5600H SI-7200DX2

(HF) KL-G200 (HF) EK5600G (HF)SG8200DS/8300DS

Flammability rating UL94 V-0

Marking

Method Laser Print

Coding (Example: SW 7N60)

YYWW (process code include date info.)

Dry packing None

Tape packed TO-92 TO-251(252) TO-220(F) **Primary** Box Tube (Tape) **Tube** Material Tape paper **Antistatic PVC Antistatic PVC** 2000 Number per unit 80 (2500)50 Box

Secondary

Box

-- --

Material

Cardboard

-- --

Number per unit

30000

32000 (20000)

8000

# **SAMWIN**

<u>Semiconductors</u> <u>Qualpack</u>

Labeling (minimum)

Device type, Quantity, Date Code, Prod. code

Bar coding Code 39 to EIA-556-A

3.2.2 Other available packages

Other package available: TO-126, TO-263

3.3 Test

Probe equipment VR/30A KE

Probe temperature  $25\pm2^{\circ}$ C

Final Test equipment 881-TT TESEC

DTS-1000 JUNO

Final Test temperature  $25\pm2^{\circ}$ C

# <u>Semiconductors</u>

#### 3.4 Wafer Process Control

All the inspections and controls are defined as a process step in the production management control system. PC system could be summarized as follows:

#### MATERIAL RECEIPT

Critical raw materials received

#### **INCOMING INSPECTION**

Raw materials inspected against SAMWIN procurement specifications.

## WAFER FABRICATION

Raw wafers are processed through diffusion, photolithography, implant, thin films, and EPI.

#### **QUALITY CONTROL**

- A) Critical Dimensions

- B) Oxide Thickness

- C) Thin Film Thickness

- D) Sheet Resistivity

- E) Reflectivity

- F) CV Drift

- G) Mask Alignment

- H) Particles

- I) Etch Completion

- J) Visual Defect

#### WAFER ACCEPTANCE

- A) Visual Each wafer is visually inspected under a microscope for defects, mask alignment, and mask sequence.

- B) Parametric Test Four specially designed test sites on each wafer are tested for process and product parameters to verify processing integrity.

#### 100% DIE ELECTRICAL TEST

All die are 100% tested for functionality and parameter conformance. Yields used for process, design, and test analysis.

# DIE ELECTRICAL TEST

Visual Inspection for:

- A) Process Defects

- B) Probe Scratches or Other Damage

- C) Electrical Test Anomalies

- D) Correct Probe Marks

SHIP WAFERS TO CONTRACTED ASSEMBLY

Critical process parameters are identified by using F.M.E.A. and other advanced tools. Specific steps of wafer process quality control are defined as hereafter:

# 3.5 Assembly Process Control

```

SHIP WAFERS TO CONTRACTED ASSEMBLY

100% WAFER SAW

QUALITY CONTROL

A) 100% Saw through and clean.

B) RI Wafer Resistivity

C) Kerf Width

D) Chips and Cracks

OPTICAL INSPECTION

Re. MIL-STD 883C Method 2010.8 Condition B

LTPD = 5%

DIE MOUNT

Visual inspection (4 dice 1X/ Machine/ Shift, 20 units, Acc = 0, Rej = 1)

Criteria:

A) Scratches, Cracks on Die

B) Die Placement, Orientation

C) Stray Epoxy

D) Die Mount Cure: 175 \pm 5°C/ 1Hr.

LEAD BONDING

QUALITY CONTROL

LTPD = 5\%

EQUIPMENT TESTING: Bond Strength tested once per shift. Minimum grams for 1mil.=3

grams.

OPTICAL INSPECTION: Re. MIL-STD 750D Method 2037 Condition C

Criteria:

A) Missing Die

B) Missing Wires

C) Poor Lead Dress

D) Conductive Contamination

```

# <u>Semiconductors</u>

#### MOLD

Post Mold Cure – 175 ± 5°C/6 Hr.

#### **QUALITY CONTROL**

(4X/Shift, 20 units, Acc = 0, Rej = 1)

Criteria:

- A) Deflash

- B) Package Voids

- C) Bubbles, Blisters

#### TRIM & FORM LEADS

#### **QUALITY CONTROL**

(4X/Shift, 20 units, Acc = 0, Rej = 1)

Criteria:

- A) Lead Defects

- B) Burrs or Incomplete Trim

- C) Mold Flash

#### LEAD SOLDER PLATING OR SOLDER DIPPING

#### QUALITY CONTROL: SOLDER DIP/SOLDER PLATE

LTPD = 5%

Criteria:

- A) Missing Plating

- B) Extraneous Solder

- C) Flaking, Peeling

## **QUALITY CONTROL: SOLDER THICHNESS**

X-ray fluoroscopy on 5 units/lot

Solder Dip = 200 micro inch minimum

Solder Plate = 300 micro inch minimum

#### QUALITY CONTROL: SOLDERABILITY

Re. MIL-STD 750D Method 2026.10 - 6 units

Criteria:

- A) 100% Coverage on Functional Area of Lead

- B) Solder Bridging, Lump, Ball

- C) Contamination

# Semiconductors

# Every unit tested for conformance to all guaranteed datasheet parameters ELECTRICAL TEST (25°C)

100% production tested to guarantee an outgoing electrical AQL of 0.1% for guaranteed electrical parameters.

MARK

#### QUALITY CONTROL: MARK PERMANENCY

Re. MIL-STD 883C Method 2015 (2X/Shift, 22 units, Acc = 0, Rej = 1)

## FINAL VISUAL INSPECTION

#### **QUALITY CONTROL**

AQL = .025%

Criteria:

- A) Marking Defects

- B) Lead Defects

- C) Package Defects

#### PACK AND SHIP TO SAMWIN

# 3.6 OQC(Out-going Quality Control)

#### PACK AND SHIP TO SAMWIN

#### INCOMING INSPECTION

Criteria:

- A) Check Mark Quality and Permanency Re. MIL-STD750D Method

- B) Check Lead Form and Plating Quality

- C) Check Solderability

- D) Check for any Gross Package or Lead Deformities

#### INCOMING ELECTRICAL TEST (HOT)

Test all parameters guaranteed by the datasheet at temperature. AQL=0.1%

#### **ELECTRICAL TEST (HOT)**

Sample pulled Re. MIL-STD 105D to guarantee an AQL level of 0.1% minimum for HOT Test parameters.

#### PRODUCTION VISUAL INSPECTION

Every unit checked for correct marking, orientation, and any package defects obtained during assembly, test, or production conditioning.

#### **QUALITY CONTROL**

A sample is pulled Re. MIL-STD 105D to guarantee an AQL of 0.1% for visually reject able defects.

#### PRODUCTION PRODUCT LABELING

#### **QUALITY CONTROL**

Each sub-lot examined by QA to verify conformance to standards. The review includes:

- A) Reliability Life Test Data checked.

- B) Humidity Performance checked

- C) ESD Sensitivity check per product per wafer fab process

- D) Labeling and Device Marking checked

# FINISHED GOOD STORES

Product stored with finished goods disposition form attached detailing the product's store classification.

## SHIPPING PREPARATION

Product packaged using approved anti-static and Faraday shielding materials.

#### **QUALITY CONTROL**

Criteria:

- A) Labeling Correct

- B) Packaging and Preparation for Shipment Correct

- C) Quantities Correct

SHIPMENT

#### 4. Qualification

All product qualifications are split into three distinct steps as shown above. This same procedure is also used to qualify a change. Before a product is released for use, it must have been manufactured using a qualified wafer and package process. Before a device is released for production processing, it must also have successfully completed its required specific qualification.

The standard tests which are used for this procedure are shown in the section "Qualification Flow"

#### 4.1 Change Procedure

All changes are controlled by ECN (Engineering Change Notice). All major changes are notified to those customers using products which are affected by the change.

A major change is defined as a change which affects the electrical and/or mechanical specification as defined in the datasheet or which affects the following parameters as defined hereafter:

- 1 General Major Changes

- 1-1 Manufacturing line

- 1-2 Sequence of fabrication process cycle

- 1-3 Material

- 1-4 Electrical parameters

- 1-5 Dimensions

- 1-6 Pad location

- 1-7 Die size

- 2 Changes specific to wafer fabrication area

- 2-1 Doping process

- 2-2 Oxide formation method

- 2-3 Equipment change

- 2-4 Layer thickness

- 2-5 Module dimensions

- 3 Changes specific to assembly process area

- 3-1 Sawing process

- 3-2 Die attach process

- 3-3 Wire interconnect method

- 3-4 Molding process

- 3-5 Tinning process

- 4 Changes specific to test area

- 4-1 Specification limit

- 4-2 Test coverage reduction

- 4-3 Product identification

- 4-4 Final conditioning

# 4.2 Qualification Flow

# **General Requirements for Plastic packaged MOSFET:**

|   | Description                                 | Test Condition                                                                           | Qualification type | Re. Standard                   | Acceptance |

|---|---------------------------------------------|------------------------------------------------------------------------------------------|--------------------|--------------------------------|------------|

| 1 | Temperature<br>Cycle Test                   | TA = -55 °C <-> 25 °C <-> +150°C (air to air), t = 15 - 5 -15 min. / cycle, Bias = None. | 1000 Cycles        | Mil-Std-750D<br>Method 1051    | 0/3 x 28   |

| 2 | Pressure<br>Cooker Test                     | TA = 121 °C +/- 2 °C,<br>RH = 100%, P =<br>15PSIG, Bias = None                           | 168 Hours          | Mil-Std-202F                   | 0/3 x 28   |

| 3 | High<br>Temperature<br>Reverse Bias<br>Test | TA = +150/175°C,<br>Reverse Bias =<br>Specification Limit X<br>0.8.                      | 1000 hours         | MIL-STD-750D,<br>method 1042.3 | 0/3 x 28   |

| 4 | High<br>Temperature<br>Gate Bias<br>Test    | TA = +150/175°C,<br>Reverse Bias =<br>Specification Limit X<br>0.8.                      | 1000 hours         | MIL-STD-750D,<br>method 1042.3 | 0/3 x 28   |

| 5 | Power Cycle<br>Test                         | TA = +25 °C <-> +125 °C, Power Dissipation = ~2.5 Watts                                  | 3000 Cycles        | MIL-STD-750D,<br>method 1037.2 | 0/3 x 28   |

| 6 | Scanning acoustic microscope                |                                                                                          |                    | MIL-STD-750D,<br>method 2077.3 | 0/3 x 50   |

# 5. Package Dimensions

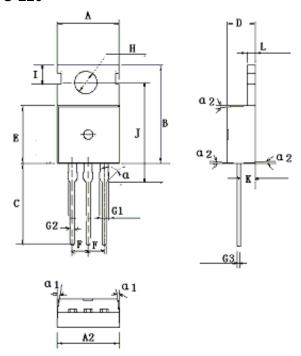

TO-220

| A(mm)      | 9.66~10.28   |

|------------|--------------|

| A2(mm)     | 9.80~10.20   |

| B(mm)      | 15.6~15.8    |

| C(mm)      | 12.70~14.27  |

| D(mm)      | 4.30~4.70    |

| E(mm)      | 8.59~9.40    |

| F(mm)      | typical 2.54 |

| G1(mm)     | 1.32~1.72    |

| G2(mm)     | 0.70~0.95    |

| G3(mm)     | 0.4~0.60     |

| H(mm) dia. | 3.50~3.83    |

| l(mm)      | 2.7~2.9      |

| J(mm)      | 15.70~16.25  |

| K(mm)      | 2.20~2.90    |

| L(mm)      | 1.15~1.40    |

| a(degree)  | 45°          |

| a2(degree) | 3°±0.5°      |

| a3(degree) | 3°±0         |

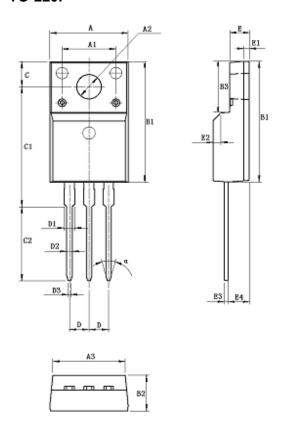

# TO-220F

| A(mm)                                   | 10.16        | ±0.20 |

|-----------------------------------------|--------------|-------|

| A1(mm)                                  | 7.00         |       |

| A2(mm)dia.                              | 3.18±0.10    |       |

| A3(mm)                                  | 9.46:        | ±0.20 |

| B1(mm)                                  | 15.87        | ±0.20 |

| B2(mm)                                  | 4.70:        | ±0.20 |

| B3(mm)                                  | 6.68:        | ±0.20 |

| C(mm)                                   | 3.30±0.10    |       |

| C1(mm)                                  | 15.80±0.20   |       |

| C2(mm)                                  | 9.75±0.20    |       |

| D(mm)                                   | typical 2.54 |       |

| D1(mm)                                  | 1.47(MAX)    |       |

| D2(mm)                                  | 0.80±0.10    |       |

| D3(mm)                                  | 0.35±0.10    |       |

| E(mm)                                   | 2.54±0.20    |       |

| E1(mm)                                  | 0.70         |       |

| E2(mm)                                  | 1.0×45°      |       |

| F2(:::::::::::::::::::::::::::::::::::: | 0.5          | +0.10 |

| E3(mm)                                  |              | -0.05 |

| E4(mm)                                  | 2.76±0.20    |       |

| α(degree)                               | 30°          |       |

**SAMWIN**

# Semiconductors

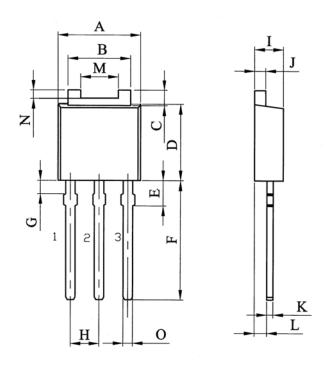

TO-251

| A(mm) | 6.4-6.8   |

|-------|-----------|

| B(mm) | 4.8-5.53  |

| C(mm) | 0.9-1.3   |

| D(mm) | 5.9-6.3   |

| E(mm) | 1.8-2.3   |

| F(mm) | 8.9-10.1  |

| G(mm) | 1.2-1.53  |

| H(mm) | 2.2-2.4   |

| l(mm) | 2.1-2.5   |

| J(mm) | 0.4-0.99  |

| K(mm) | 0.4-0.6   |

| L(mm) | 0.9-1.1   |

| M(mm) | 3.6-4.0   |

| N(mm) | 0.4-0.6   |

| O(mm) | 0.66-0.92 |

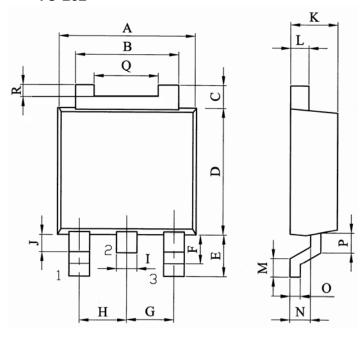

TO-252

| A(mm) | 6.4-6.8   |

|-------|-----------|

| B(mm) | 4.8-5.53  |

| C(mm) | 0.9-1.3   |

| D(mm) | 5.9-6.3   |

| E(mm) | 2.3-2.9   |

| F(mm) | 1.8-2.2   |

| G(mm) | 2.2-2.4   |

| H(mm) | 2.22.4    |

| l(mm) | 0.660.92  |

| J(mm) | 0.6-0.95  |

| K(mm) | 2.1-2.5   |

| L(mm) | 0.4-0.6   |

| M(mm) | 0.80-1.4  |

| N(mm) | 0.9-1.1   |

| O(mm) | 0.4-0.6   |

| P(mm) | 0.81-1.01 |

| Q(mm) | 3.6-4.0   |

| R(mm) | 0.4-0.6   |

|       |           |

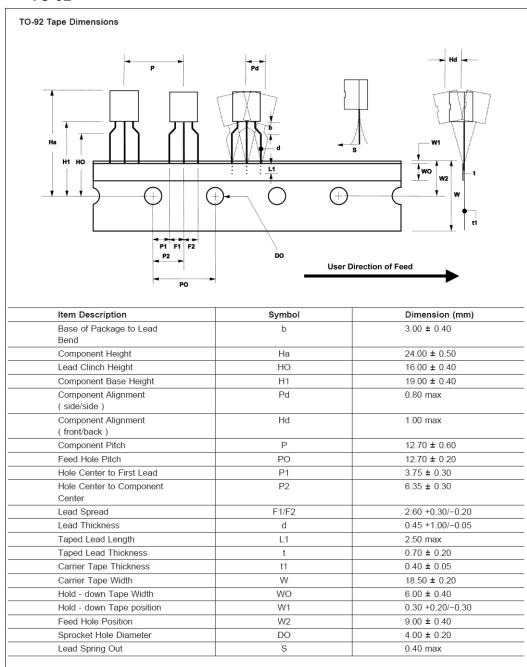

#### **TO-92**

#### 6. User Information

The user must protect components against EOS and ESD damages by grounding personal and workstations.

#### 7. Environmental Information

The SAMWIN Environmental Policy aims at:

- Reducing the use of harmful chemicals in its processes

- Reducing the content of harmful materials in its products

- Using re-cyclable materials wherever possible

- Reducing the energy content of its products

As part of that plan, Ozone Depleting Chemicals are being replaced either by SAMWIN or its subcontractor's processes.

## 8. Other Data

# 8.1 Approval Certificate

**FAB ISO 9001**

**Assembly ISO 16949**

Assembly ISO 14001

Assembly ISO 2000

**Assembly PHILIPS Semiconductors Certificate**

TO-220 SGS report 2006.Aug

TO-220F SGS report 2006.Aug

#### 8.2 Datasheet Reference

Direct access on the web to datasheet at:

http://www.samwinsemi.com

#### 8.3 Address Reference

All enquiries relating to this document should be addressed to the following:

Samwin South Semiconductors 2005, A Building, Cyber Times, Tianan Cyber Park, Futian District, Shenzhen, China Telephone (86) 755 83391818 Telefax (86) 755 83476838

#### Remarks:

The information given in this document is believed to be accurate and reliable. However, no responsibility is assumed by SAMWIN for its use. No specific guarantee or warranty is implied or given by this data unless agreed in writing elsewhere.

SAMWIN reserve the right to update or modify this information without notification, at any time, in the interest of providing the latest information.