# SWITCHING MODE LED DRIVER

#### **DESCRIPTION**

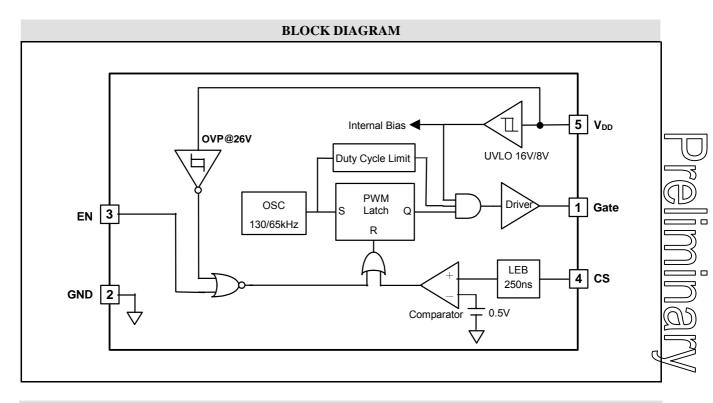

The A704 is a PWM high efficiency LED driver controller. The LED string is driven at constant current rather than constant voltage, thus providing constant light output and enhanced reliability.

#### **FEATURES**

- Low Startup Current (5uA in typical).

- Low Operating Current (3mA in typical).

- Lead-Edge Blanking.

- Internal OVP Detected.

- 150°C OTP Sensor with Hysteresis.

- Under Voltage Lockout (UVLO).

- Fixed PWM Frequency.

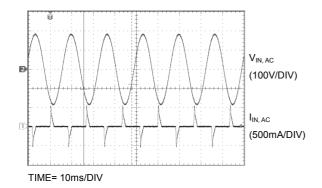

- PFC > 0.9 with Suitable External Components.

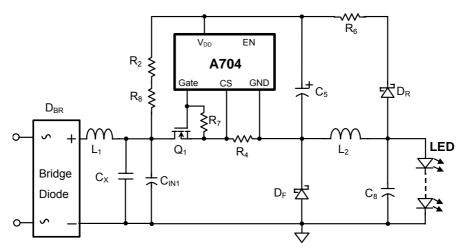

# TYPICAL APPLICATION CIRCUIT

# R<sub>1</sub> R<sub>2</sub> A704 Gate CS GND C<sub>2</sub> Note C<sub>3</sub> C<sub>1</sub> C<sub>1</sub> C<sub>2</sub> C<sub>1</sub> C<sub>2</sub> C<sub>2</sub> C<sub>3</sub> C<sub>1</sub> C<sub>2</sub> C<sub>2</sub> C<sub>3</sub> C<sub>4</sub> C<sub>5</sub> C<sub>6</sub> C<sub>7</sub> C<sub>1</sub> C<sub>2</sub> C<sub>3</sub> C<sub>4</sub> C<sub>4</sub> C<sub>5</sub> C<sub>6</sub> C<sub>7</sub> C<sub>1</sub> C<sub>1</sub>

\*Note:  $C_S$  **MUST** be very close to A704's  $V_{DD}$  pin and GND pin. Please refer to ADDtek's reference layout.

#### **APPLICATIONS**

- B22, E27 lamp device

- General purpose lighting

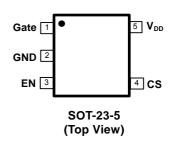

# PACKAGE PIN OUT

#### **ORDER INFORMATION**

SOT-23-5 5 pin

A704WFT

Note: The letter "F" is marked for Lead Free parts, and letter "T" is marked for Tape & Reel.

| ABSOLUTE MAXIMUM RATINGS (Note)                        |                |  |  |  |

|--------------------------------------------------------|----------------|--|--|--|

| Input Voltage, $V_{DD}$                                | 32V            |  |  |  |

| Operating temperature                                  | -20°C ~85°C    |  |  |  |

| Maximum Operating Junction Temperature, T <sub>J</sub> | 150°C          |  |  |  |

| Storage Temperature Range                              | -65°C to 150°C |  |  |  |

| Lead Temperature (Soldering, 10 seconds)               | 260°C          |  |  |  |

Note: Exceeding these ratings could cause damage to the device. All voltages are with respect to Ground. Currents are positive into, negative out of the specified terminal.

| PIN DESCRIPTION |                                                        |  |  |  |

|-----------------|--------------------------------------------------------|--|--|--|

| Pin Name        | Pin Function                                           |  |  |  |

| Gate            | Drives the gate of the external MOSFET.                |  |  |  |

| GND             | Power Ground Pin.                                      |  |  |  |

| EN              | Enable Pin.                                            |  |  |  |

| CS              | Current Sense Pin                                      |  |  |  |

| $V_{DD}$        | Input Power Supply Pin and Over Voltage Protected Pin. |  |  |  |

| THE | $\mathbf{D}\mathbf{M}$ | AT           | $\mathbf{n}$ | TA           |

|-----|------------------------|--------------|--------------|--------------|

|     |                        | $\mathbf{A}$ | IIA          | $\mathbf{H}$ |

Thermal Resistance from Junction to Ambient,  $\theta_{JA}$  TBD °C /W

Junction Temperature Calculation:  $T_J = T_A + (P_D \times \theta_{JA})$ .

The  $\theta_{\scriptscriptstyle JA}$  numbers are guidelines for the thermal performance of the device/pc-board system.

Connect the ground pin to ground using a large pad or ground plane for better heat dissipation.

All of the above assume no ambient airflow.

# **Maximum Power Calculation:**

$$P_{D(MAX)} = \frac{T_{J(MAX)} - T_{A(MAX)}}{\theta_{IA}}$$

T<sub>J</sub>(°C): Maximum recommended junction temperature

T<sub>A</sub>(°C): Ambient temperature of the application

$\theta_{JA}(^{\circ}C/W)$ : Junction-to-Ambient thermal resistance of the package, and other heat dissipating materials.

# **ELECTRICAL CHARACTERISTICS**

$V_{DD}$ =20 $V_{DC}$ ,  $C_{Load}$ =1nF,  $R_{Load}$ =2.2  $\Omega$  in series,  $T_A$ =25°C, unless otherwise noted.

| Description & Conditions              | Parameter             | Conditions                                                 | Min | Тур | Max | Unit            |   |

|---------------------------------------|-----------------------|------------------------------------------------------------|-----|-----|-----|-----------------|---|

| Input Supply Voltage                  | $V_{\mathrm{DD}}$     |                                                            | 6.5 |     | 32  | V               |   |

| Input Supply Current                  | $I_{DD}$              | After start-up, V <sub>DD</sub> =20V                       |     | 3   | 5   | mA              |   |

| Input Quiescent Current               | $I_{QC}$              | Before start-up, V <sub>DD</sub> =15V                      |     | 5   | 30  | uA              |   |

| Input Shutdown Current                | $I_{\mathrm{SD}}$     | $V_{DD}$ pin, after start-up. $V_{DD}$ =20V, $V_{EN}$ =Low |     | 1   | 2   | mA              |   |

| Under-Voltage Lockout, Turn On        | V <sub>UVLO,ON</sub>  |                                                            | 16  | 17  | 18  | V               |   |

| Under-Voltage Lockout, Turn Off       | V <sub>UVLO,OFF</sub> |                                                            | 6   |     | 8   | V               |   |

| Over-Voltage Protection               | V <sub>OVP</sub>      | V <sub>DD</sub> pin                                        | 26  |     |     | V               |   |

| Current Sense Voltage                 | V <sub>CS</sub>       |                                                            | 485 | 500 | 515 | mV              |   |

| Enable Input Logic "High"             | V <sub>IH</sub>       |                                                            | 2.2 |     | 6   | V               |   |

| Enable Input Logic "Low"              | V <sub>IL</sub>       |                                                            | 0   |     | 0.8 | V               | L |

| Oscillator Maximum Duty Cycle         | $D_{MAX}$             |                                                            |     |     | 50  | %               |   |

| Leading Edge Blanking                 | $t_{ m LEB}$          |                                                            | 150 | 200 | 250 | nS              | E |

| CS to Gate Pin Delay Time             | $t_{\mathrm{PD}}$     | CS="1", Gate="0"                                           |     | 50  | 75  | nS              | ( |

| Minimum Turn-ON Time                  | t <sub>ON,MIN</sub>   |                                                            | 300 |     |     | nS              | Ē |

| Thermal Shutdown Temperature          | $T_{SD}$              |                                                            | 150 |     |     | °C              |   |

| Thermal Shutdown Recovery Temperature | $T_{REC}$             |                                                            | 120 |     |     | °C              |   |

| Switching Frequency                   | $f_{SW}$              |                                                            | 50  |     | 70  | kHz             | E |

| Gate Pin Source Current               | I <sub>SOURCE</sub>   | C <sub>Load</sub> =1nF                                     |     | 300 |     | mA              | 1 |

| Gate Pin Sink Current                 | I <sub>SINK</sub>     | C <sub>Load</sub> =1nF                                     |     | 500 |     | mA <sub>C</sub> |   |

| Gate Pin Maximum Voltage              | $V_{Gate}$            |                                                            |     | 20  |     | V               | ľ |

# **CHARACTERISTIC CURVES**

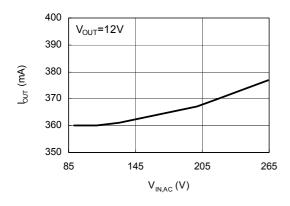

# **AC Input Voltage and Current**

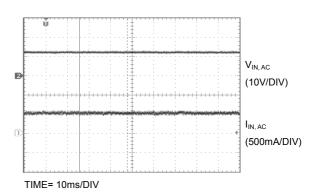

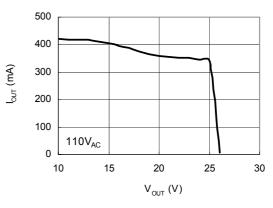

# **Output Voltage and Current**

Line Regulation

Load Regulation

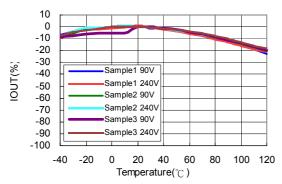

# Sample to Sample Offset vs. Temperature

#### APPLICATION INFORMATION

The A704 PWM controller is a monolithic integrated circuit, design for High Brightness LED application, provides the necessary feature to implement LED driver with a minimal external component needed. Internally implemented function include, a low start up current and operating current reducing the power dissipation on start-up resistor, Built-in OVP and UVLO function detected the LED output whether open and short circuit occur, SOT-23 package can save your PCB layout spaces and easy design into place you want, ...etc.

# **Application Circuit:**

Fig. 1 - Typical Application circuit

# **Circuit Topology**

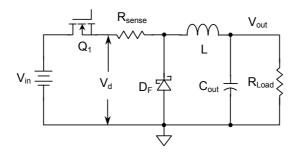

A Buck converter is an excellent choice for LED driver in off line application provides a constant LED current. A peak current controlled buck converter can give reasonable LED current variation over a wide input rang and LED voltage when the converter is implemented in continuous conduction mode. The A704 is a "Buck" or Step-Down Converter controller and its typical application circuit was shown as Fig.1. Simplify Fig. 1, its basic schematic can be seen in Fig.2.

Fig 2. Basic Buck converter

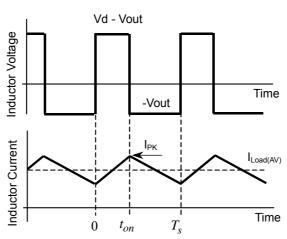

The operation of this regulator topology has two distinct time periods. The first one occurs when the series switch is "on", the input voltage is connected to the input of the inductor. The output of the inductor is the output voltage, and the rectifier (or catch diode) is reverse biased. During this period, since there is a constant voltage source connected across the inductor, the inductor current begins to linearly ramp upwards, as described by the following equation:

$$I_{L(on)} = \frac{(V_{in} - V_{out}) \times t_{on}}{L}$$

During this "on" period, energy is stored within the core material in the form of magnetic flux. If the inductor is properly designed, there is sufficient energy stored to carry the requirements of the load during the "off" period.

The next period is the "off" period of the power switch. When the power switch turns off, the voltage across the inductor reverses its polarity and is clamped at one diode voltage drop below ground by the catch diode. The current now flows through the catch diode thus maintaining the load current loop. This removes the stored energy from the inductor. The inductor current during this time is:

$$I_{L(off)} = \frac{V_{out} \times (T_s - t_{on})}{L}$$

This period ends when the power switch is once again turned on. Regulation of the converter is accomplished by varying the duty cycle of the power switch. It is possible to describe the duty cycle as follows:

$$D = \frac{t_{on}}{T_s}$$

Where,  $T_s$  is period of switching, and  $t_{on}$  is "turn on" time of  $Q_1$ .

For the buck converter with ideal components, the duty cycle can also be described as: Figure 3 shows the buck converter, idealized waveforms of the catch diode voltage and the inductor current.

Fig 3. Basic Buck converter

# **Component Selection**

This application note discusses the design of a buck-based LED driver using A704 with the help of an off-line application example. In this example, Vin= 90~240Vac & LED string voltage= 12V are used. Anyway, the same procedure can be used to design LED drivers with wide AC voltage input & DC voltage output.

# 1. Maximum output voltage consideration $(V_{o, max})$

The first design criterion to meet is that the maximum LED string voltage  $V_{o,\text{max}}$  is should be less than half the minimum input voltage to avoid having to implement a special loop compensation technique. For this example, the minimum input voltage  $V_{in dc}$  should be:

$$V_{in,dc}$$

min =  $2 \times V_{o,max}$

Where,  $V_{in,dc}$  min is the minimum voltage of bridge diodes

For example, the  $V_{in,dc}$  min in the circuit of this application note is about 100V. So the  $V_{o,max}$  (LED string voltage) should < 50V.

# 2. Choose the Input Diode Bridge (D<sub>BR</sub>)

hoose the Input Diode Bridge ( $D_{BR}$ )

The voltage rating of the bridge diode  $V_{bridge}$  will depend on the maximum value of the input voltage. The ent rating will depend on the maximum average current drawn by the converter.  $V_{bridge} = 1.25 \times (\sqrt{2} \times V_{\max,ac}) \dots (1)$ Where,  $V_{\max,ac}$  is the maximum input voltage RMS value.

The 1.25 factor in equation (1) is used for a safety margin.

For this design, the  $V_{bridge}$  should be exceed than (1.25\* 1.414\*  $V_{\max,ac}$ )= (1.25\*1.414\* 240)=425 V. A 600V. current rating will depend on the maximum average current drawn by the converter.

$$V_{bridge} = 1.25 \times (\sqrt{2} \times V_{\text{max},ac}) \dots (1)$$

0.5A bridge diode is chosen in the example.

# 3. Choose the Input inductor and input Capacitors

Placing an inductor (L1) in series with input bridge rectifier reduces input current rejection to input source. At this times, utilizing the equivalents series resistance (ESR) of L1 to limit the inrush current charge to input bulk capacitor C1. The ESR should limit the inrush current not more than the Maximum Peak forward Surge Current (I<sub>FSM</sub>) of the bridge rectifier specification as given by equation (2), assuming maximum voltage is applied. The required resistance is:

$$ESR \ge \frac{V_{bridge}}{I_{FSM}}$$

(2)

In this design, the  $V_{bridge}$  is 425 V and  $I_{FSM}$  is 30A. So the ESR of the chock should > (425/30)=14.1 $\Omega$ . If the power loss of such high ESR chock is too high, the designer can replace the high ESR chock with a low ESR chock and add a negative-temperature-coefficient (NTC) resistor to limit the inrush current. As long as the (NTC (hot) resistance + low ESR Chock resistance) is lower than the resistance of the high ESR chock, the efficiency of the A704 DC-DC can be improved.

The hold-up and input filter capacitor required at the diode bridge output have to be calculated at the minimum AC input voltage. The minimum capacitor value can be calculated as:

In this design,

$$C1 \ge \frac{V_{o,\text{max}} \times I_{o,\text{max}} \times (1 - 2 \times freq \times t_c)}{(2 \times V_{\text{min},ac}^2 - V_{\text{min},dc}^2) \times \eta \times freq}$$

Where, freq is the AC input frequency, as a rule, freq is  $50 \sim 60$ Hz.

$\eta$  is efficiency of the system, and  $t_c$  is the conduction angle of the AC input, use 45° conduction angle if unknown.

$$C1 \ge \frac{12 \times 0.35 \times (1 - 0.5)}{(2 \times 90^2 - 90^2) \times 0.8 \times 60} \ge 5.4uF$$

margin. For example, the input 220Vac input, the input capacitor voltage should exceed than as:

$$V_{\text{max } cap} \ge 1.15 \times \sqrt{2} \times V_{\text{max } ac} \Rightarrow V_{\text{max } ac} \ge 360V$$

The voltage rating of the capacitor should be at least 1.15 times greater than the peak input voltage for a safety gin. For example, the input 220Vac input, the input capacitor voltage should exceed than as:  $V_{\max,cap} \ge 1.15 \times \sqrt{2} \times V_{\max,ac} \Rightarrow V_{\max,ac} \ge 360V$  Choose a  $400\text{V}/10\mu\text{F}$  electrolytic capacitor in the example. Such electrolytic capacitor has sizable ESR component. The large ESR of these capacitors makes it inappropriate posorb the high frequency ripple current generated by the buck converter. Thus, adding a small MLCC capacitor in lelel with the electrolytic capacitor is recommended. to absorb the high frequency ripple current generated by the buck converter. Thus, adding a small MLCC capacitor in parallel with the electrolytic capacitor is recommended.

# 4. Choose the power choke

The inductor selection should make the Buck converter work in CCM; the inductor value depends on the ripple current in the LEDs. For example, assume a +/- 30% ripple current in the LEDs. Then, the inductor can be calculated as:

$$L = \frac{V_o(1-D)T_s}{0.6I_o \times \eta}$$

In this design example,  $T_s$  is 16.6 $\mu$  s, D=0.12, Vo=12V<sub>dc</sub>,  $\eta$ =0.8, Io=0.35

$$L = \frac{12 \times (1 - 0.12) \times 16.6 \,\mu}{0.6 \times 0.35 \times 0.8} = 1.05 mH$$

Choose the power choke inductance is 1mH.

Note that the inductance of most chocks drop when the chock current has DC-current components. This inductance drop may cause the actual Io to be lower than the calculation value of Io (please refer the Rcs section of this application note for more detail)

# 5: Choose the FET (Q1) and Diode (D<sub>F</sub>)

Since these power components (diode & MOSFET) maximum peak current exceeds the regulator maximum load current, these components current rating must be at least 1.2 times greater than the maximum load current. And the reverse voltage rating of these components should be at least 1.25 times the maximum input voltage. Therefore, the peak voltage seen by the FET is equal to the maximum input voltage

$$V_{Q1} = 1.25 \times V_{\text{max},ac} = 1.25 \times (\sqrt{2} \times 240) = 425V$$

Hence, the current rating of the FET is

$$I_{O1} = 1.25 \times I_{o.pk} = 1.25 \times 1.3 \times 0.35 = 0.57 A$$

In the example, choose at least a 500V 2A N-channel MOSFET. A 600V/2A N-channel MOSFET can allow more safety margin.

The peak voltage rating of the diode is as same as the Q1 MOSFET. Hence,

$$V_{DF} = 1.25 \times V_{\text{max},ac} = 1.25 \times (\sqrt{2} \times 240) = 425V$$

The average current through the diode is:

$$I_{DF} = 1.25 \times I_{o,pk} = 1.25 \times 1.3 \times 0.35 = 0.57 A$$

Choose 600V 2A Trr=35nS Fast recovery diode in the example.

# 6. Choose the Sense Resistor (R4)

Since the output ripple current  $I_{PP}$  is design for 0.6 times Io current.

$$I_{pp} = \frac{V_o(1-d)T_s}{I_c} = 0.6 \times I_o$$

Therefore the Peak current can be given as:

$$I_{pk} = I_o + \frac{1}{2}I_{pp} = 1.3 \times I_o$$

Hence, the sense resistor value is given by:

$$R_{cs} = \frac{V_{cs}}{1.3 \times I_o} = \frac{V_{cs}}{I_{pk}}$$

In the design example, use  $R_{CS} = (0.5V/(1.3*0.35) = 1.1\Omega$ . Note that factors like inductor value deviation could cause the actual Io to be higher (or lower) than the ideal value. So we may need to fine-tune the Rcs value for accurate Io.

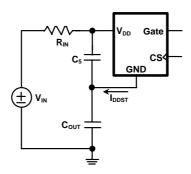

# 7. Start-up Circuitry

When the power is turned on, the input rectified voltage  $V_{in,dc}$  charges the hold-up capacitor  $C_5$  and the output capacitor Cout via a start-up resistor  $R_{in}$  as shown in Fig. 4. As the voltage of  $V_{CC}$  pin reaches the start threshold voltage  $V_{TH(ON)}$ , the A704 activates and drives the entire power supply to work.

$$V_{TH(ON)} \cong \frac{C_{out}}{C_{out} + C_5} (V_{in} - I_{DDST} \cdot R_{in}) (1 - e^{\frac{-T_D}{R_{in} \cdot (C_5 //C_{out})}})$$

Where  $I_{DDST}$  is the start-up current of A704

2.2uF/50V, and Cout is 22uF/50V, the Start-up delay  $T_{D\_ON}$  is less than 0.63 sec for 90Vac input.

Fig.4. Start-up Circuitry

Since the start-up current  $I_{DDST}$  is only 5uA typical, a large  $R_{IN}$  such as 2M ohms can be used. Also with a  $C_5$  is F/50V, and Cout is 22uF/50V, the Start-up delay  $T_{D_-ON}$  is less than 0.63 sec for 90Vac input.

For example, if the input voltage  $V_{in,dc}$  is 310Vdc, output voltage  $V_0$ =12Vdc, and start-up resistor  $R_{in}$  is  $C_0$ , the power dissipation on the  $C_0$  is  $C_0$ .  $2M\Omega$ , the power dissipation on the  $R_{in}$  is:

$$P_{R_{in}} = \frac{V_{in,dc}^2 - 2V_o^2}{R_{IN}} = \frac{310^2 - 2 \times 12^2}{2M} = 48mW$$

#### LAYOUT GUIDELINES

- 1. PCB Layout consideration: The hold-up capacitor C<sub>5</sub> need closed by the V<sub>DD</sub> pin of the controller IC •

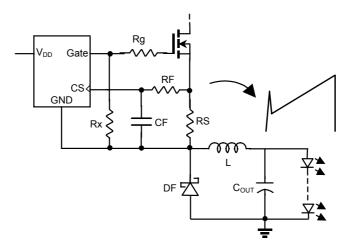

- 2. PCB Layout consideration: Please must put these components, (Cin1, Q1, R4, DF) & (Q1,704, R4,R7), as close as possible to each other when in PCB placement (refer to Fig-1, Fig-11 & Fig-12). An A704 DC-DC may not work well if some of these components are placed far away from others.

- 3. When the MOSFET turned on, a spike, which is induced by the diode reverse recovery and by the output capacitances of the MOSFET and diode, inevitably appears on the sensed signal. Inside A704, a leading edge blanking time about 250nsec is introduced to avoid premature termination of MOSFET by the spike. Therefore, only a small-value RC filter (e.g. 100ohm + 470pF) is required between the SENSE pin and RS.

- 4. A704 output stage is a totem pole driver stage that can directly drive MOSFET gate. It is also equipped with a voltage clamping circuit to protect MOSFET from damage caused by undesirable over drive voltage. The output voltage is clamped at 20Vmax. An external pull down resistor Rx in the range of 10k to 47k ohm is used to avoid floating state of gate before startup. A gate drive resistor Rg in the range from several to several tens ohm is recommended. This resistor limits the peak gate drive current and provides damping to prevent oscillations at the MOSFET gate terminal.

Fig.10. Gate drive

- 5. The power stage ground and the controller loop ground in this circuit is different, therefore, the measurement equipment need be isolated with device under test (DUT).

- 6. When output load is open/disconnect, the output voltage would increase the value of the over-voltage protection. However, the start-up circuitry still charges energy to the output capacitor; Placed a dummy load in the range of 10k to 47k ohm in the output is recommended.

Figure 11. Top layer

Figure 12. Bottom layer.

Table 1. Bill of Material list

| C.R. NO          | Q'TY | Description                | Vendor   | Package      |

|------------------|------|----------------------------|----------|--------------|

| A1               | 1    | A704 control IC            | ADD      | SOT23-5      |

| Q1               | 1    | Power NMOS 02N60H          | APEC     | TO-252,      |

| C <sub>IN1</sub> | 1    | E.C Cap: 10uF/ 400V        | NCC      | DIP D10x16mm |

| C <sub>X</sub>   | 1    | Cap X1 MPP 0.1uF           | Chiefcon | CKX104M      |

| L1               | 1    | IND 2.2mH                  | GangSong |              |

| L2               | 1    | IND 1mH                    | GangSong |              |

| DF               | 1    | DIO Super fast 600V 2A,    | PANJIT   | SMB          |

| DR               | 1    | DIO Fast Diode 600V 1A,    | PANJIT   | SMA          |

| D <sub>BR</sub>  | 1    | Bridge Diode 600V 0.5A B6S | PANJIT   | MDI          |

| R2, R8           | 2    | 1ΜΩ                        | relac    | SMD 1206     |

| R4               | 1    | 1.1Ω                       | relac    | SMD 0805     |

| R6               | 1    | 12Ω                        | relac    | SMD 0805     |

| R7               | 1    | 47kΩ                       | relac    | SMD 0805     |

| C5               | 1    | E.C Cap: 2.2uF/ 50V        | NCC      | D5x11        |

| C8               | 1    | E.C Cap : 22uF/ 50V        | NCC      | D5x11        |

# **IMPORTANT NOTICE**

ADDtek reserves the right to make changes to its products or to discontinue any integrated circuit product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

A few applications using integrated circuit products may involve potential risks of death, personal injury, or severe property or environmental damage. ADDtek integrated circuit products are not designed, intended, authorized, or warranted to be suitable for use in life-support applications, devices or systems or other critical applications. Use of ADDtek products in such applications is understood to be fully at the risk of the customer. In order to minimize risks associated with the customer's applications, the customer should provide adequate design and operating safeguards.

ADDtek assumes to no liability to customer product design or application support. ADDtek warrants the performance of its products to the specifications applicable at the time of sale.

Preliminary

ADDtek Corp.

9F, No. 20, Sec. 3, Bade Rd., Taipei, Taiwan, 105

TEL: 2-25700299 FAX: 2-25700196