# BYD Microelectronics Co., Ltd.

### **BM208 Series**

### **Two-cell Li Battery Protectors**

### **General Description**

The BM208 series are protection ICs for Lithium-ion rechargeable battery packs. It includes voltage detection unit, voltage reference unit, bias unit, delay unit, and logic circuits. The BM208 series have high-accuracy voltage detection for protecting Two-cell lithium battery packs from overcharge, over-discharge, excess-current and short circuit.

### **Applications**

### **Features**

- Overcharge Threshold

- 4.100~ 4.400V

- Accuracy Min. ±25mV (25 ) ±50mV (-20 ~70 )

- Over-discharge Threshold

- Typ. 2.33V

- Accuracy Min. ±80mV

- Excess Current 1 Protection Threshold

- Typ. 0.30V @ VC = 3.30V, VCC =6.60V

- Accuracy ±0.03V

- Excess Current 2 Protection Threshold

- Typ. 0.60V @ VC = 3.30V, VCC = 6.60V

- Accuracy ±0.10V

- Short Circuit Protection Threshold

- Typ. 1.50V @ VC = 3.30V, VCC = 6.60V

- Accuracy ±0.50V

- Low power Consumption

- Typ. 10.0uA @ VC = 3.90V, VCC =7.80V (Standard working current)

- Typ. 0.90uA @ VC = 2V, VCC = 4V (Standby current)

- Output Delay Of Overcharge

- Typ. 100ms (connect a 0.01uF cap to CT)

- Output Delay Of Over-discharge

- Typ. 24ms @ VC = 2.20V, VCC = 4.40V

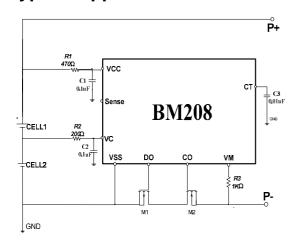

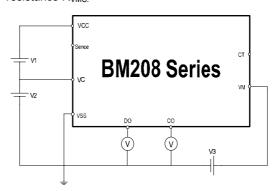

### **Typical Application Circuits**

### Recommended value:

$R_1=470\Omega$ ;  $R_2=200\Omega$ ;  $R_3=1k\Omega$ ;  $C_1=C_2=0.10uF$ ;  $C_3=0.01uF$ ;

#### **Notes**

$R_1C_1$ ,  $R_2C_2$  are to stabilize the supply voltage of the BM208 series.  $R_1C_1$  is hence regarded as the time constant for VCC pin.  $R_2C_2$  is hence regarded as the time constant for VC pin.  $R_1$  and  $R_3$  can also be a part of current-limit circuit for the BM208 series. Recommended values of these elements are as follows:

- $R_2 < 470\Omega$ . A larger value of  $R_2$  results in high detection voltage, low detection accuracy.

- $R_3 < 2.5$ kΩ. A larger value of  $R_3$  possibly counteracts resetting from over-discharge even with a charger.

$R_1 + R_3 - 1.2 k\Omega.$  Smaller values may lead to power consumption over the maximum dissipation rating of the BM208 series.

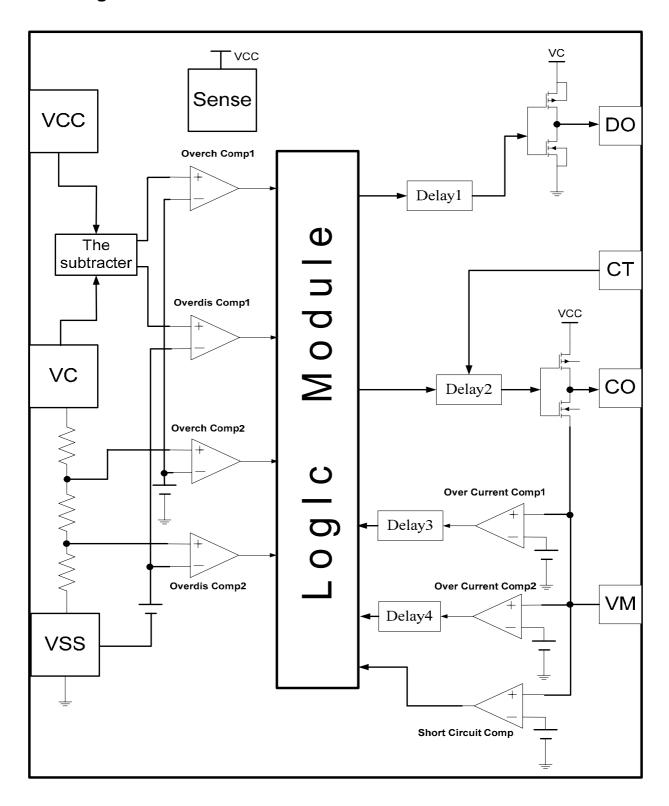

### **Block Diagram**

### **Selection Guide**

### Type Number

### BM208 XXXX

| Symbol | Meaning                                              | Description           |

|--------|------------------------------------------------------|-----------------------|

| vvvv   | Overcharge/Over-discharge/Excess Current 1 detection | Assigned from AAAA to |

| XXXX   | threshold and accuracy                               | WWWW                  |

### Type Number Option

Through choosing the "XXXX", the Overcharge Detection Threshold Voltage (VCT1, 2), the Over-discharge Detection Threshold voltage (VDT1,2), the Excess Current 1 Detection Voltage (VIT) and their accuracy of BM208 can be decided.

Table 1. VCT1, 2 & VDT1, 2 & Marking

(@25)

| Type<br>Number | Overcharge<br>detection<br>voltage 1, 2<br>VCT1, 2 | Overcharge<br>release<br>voltage 1, 2<br>VCR1, 2 | Over-discharge<br>detection<br>voltage 1, 2<br>VDT1, 2 | Over-discharge<br>release<br>voltage 1,2<br>VDR1, 2 | Excess<br>current 1<br>detection<br>VIT1 | Mark  |

|----------------|----------------------------------------------------|--------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------|------------------------------------------|-------|

| BM208 RHHA     | 4.250V±25mV                                        | 4.050±100mV                                      | 2.31V±80mV                                             | 3.01V±150mV                                         | 0.30V                                    | 8RHHA |

| BM208 LHHA     | 4.275V±25mV                                        | 4.075±100mV                                      | 2.32V±80mV                                             | 3.02V±150mV                                         | 0.30V                                    | 8LHHA |

| BM208 MHHA     | 4.300V±25mV                                        | 4.100±100mV                                      | 2.33V±80mV                                             | 3.03V±150mV                                         | 0.30V                                    | 8MHHA |

| BM208 HHHA     | 4.325V±25mV                                        | 4.125±100mV                                      | 2.34 V±80mV                                            | 3.04V±150mV                                         | 0.30V                                    | 8НННА |

| BM208 SHHA     | 4.350V±25mV                                        | 4.150±100mV                                      | 2.35 V±80mV                                            | 3.05V±150mV                                         | 0.30V                                    | 8SHHA |

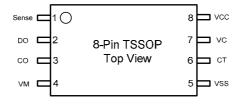

### **Package Type**

### **Pin Description**

| Pin number | Pin name | Description                                         |  |  |  |  |

|------------|----------|-----------------------------------------------------|--|--|--|--|

| 1          | Sense    | Connect to VCC                                      |  |  |  |  |

| 2          | DO       | Over-discharge detection pin, CMOS output           |  |  |  |  |

| 3          | CO       | Overcharge detection pin, CMOS output               |  |  |  |  |

| 4          | VM       | The excess-current detection pin                    |  |  |  |  |

| 5          | VSS      | Ground                                              |  |  |  |  |

| 6          | CT       | To connect capacitor for Overcharge detection delay |  |  |  |  |

| 7          | \( \( \) | The middle pin between two cells (to connect cell 1 |  |  |  |  |

| /          | VC       | cathode and cell 2 anode)                           |  |  |  |  |

| 8          | VCC      | Positive power input pin (to connect cell 1 anode)  |  |  |  |  |

### **Function Description**

#### 1. Normal Condition:

When both VC and (VCC-VC) are between the Over-discharge Detection Threshold Voltage (VDT) and the Overcharge Detection Threshold Voltage (VCT), and the VM pin voltage between the Charger Detection Threshold Voltage (VCHA) and the Excess Current 1 Detection Threshold Voltage (VIT1), the outputs of DO pin and CO pin are on high level, making the charge and discharge MOSFETs on. Charging and discharging can be carried out freely.

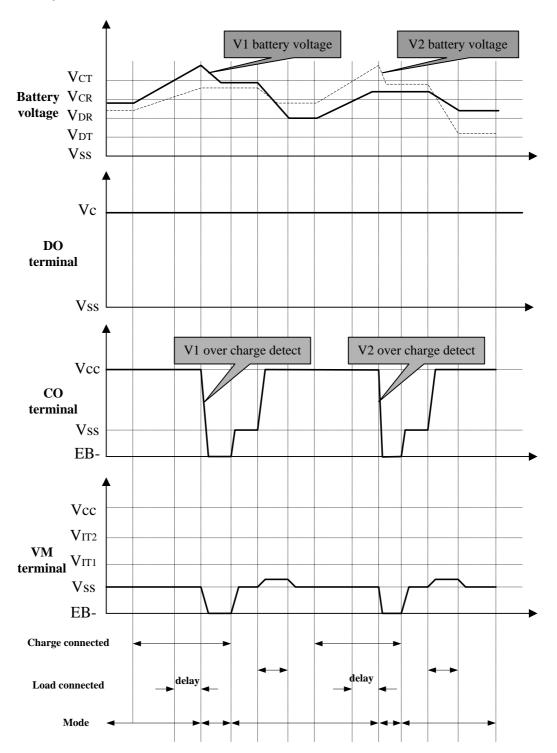

### 2. Overcharge Condition:

During charging, when VC or (VCC - VC) increases higher than VCT and takes the Overcharge Detection Delay Time ( $T_{CT}$ ) or longer, the output of CO pin will change from high level to low level, turning off the charging control FET to stop charging.

#### 3. Overcharge Protection Release Condition:

The output of CO pin will change to high level, making charging recovered, when either of the following conditions come into being: (1) both VC and (VCC - VC) become lower than the Overcharge Release Voltage (VCR); (2) a load connects to VCC after a charger is disconnected from the battery pack, and both VC and (VCC - VC) are lower than VCT.

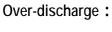

### 4. Over-discharge Condition:

During discharging, when VC or (VCC - VC) decreases lower than VDT and taking the Over-discharge Detection Delay Time ( $T_{DT}$ ) or longer, the output of DO pin will change from high level to low level, turning off the discharging control FET to stop discharging.

### 5. Over-discharge Protection Release Condition:

The output of DO pin will change to high level, making discharging recovered, when either of the following conditions come into being: (1) a charger is connected to the battery pack, and the battery supply voltage becomes lower than VDT, and VM is higher than the Charger Detection Threshold Voltage (VCHA); (2) both

the VC and (VCC - VC) become higher than the Over-discharge Release Voltage (VDR) and VM is between VCHA and VIT1.

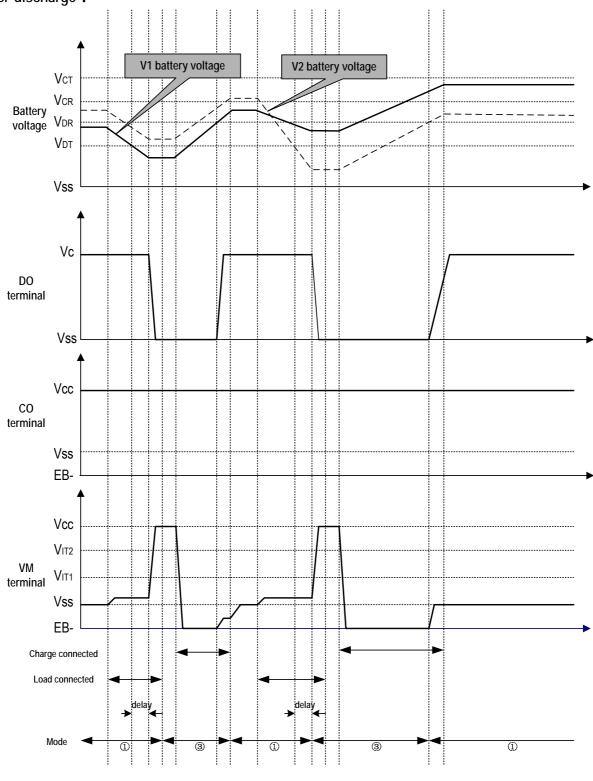

#### 6. Excess Current 1 Protection:

During discharging, the current varies with load, and VM increases with the rise of the discharging current. Once VM rises higher than the Excess Current 1 Detection Threshold Voltage (VIT1) and stays longer than the Excess Current 1 Detection Delay Time  $(T_3)$ , DO pin changes from high to low level, turning off the discharging control FET. Once that excess current state is removed, i.e. VM < VIT1, and the circuit recovers to normal state.

#### 7. Excess Current 2 Protection:

During discharging, the current varies with load, and VM increases with the rise of the discharging current. Once VM rises higher than the Excess Current 2 Detection Threshold Voltage (VIT2) and stays longer than the Excess Current 2 Detection Delay Time (T<sub>4</sub>), DO pin changes from high to low level, turning off the discharging control FET. Once that excess current state is removed, and VM < VIT1, and the circuit recovers to normal state.

#### 8. Short Circuit Protection:

This function has the same principle as the excess current protection. But, the delay time  $T_5$  is far shorter than  $T_3$  and  $T_4$ , and the threshold VSHORT is far higher than VIT1 and VIT2. When the circuit is shorted, VM increases rapidly. Once VM VSHORT, DO pin switches to low, turning off the discharging control FET. After the short circuit state is removed, and VM < VIT1, the circuit recovers to the normal state. The short circuit peak current is related to VSHORT and the ON resistance of the two FETs in series.

### 9. Abnormal Charge Current Condition:

If the VM pin voltage falls below the Abnormal Charge Current Detection Threshold Voltage (VAB) during charging under normal condition and takes the Abnormal Charge Current Detection Delay Time (TAB) or longer, the charging control FET is turned off and charging

stops. This action is called the Abnormal Charge Current Detection. Abnormal charge current detection works when the DO pin voltage is "H" and the VM pin voltage falls below the Abnormal Charge Current Detection Threshold Voltage (VAB). To an over-discharged battery, only when charging makes the battery voltage higher than the Over-discharge Detection Threshold, the Abnormal Charge Current Detection can act. Abnormal charge current state is released, once the voltage difference between VM pin and VSS pin becomes bigger than the Abnormal Charge Current Detection Threshold Voltage (VAB) value.

### 10. Charger Detect Condition:

A two-cell battery in over-discharge condition can be released, when it is connected to a charger, the VM pin voltage is lower than the Abnormal Charge Current Detection Threshold Voltage (VAB), and each cell voltage becomes higher than the Over-discharge Detection Threshold Voltage (VDT). This action is called Charger Detection. But, if the VM pin voltage is between the Abnormal Charge Current Detection Threshold Voltage (VAB) and the Excess Current 1 Detection Threshold Voltage (VIT1), the over-discharge state is not released unless the two cell voltages both become higher than the Over-discharge Release Voltage (VDR).

### Electrical Characteristic 1\*

(T<sub>OPT</sub>=25 unless otherwise specified)

| Item                                          | Symbol           | Condition            | Min.                | Тур.               | Max.                | Unit | Circuit  |

|-----------------------------------------------|------------------|----------------------|---------------------|--------------------|---------------------|------|----------|

| Detection Voltage                             | - J              | 00.10.11.011         |                     | .76.               |                     |      | o o dank |

| Over charge Detection Voltage 1,2             | VCT1,22*         | 25                   | VCT1,2-0.025        | VCT1,2             | VCT1,2+0.025        | V    | 1        |

| Over charge Release Voltage 1,2               | VCR1,23*         | 25                   | <i>VCT1,2</i> -0.30 | <i>VCT1,2</i> -0.2 | <i>VCT1,2</i> -0.10 | V    | 1        |

| Over-discharge Detection Voltage 1,2          | VDT1,22*         | 25                   | VDT1,2-0.08         | VDT1,2             | VDT1,2+0.08         | V    | 1        |

| Over-discharge Release Voltage 1,2            | VDR1,23*         | 25                   | <i>VDT1,2</i> +0.55 | <i>VDT1,2</i> +0.7 | <i>VDT1,2</i> +0.85 | V    | 1        |

| Excess Current 1 Detection Voltage            | VIT1             | V1=V2=3.30V          | 0.27                | 0.30               | 0.33                | V    | 1        |

| Excess Current 2 Detection Voltage            | VIT2             | V1=V2=3.30V          | 0.50                | 0.60               | 0.70                | V    | 1        |

| Short Circuit Detection Voltage               | VSHORT           | V1=V2=3.30 V         | 1                   | 1.50               | 2                   | V    | 1        |

| Abnormal Charge Detection Voltage             | VAB              | V1=V2=3.30 V         | -0.17               | -0.15              | -0.13               | V    | 1        |

| Charger Detection Voltage                     | VCHA             | V1=V2=3.30 V         | -0.17               | -0.15              | -0.13               | V    | 1        |

| Delay Time (C <sub>4</sub> =0.01u F)          |                  |                      | <u>I</u>            | I                  |                     |      |          |

| Over Charge Detection Delay Time              | Тст              | V1=V2=4.40V          | 50                  | 100                | 200                 | ms   | 3        |

| Over- discharge Detection Delay Time          | T <sub>DT</sub>  | V1=V2=2.20V          | 12                  | 24                 | 48                  | ms   | 3        |

| Over Current 1 Detection Delay Time           | T <sub>3</sub>   | V1=V2=3.30V          | 6                   | 12                 | 24                  | ms   | 3        |

| Over Current 2 Detection Delay Time           | T <sub>4</sub>   | V1=V2=3.30V          | 1                   | 2                  | 3                   | ms   | 3        |

| Short Circuit Detection Delay Time            | T <sub>5</sub>   | V1=V2=3.30V          |                     |                    | 10                  | us   | 3        |

| Abnormal Charge Detection Delay Time          | Тав              | V1=V2=3.30V          | 50                  | 100                | 200                 | ms   | 3        |

| Output Voltage And VM Internal Res            | istance          |                      | •                   |                    |                     |      |          |

| CO "H" Voltage                                | VCO(H)           | V1=V2=3.90V          | 7.55                | 7.60               |                     | V    | 4        |

| CO "L" Voltage                                | VCO(L)           | V1=V2=4.40V          |                     | 0.10               | 0.13                | V    | 4        |

| DO "H" Voltage                                | VDO(H)           | V1=V2=3.90V          | 3.77                | 3.82               |                     | V    | 4        |

| DO "L" Voltage                                | VDO(L)           | V1=V2=2.20V          |                     | 0.05               | 0.08                | V    | 4        |

| Resistance Between VM And VCC                 | $R_{\text{VMD}}$ | V1=V2=2.20V<br>VM=0V | 40                  | 110                | 200                 | ΚΩ   | 4        |

| Resistance Between VM And VSS R <sub>VI</sub> |                  | V1=V2=3.30V<br>VM=1V | 50                  | 150                | 300                 | ΚΩ   | 4        |

| Operation Voltage And Current Con             | sumption         | •                    | •                   | -                  |                     |      |          |

| Operation Voltage Between VCC And VSS         | VCSOP            | 25                   | 2                   | -                  | 16                  | V    |          |

| Operation Voltage Between VCC And VM          | VCMOP            | 25                   | 5                   | -                  | 28                  |      |          |

| Current Consumption During Normal State       | Горе             | V1=V2=3.90V          | 5                   | 10                 | 15                  | uA   | 2        |

| Current Consumption During Power Down         | I <sub>PDN</sub> | V1=V2=2.20V          | 0.50                | 0.90               | 1.50                | uA   | 2        |

| . •                                           |                  |                      |                     |                    |                     |      |          |

<sup>1\*</sup> The Electrical parameters for this temperature range is guaranteed by design, not tested in production.

<sup>2\*</sup> See "Selection Guide" section.

<sup>3\*</sup> VCT1, 2 and VDT1,2 are the Overcharge and Over-discharge threshold voltage of actual testing.

<sup>4\*</sup> V1 is the voltage of cell1 and V2 is the voltage of cell2, refer to the Typical Application Circuits and test circuits.

### Electrical Characteristic 1\*

(T<sub>OPT</sub>=-20~70 unless otherwise specified)

| Item                                    | Symbol                | Condition            | Min.                | Тур.               | Max.                | Unit | Circuit |

|-----------------------------------------|-----------------------|----------------------|---------------------|--------------------|---------------------|------|---------|

| Detection Voltage                       |                       |                      |                     |                    |                     |      |         |

| Over charge Detection Voltage 1,2       | VCT1,22*              |                      | VCT1,2-0.050        | VCT1,2             | VCT1,2+0.050        | V    | 1       |

| Over charge Release Voltage 1,2         | VCR1,23*              |                      | <i>VCT1,2</i> -0.35 | <i>VCT1,2</i> -0.2 | <i>VCT1,2</i> -0.05 | V    | 1       |

| Over-discharge Detection Voltage 1,2    | VDT1,22*              |                      | VDT1,2-0.10         | VDT1,2             | VDT1,2+0.10         | V    | 1       |

| Over-discharge Release Voltage 1,2      | VDR1,23*              |                      | <i>VDT1,2</i> +0.20 | <i>VDT1,2</i> +0.7 | <i>VDT1,2</i> +0.90 | V    | 1       |

| Excess Current 1 Detection Voltage      | VIT1                  | V1=V2=3.30V          | 0.26                | 0.30               | 0.34                | V    | 1       |

| Excess Current 2 Detection Voltage      | VIT2                  | V1=V2=3.30V          | 0.40                | 0.60               | 0.80                | V    | 1       |

| Short Circuit Detection Voltage         | VSHORT                | V1=V2=3.30 V         | 1                   | 1.50               | 2                   | V    | 1       |

| Abnormal Charge Detection Voltage       | VAB                   | V1=V2=3.30 V         | -0.18               | -0.15              | -0.12               | V    | 1       |

| Charger Detection Voltage               | VCHA                  | V1=V2=3.30 V         | -0.18               | -0.15              | -0.12               | V    | 1       |

| Delay Time (C <sub>4</sub> =0.01u F)    |                       |                      |                     |                    |                     |      |         |

| Over Charge Detection Delay Time        | Тст                   | V1=V2=4.40V          | 40                  | 100                | 250                 | ms   | 3       |

| Over -discharge Detection Delay Time    | T <sub>DT</sub>       | V1=V2=2.20V          | 8                   | 24                 | 60                  | ms   | 3       |

| Over Current 1 Detection Delay Time     | T <sub>3</sub>        | V1=V2=3.30V          | 4                   | 12                 | 30                  | ms   | 3       |

| Over Current 2 Detection Delay Time     | T <sub>4</sub>        | V1=V2=3.30V          | 1                   | 2                  | 5                   | ms   | 3       |

| Short Circuit Detection Delay Time      | <b>T</b> <sub>5</sub> | V1=V2=3.30V          |                     |                    | 10                  | us   | 3       |

| Abnormal Charge Detection Delay Time    | Тав                   | V1=V2=3.30V          | 40                  | 100                | 250                 | ms   | 3       |

| Output Voltage And VM Internal Res      | stance                |                      |                     |                    |                     |      |         |

| CO "H" Voltage                          | VCO(H)                | V1=V2=3.90V          | 7.50                | 7.60               |                     | V    | 4       |

| CO "L" Voltage                          | VCO(L)                | V1=V2=4.40V          |                     | 0.10               | 0.15                | V    | 4       |

| DO "H" Voltage                          | VDO(H)                | V1=V2=3.90V          | 3.72                | 3.82               |                     | V    | 4       |

| DO "L" Voltage                          | VDO(L)                | V1=V2=2.20V          |                     | 0.05               | 0.10                | V    | 4       |

| Resistance Between VM And VCC           | $R_{VMD}$             | V1=V2=2.20V<br>VM=0V | 30                  | 110                | 250                 |      | 4       |

| Resistance Between VM And VSS           | R <sub>VMS</sub>      | V1=V2=3.30V<br>VM=1V | 40                  | 150                | 400                 |      | 4       |

| Operation Voltage And Current Con       | sumption              |                      |                     |                    |                     |      |         |

| Operation Voltage Between VCC And VSS   | VCSOP                 |                      | 2                   | -                  | 16                  | V    |         |

| Operation Voltage Between VCC And VM    | VCMOP                 |                      | 5                   | -                  | 28                  |      |         |

| Current Consumption During Normal State | I <sub>OPE</sub>      | V1 = V2 = 3.90V      | 5                   | 10                 | 18                  | uA   | 2       |

| Current Consumption During Power Down   | I <sub>PDN</sub>      | V1 = V2 = 2.20V      | 0.50                | 0.90               | 1.50                | uA   | 2       |

<sup>1\*</sup> The Electrical parameters for this temperature range is guaranteed by design, not tested in production.

<sup>2\*</sup> See "Selection Guide" section.

<sup>3\*</sup> *VCT1,2* and *VDT1,2* are the Overcharge and Over-discharge threshold voltage of actual testing.

<sup>4\*</sup> V1 is the voltage of cell1 and V2 is the voltage of cell2, refer to the Typical Application Circuits and test circuits.

### **Absolute Maximum Ratings**

| Item                    | Symbol           | Pin   | Rated Value       | Unit |

|-------------------------|------------------|-------|-------------------|------|

| VCC-VSS Input Voltage   | $V_{DS}$         | VCC   | VSS-0.30~VSS+18   | V    |

| Sense Pin Input Voltage | $V_{Sense}$      | Sense | VSS-0.30~VCC+0.30 | V    |

| Delay Pin Input Voltage | V <sub>CT</sub>  | CT    | VSS-0.30~VCC+0.30 | V    |

| VM Pin Input Voltage    | VvM              | VM    | VCC-28~VCC+0.30   | V    |

| DO Pin Output Voltage   | $V_{DO}$         | DO    | VSS-0.30~VC+0.30  | V    |

| CO Pin Output Voltage   | V <sub>CO</sub>  | CO    | VM-0.30~VCC+0.30  | V    |

| Power Dissipation       | $P_D$            |       | 300               | mW   |

| Operation Temperature   | T <sub>opr</sub> |       | -20~+85           |      |

| Storage Temperature     | T <sub>stg</sub> |       | -40~+125          |      |

Attention: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### **Operation Timing Charts:**

### Overcharge:

Note: Normal mode Overcharge mode Over-discharge mode

Excess current 1 mode Excess current 2 mode

Short circuit mode

The number N = the times of the charge-discharge cycle.

Note: Normal mode Overcharge mode Over-discharge mode

Short circuit mode

The number N = the times of the charge-discharge cycle.

### **Excess current:**

Note: Normal mode Overcharge mode Over-discharge mode

Excess current 1 mode Excess current 2 mode

Short circuit mode

The number N = the times of the charge-discharge cycle.

### **Test Circuits**

(1) Overcharge detection threshold voltage and overcharge release voltage

### Test circuit 1

Set V2=3.30V V3=0V, the Overcharge Detection Threshold Voltage (VCT1) is the voltage between VCC and VC to which when V1 increases and keeps the condition for the Overcharge Detection Delay Time ( $T_{CT}$ ), VCO changes from "H" to "L". The overcharge release voltage (VCR1) is the voltage between VCC and VC to which when V1 decreases, VCO changes from "L" to "H".

Set V1=3.30V V3=0V, the Overcharge Detection Threshold Voltage (VCT2) is the voltage between VC and VSS to which when V2 increases and keeps the condition for the Overcharge Detection Delay Time ( $T_{CT}$ ), VCO changes from "H" to "L". The Overcharge Release Voltage (VCR2) is the voltage between VC and VSS to which when V2 decreases, VCO changes from "L" to "H".

# (2) Over-discharge detection threshold voltage and over-discharge release voltage

Set V2=3.30V V3=0V, the Over-discharge Detection

#### Test circuit 1

Threshold Voltage (VDT1) is the voltage between VCC and VC to which when V1 decreases and keep the condition for the Over-discharge Detection Delay Time ( $T_{DT}$ ), VDO changes from "H" to "L". The Over-discharge Release Voltage (VDR1) is the voltage between VC and VSS to which when V1 increases, VDO changes from "L" to "H". Set V1=3.30V V3=0V, the Over-discharge Detection Threshold Voltage (VDT2) is the voltage between VC and VSS to which when V2 decreases and keep the condition for the Over-discharge Detection Delay Time ( $T_{DT}$ ), VDO changes from "H" to "L". The Over-discharge Release Voltage (VDR2) is the voltage between VC and VSS to which when V2increases, VDO changes from "L" to "H".

# (3) Excess current detection threshold voltage and short circuit detection threshold voltage

#### Test circuit 1

Set V1=V2=3.30V, the Excess Current 1 Detection Threshold Voltage (VIT1) is the voltage V3 between VM and VSS to which when VM increases within 10 us and keep the

condition for the Excess Current 1 Detection Delay Time (T<sub>3</sub>), VDO changes from "H" to "L".

The Excess Current 2 Detection Threshold Voltage (VIT2) is the voltage V3 between VM and VSS to which when VM increases within 10 us and keep the condition for the Excess Current 2 Detection Delay Time (T<sub>4</sub>), VDO changes from "H" to "L".

The Short Circuit Detection Threshold Voltage (VSHORT) is the voltage V3 between VM and VSS to which when VM increases within 10us and keep the condition for the Short Circuit Detection Delay Time (T5), VDO changes from "H" to "L".

## (4) Charger detection threshold voltage and abnormal charge current detection threshold voltage

#### Test circuit 1

In the over-discharge condition, increase V2 gradually until it is between VDT2 and VDR2. The voltage between VM and VSS to which when V3 decreases from 0V, VDO changes from "L" to "H", is the Charger Detection Threshold Voltage (VCHA).

In the normal charging condition, the voltage between VM and VSS to which when V3 decreases from 0V, VCO changes from "H" to "L" is the Abnormal Charge Current Detection Threshold Voltage (VAB). It has the same value as the Charger Detection Threshold Voltage (VCHA).

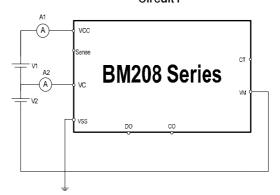

# (5) Normal operation current consumption and power down current consumption

### Test circuit 2

Set V1=V2=3.30V, the current A1 flowing through VCC and Sense pin and the current A2 flowing through VC pin are the normal operation consumption current ( $I_{OPE}$ ).

Set V1=2.20V V2=2.20V, the current A1 flowing through VCC and Sense pin and the current A2 flowing through VC pin are the power down current consumption (I<sub>PDN</sub>).

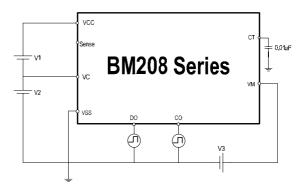

# (6) Overcharge detection delay time and over-discharge detection delay time

#### Test circuit 3

Set V3=0V, If V1 or V2 increases to be VCT1 or over VCT1 and keeps the condition for some time, VCO will change from "H" to "L". The time is called Overcharge Detection Delay Time (T<sub>CT</sub>). It is used to judge whether overcharge

happens indeed.

#### Test circuit 3

Set V3=0V, If V1 or V2 decreases to be VDT1 or below VDT1 and keeps the condition for some time, VDO will change from "H" to "L". The time is called Over-discharge Detection Delay Time  $(T_{DT})$ . It is used to judge whether over-discharge happens indeed.

# (7) Excess current detection delay time and short circuit detection delay time

#### Test circuit 3

Set V1=V2=3.30V, If V3 increases to be VIT1 or over VIT1 and keeps the condition for some time, VDO will change from "H" to "L". The time is called Excess Current 1 Detection Delay Time  $(T_3)$ . It is used to judge whether excess current 1 happens indeed.

Set V1=V2=3.30V, If V3 increases to be VIT2 or over VIT2 and keeps the condition for some time, VDO will change from "H" to "L". The time is called Excess Current 2 Detection Delay Time  $(T_4)$ . It is used to judge whether excess current 2 happens indeed.

Set V1=V2=3.30V, If V3 increases to be VSHORT or over VSHORT and keeps the condition for some time, VDO will change from "H" to "L". The time is called Short Circuit Delay Time ( $T_5$ ). It is used to judge whether short circuit happens indeed.

### (8) CO and DO output voltage

### Test Circuit 4

Set V1=V2=3.90V, V5=0V, K1 on and K2 off, increaseV4 from 0V gradually, the V4 voltage when A2 = 50uA is the CO 'H' voltage (VCOH).

Set V1=V2=4.40V, V5=0V, K1 on and K2 off, increase V4 from 0V gradually, the V4 voltage when A2 = -50uA is the CO 'L' voltage (VCOL).

Set V1=V2=3.90V, V5=0V, K1 off and K2 on, increase V3 from 0V gradually, the V3 voltage when A1 =50uA is the DO 'H' voltage (VDOH).

Set V1=V2=2.20V, V5=0V, K1 off and K2 on, increase V3 from 0V gradually, the V3 voltage when A1 = -50uA is the DO 'L' voltage (VDOL).

# (9) Internal resistance VM-VCC and VM-VSS Test circuit 4

Set V1=V2=2.20V, V5=0V, K1 off and K2 off, (V1+V2)/I3 is the internal resistance  $R_{\text{VMD}.}$

Set V1=V2=3.30V, V5=1V, K1 off and K2 off, V5/I3 is the internal resistance  $R_{\text{VMS}}$

Circuit1

Circuit2

Circuit3

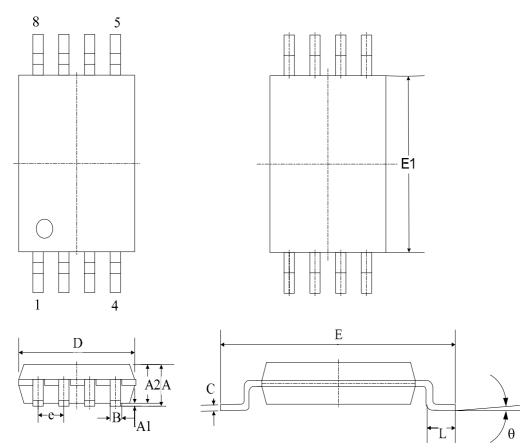

### Package Outline

### **Dimensions**

|    | DIM. | Α     | A1    | A2    | В     | С     | D     | Е     | E1    | е            | L     | θ  |

|----|------|-------|-------|-------|-------|-------|-------|-------|-------|--------------|-------|----|

|    | MIN. | 1.050 | 0.020 | 0.800 | 0.170 |       | 2.900 | 6.200 | 4.300 |              | 0.450 | 0° |

| mm | NOM. | ı     | ı     | ı     | ı     | 0.127 | -     | 6.400 | 4.400 | 0.650<br>BSC | 0.600 | 4° |

|    | MAX. | 1.200 | 0.150 | 1.050 | 0.300 |       | 3.200 | 6.600 | 4.500 | 200          | 0.750 | 8° |

BYD Microelectronics Co. Ltd. reserves the right to modify the specifications without prior notification.