## iP7302

# TRANSITION-MODE SINGLE STAGE PFC LED POWER SUPPLY

#### 1. Description

The iP7302 is a peak current mode fly-back PFC controller, with transition current turn-on ( transition mode ). It operates on fly-back circuit after rectifier diode, so the waveform of input current follows that of voltage.

iP7302 is different from iP7300 in the connections of inputs of error amplifier between pin1 and pin2. The Pin1 is connected to positive input and pull up  $50 \text{K}\Omega$  resistor to internal supply of 5V. The negative input is connected to output to form unity gain buffer. Pin2 is non connected. This modification is specially made to suit single stage LED power supply which requires PFC.

The structure of single stage LED power supply with PFC offers several advantages: high PF, no need of bulk electrolytic capacitor, output isolates from line input, reasonable size and cost. The disadvantage is that the output contains 120/100Hz ripple. But with iP7700, the average current may be controlled very well.

With output clamp at 18V, the iP7302 has a wide VDD operation range. The turn-on delay of soft-drive facilitates valley voltage switching, and the soft drive itself minimizes turn-on current spike. Thus higher efficiency could be achieved.

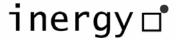

The iP7302 is packaged with small size SOP-8, and it is easy to use with few external components. It is also equipped with under voltage lock out (UVLO) with very small start-up current.

#### 2. Features

- Wide VDD operation range with internal output voltage clamp at 18V

- UVLO with low standby current

- Soft drive for minimizing turn-on current spike

- Zero current with valley voltage switching

- Low operating current

- SOP-8L packaging with few external components needed

- High power factor with low THD

### 3. Applications

LED lighting

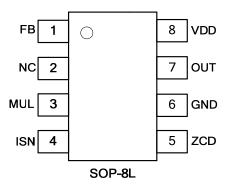

### 4. Pin Assignments

1

# iP7302

### 5. Marking Information

| Product Name | Marking                        |

|--------------|--------------------------------|

| iP7302       | iP7302<br>XXXXXX X : Date Code |

### 6. Ordering Code

| iP7302 ☐ Assembly Material | Assembly Material<br>G: Halogen and Lead Free Device |

|----------------------------|------------------------------------------------------|

|----------------------------|------------------------------------------------------|

Note: inergy defines "Green" as lead-free ( RoHS compliant ) and halogen free ( Br or Cl does not exceed 900 ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500 ppm by weight ; Follow IEC 61249-2-21 and IPC/JEDEC J-STD-020C )

#### 7. Pin Definitions

| Pin | Name | Description                                                                                                                                                      |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | FB   | Non inverting input of the buffer. A 50K $\Omega$ resistor is connected between this pin and internal 5V.                                                        |

| 2   | NC   | No connected.                                                                                                                                                    |

| 3   | MUL  | Input of the multiplier stage. A resistive divider is connected between the rectified mains and this pin, to provide the sinusoidal reference to the multiplier. |

| 4   | ISN  | Input of the PWM comparator. The current flowing in the MOSFET is sensed by a resistor and the resulting voltage is applied to this pin.                         |

| 5   | ZCD  | Flyback inductor's demagnetization sensing input for transition-mode operation. A negative-going edge triggers MOSFET's turn on.                                 |

| 6   | GND  | Ground.                                                                                                                                                          |

| 7   | OUT  | Gate driver output.                                                                                                                                              |

| 8   | VDD  | Supply voltage of driver and control circuits.                                                                                                                   |

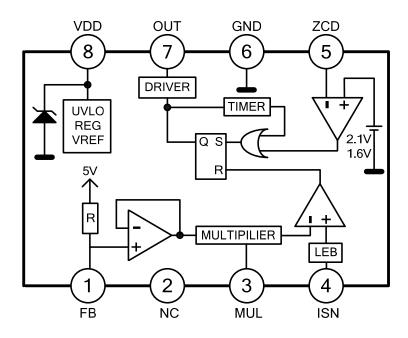

# 8. Block Diagram

# 9. Absolute Maximum Ratings

| Parameter                            | Symbol            | Value       | Unit |

|--------------------------------------|-------------------|-------------|------|

| Supply voltage                       | VDD               | 20          | V    |

| Maximum voltage on FB, MUL, ISN, ZCD | V                 | - 0.3 ~ 6   | V    |

| Maximum junction temperature         | TJ <sub>max</sub> | 150         | °C   |

| Storage temperature                  | T <sub>STG</sub>  | - 60 to 150 | °C   |

| ESD capability, HBM model            | V                 | 2.0         | kV   |

| ESD capability, MM model             | V                 | 200         | V    |

#### 10. Electrical Characteristics

( VDD = 15V, for typical values  $T_J$  = 25 °C )

| Parameter                         | Symbol             | Conditions                        | Min.   | Тур. | Max.     | Unit |

|-----------------------------------|--------------------|-----------------------------------|--------|------|----------|------|

| SUPPLY VOLTAGE S                  | ECTION             |                                   |        |      |          |      |

| Operating Range                   | VDD                | after turn-on                     | 11     | -    | 17       | V    |

| Turn-on Threshold                 | VDD on             |                                   | 11     | 12   | 13       | V    |

| Turn-off Threshold                | VDD off            |                                   | 9      | 10   | 11       | V    |

| On/Off Hysteresis                 | Hys                |                                   | 1.8    | 2    | 2.2      | V    |

| SUPPLY CURRENT S                  | ECTION             |                                   |        |      |          |      |

| Start-up Current                  | IDD <sub>st</sub>  | before turn-on<br>(VDD = 11V)     | -      | 15   | -        | uA   |

| Quiescent Current                 | Iq                 |                                   | -      | 1    | -        | mA   |

| Operating Current                 | IDD <sub>op</sub>  | PWM loaded,<br>f = 20kHz, C = 1nF | -      | 1.8  | -        | mA   |

| FEEDBACK SECTION                  | ١                  |                                   |        |      |          |      |

| Internal Pull Up Resistor         | R <sub>FB</sub>    |                                   | -      | 50   | -        | kΩ   |

| Open Circuit Voltage              | $V_{FB}$           |                                   | -      | 5.5  | -        | V    |

| <b>MULTIPLIER SECTIO</b>          | N                  |                                   |        |      |          |      |

| Input Bias Current                | I <sub>MUL</sub>   |                                   | -      | -    | 0.1      | uA   |

| Linear Operation Voltage          | $V_{MUL}$          |                                   | 0 to 4 | -    | 0 to 4.5 | V    |

| Gain                              | K                  | $V_{MUL} = 1V V_{COMP} = 3V$      | 0.32   | 0.4  | 0.48     | 1/V  |

| ZERO CURRENT DETE                 | CTOR               |                                   |        |      |          |      |

| Input Bias Current                | I <sub>ZCD</sub>   |                                   | -      | -    | 1        | uA   |

| Zero Current Detect               | V <sub>ZCD</sub>   | Negative slope                    | -      | 1.6  | -        | V    |

| Zero Current Detect<br>Hysteresis | V <sub>H</sub>     |                                   | -      | 0.5  | -        | V    |

| Delay To Turn On                  | tzcD               |                                   | -      | 300  | -        | ns   |

| Upper Clamp Voltage               | V <sub>ZCD-U</sub> | I <sub>ZCD</sub> = 20uA           | -      | 4.8  | -        | V    |

| Opper Clamp Voltage               |                    | I <sub>ZCD</sub> = 3mA            | -      | 5.9  | -        | V    |

| Lower Clamp Voltage               | V <sub>ZCD-L</sub> | $I_{ZCD} = -3mA$                  | -      | 0.2  | -        | V    |

| Input Capacitance                 | C <sub>par</sub>   | V <sub>ZCD</sub> = 1.0V           | -      | 10   | -        | pF   |

| Maximum Off Time                  | t <sub>OFF</sub>   |                                   | 75     | 150  | 300      | us   |

| CURRENT SENSE COMPARATOR          |                    |                                   |        |      |          |      |

| Input Bias Current                | I <sub>CS</sub>    |                                   | -      | -    | 0.1      | uA   |

| Delay To Turn Off                 | t <sub>delay</sub> |                                   | -      | 250  | 450      | ns   |

| LEB                               | t <sub>LEB</sub>   |                                   | -      | 300  | -        | ns   |

| Current Sense Limit               | V <sub>limit</sub> | V <sub>COMP</sub> = Upper Clamp   | 1.6    | 1.7  | 1.8      | V    |

| OUTPUT SECTION  |                 |                   |   |     |   |   |

|-----------------|-----------------|-------------------|---|-----|---|---|

| Output Clamp    | Vo_clamp        |                   | - | 17  | - | V |

| Dropout Voltage | V <sub>GD</sub> | IGDsource = 200mA | - | 3   | 1 | V |

|                 |                 | IGDsource = 20mA  | - | 0.3 | 1 | V |

|                 |                 | IGDsink = 200mA   | - | 2.5 | - | V |

|                 |                 | IGDsink = 20mA    | - | 0.2 | - | V |

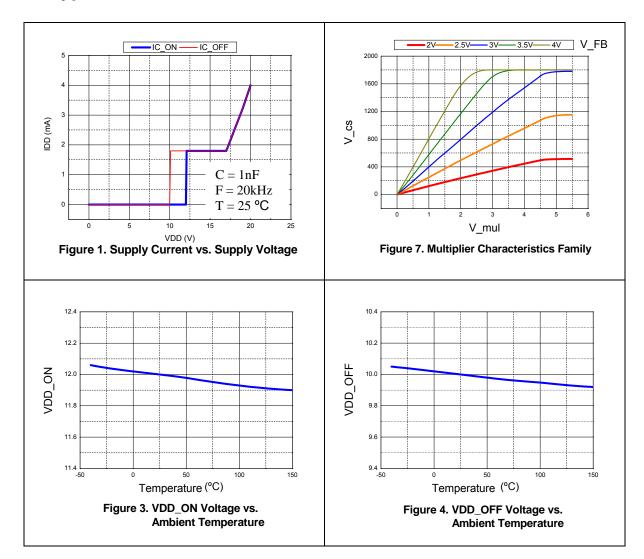

### 11. Typical Characteristics

inergy⊡

# 12. Application circuit and function description

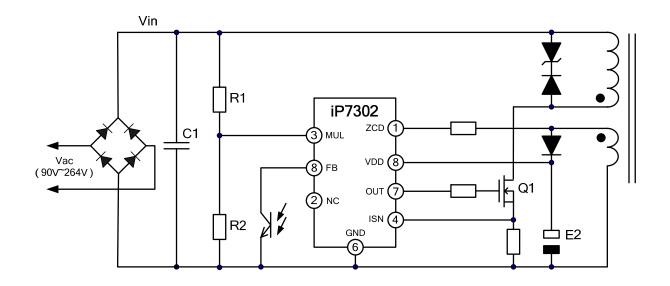

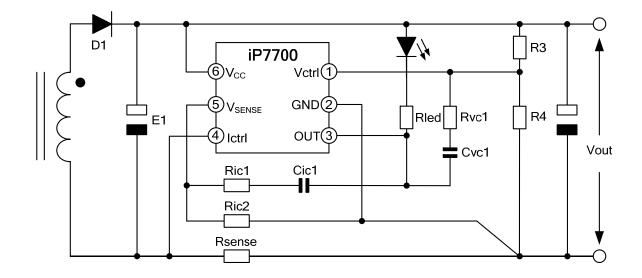

### 12.1 Typical application circuit

### iP7302

#### a. Power supply

Power is supplied between VDD and GND pin. At VDD below UVLO off, IC is in Under Voltage Lock Out ( UVLO ) state, It does not operate and consumes very low current. As voltage increases above UVLO on, the IC starts to operate with 1mA power consumpition. During this time IC power is provided by E2 capacitor, so it voltage decreases. Before the voltage drops to UVLO off, since some auxiliary power provides continuum power, the IC continues to operate. However, if the voltage drops below UVLO off, it enters UVLO state.

#### b. PWM

During operation, if the iP7302 is off for more than tOFF, an internal timer triggers the output on. It might happen at very beginning. The output drives the external MOSFET(Q1) on, so the current pass through primary winding of flyback transformer and Q1 increases with di/dt = Vin/L. The voltage across secondary winding of inductor is negative.

The current is sensed through ISN pin by detecting voltage across a sense resistor. If it exceeds target values, output is turned off. As the current through transformer must be continuous, so it flows through flyback diode ( D1 ) to output capacitor( E1 ). Voltage of E1 is always higher than zero, so the current is decreasing with di/dt = -vout/L. The voltage across auxiliary winding of inductor is positive, which is sensed by ZCD pin.

Re-turn on is initiated by two mechanisms: maximum off time and zero current detect( ZCD ). As the current decreases to zero, the diode is off, and the drain voltage of Q1 is oscillating about Vin. As it swings through Vin, the auxiliary winding voltage swings through zero. When it swings across 1.6V ZCD trigger the output on. The process is repeated as PWM switching.

#### c. Current shaping

For transition conduction mode, current always starts from zero when Q1 is on, and Q1 is off when current reaches a target value that follow the input voltage. As Q1 is turn off, the current is diverted to output capacitor and decreasing. The input current looks as triangle, and its peak follows input voltage. Therefore, if the current ripple at switching frequency is filtered ( using C1 ), the average input current, which is half of its peak, would look as the input sinusoidal voltage. High power factor and low total Harmonics Distortion ( THD ) may be achieved.

#### d. Feedback output control

For LED power applications, current controls is the primary concerned, and voltage is controlled when output is open to prevent over voltage. The iP7700 serves for this purpose. It consists of two sets of voltage reference and error amplifier. First is 0.2 V, for current controls, and  $2^{\text{nd}}$  is 1.21 V for voltage controls

Output current is sensed on the voltage difference between Rsense.  $R_{IC2}$  is the input resistor of current controller.  $R_{IC1}$  and  $C_{iC1}$  is its PI (proportional integral) compensator.

Output voltage is sensed through R3, R4 voltage divider. Its effective resistance acts as input resistor of voltage controller.  $R_{VC1}$  and  $C_{VC1}$  is its PI (proportional integral) compensator.

The outputs of current and voltage controller are open drain, so they may be connected together as "OR" logic, which ever reaches will controls.

This output signal pulls current through Rled and photo-diode of photo-coupler, and proportional current passes through the transistor of photo-coupler. It would pull the FB pin down. The close loop would reach an ( quasi ) equilibrium, in which output current or voltage is near to the set point.

For LED application, the voltage's set point is set possibly high, and current is set at the operation current of LED, so current is controlled.

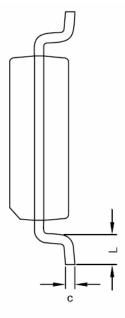

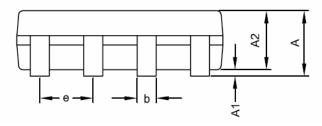

### 13. Package Dimensions

#### SOP-8L

| Symbol   | Dimensions In Millimeters |      |  |

|----------|---------------------------|------|--|

| Syllibol | MIN.                      | MAX. |  |

| Α        | 1.35                      | 1.75 |  |

| A1       | 0.00                      | 0.25 |  |

| A2       | 1.15                      | 1.50 |  |

| D        | 4.80                      | 5.00 |  |

| E        | 5.80                      | 6.20 |  |

| E1       | 3.80                      | 4.00 |  |

| С        | 0.19                      | 0.27 |  |

| b        | 0.33                      | 0.53 |  |

| е        | 1.27 BSC                  |      |  |

| L        | 0.40                      | 1.27 |  |

#### Notes:

- 1. Jedec outline: MS-012AA

- 2. Dimensions "D" does not include mold flash, protrusions and gate burrs shall not exceed .15 mm (.006 in) per side .

- 3. Dimensions "E1" does not include inter-lead flash, or protrusions. Inter-lead flash and protrusions shall not exceed .25 mm (.010 in) per side.