**Enabling Energy Efficient Solutions**

www.onsemi.com

#### **ON Semiconductor®**

# Design and Implementation of a fixed-frequency Adapter with Very Low Power Consumption

# Agenda

- New ENERGY STAR<sup>®</sup> requirements

- Needed features to meet the new specification

- New controller family NCP1237/38/87/88

- Design step 1: Power stage

- Design step 2: Set the compensations

- Design step 3: No Load Input Power

- Design step 4: Magnetics

- Design step 5: EMI

- Preliminary demo board example

- Conclusion

### **EPA 2.0 (External Power Supplies)**

#### EPA ENERGY STAR Version 2.0 EPS Voluntary Specification (Effective November 1, 2008)

Energy-Efficiency Criteria for Ac-Ac and Ac-Dc External Power Supplies in Active Mode: Standard Models

| Nameplate Output Power (P | Minimum Average Efficiency in Active Mode<br>(expressed as a decimal) |  |  |

|---------------------------|-----------------------------------------------------------------------|--|--|

| 0 to ≤ 1 watt             | ≥ 0.480 * P <sub>no</sub> + 0.140                                     |  |  |

| > 1 to ≤ 49 watts         | ≥ [0.0626 * Ln (P <sub>no</sub> )] + 0.622                            |  |  |

| > 49 watts                | ≥ 0.870                                                               |  |  |

(was > 0.84 in previous version 1.1)

Energy-Efficiency Criteria for Ac-Ac and Ac-Dc External Power Supplies

|     | _                           |                          |             |      |               |

|-----|-----------------------------|--------------------------|-------------|------|---------------|

| Nan | Nameplate Output Power (P ) | Maximum Power in No-Load |             | ∍de  |               |

|     | no                          | AC-AC EPS                | AC-DC EPS   |      |               |

|     | 0 to < 50 watts             | ≤ 0.5 watts              | ≤ 0.3 watts | (< 0 | .5 W in 1.1)  |

|     | ≥ 50 to ≤ 250 watts         | ≤ 0.5 watts              | ≤ 0.5 watts | (< 0 | .75 W in 1.1) |

#### **Energy Consumption Criteria for No-Load**

# EPS 5.0 (ENERGY STAR<sup>®</sup> Program Requirements for Computers)

- Defines E<sub>TEC</sub> for different types of products as a Typical Energy Consumption

- For the desktop and notebook product categories TEC will be determined by the following formula:

$E_{TEC} = (8760/1000) * (P_{off} * T_{off} + P_{sleep} * T_{sleep} + P_{idle} * T_{idle})$

- where all Px are power values in watts, all Tx are Time values in % of year, and the TEC E<sub>TEC</sub> is in units

of kWh and represents annual energy consumption based on mode weightings

- The light load efficiency and no load consumption is more important

E<sub>TEC</sub> requirement desktops and notebooks

|           | Desktops and Integrated Computers (kWh) | Notebook Computers (kWh)   |

|-----------|-----------------------------------------|----------------------------|

|           | <b>Category A</b> : ≤ 148.0             | <b>Category A</b> : ≤ 40.0 |

| TEC (kWh) | <b>Category B</b> : ≤ 175.0             | <b>Category B</b> : ≤ 53.0 |

|           | <b>Category C</b> : ≤ 209.0             | <b>Category C</b> : ≤ 88.5 |

|           | <b>Category D</b> : ≤ 234.0             |                            |

• Effective from July 1, 2009 (except: game consoles from July 1, 2010)

# Agenda

- New ENERGY STAR<sup>®</sup> requirements

- Needed features to meet the new specification

- New controller family NCP1237/38/87/88

- Design step 1: Power stage

- Design step 2: Set the compensations

- Design step 3: No Load Input Power

- Design step 4: Magnetics

- Design step 5: EMI

- Preliminary demo board example

- Conclusion

## **Improving Efficiency**

- Sources of loss:

- Switching losses:

$$P_{loss(switching)} = \frac{1}{2} \cdot C_{DRAIN} V_{DRAIN(turn-off)}^{2} \cdot F_{SW}$$

- Losses caused by leakage inductance:

$$P_{loss(leak)} = \frac{1}{2} \cdot L_{leak} \cdot I_{peak}^{2} \cdot \overline{F_{SW}}$$

- <u>Ways to improve efficiency:</u>

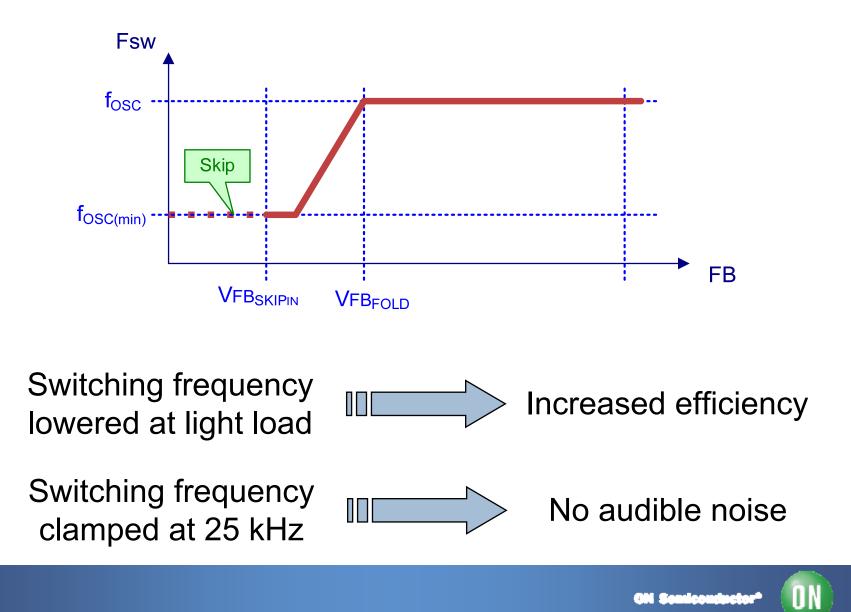

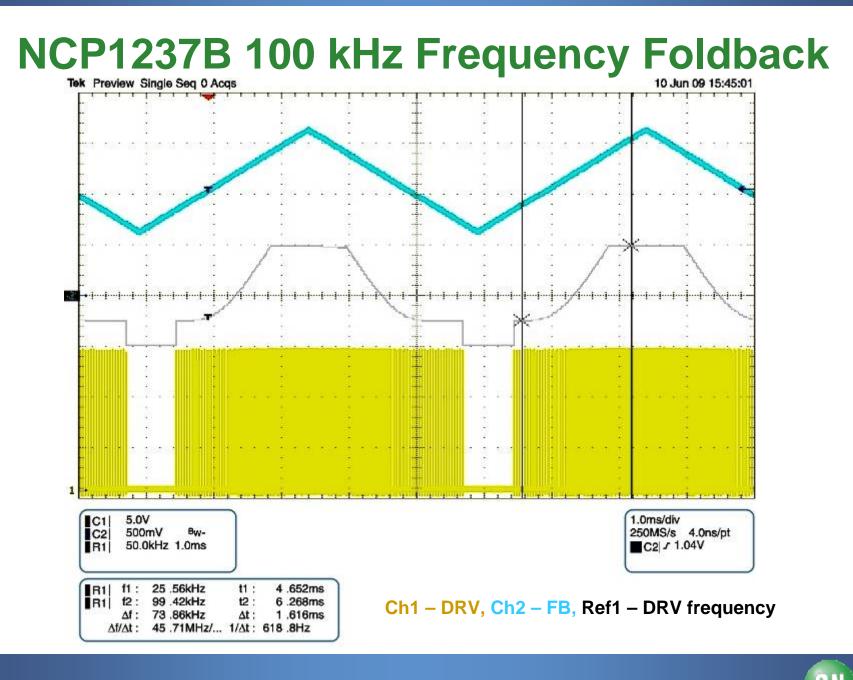

- − Lower the switching frequency  $F_{SW}$  → frequency foldback at light loads

- Lower the Drain voltage at turn-off  $\rightarrow$  valley switching

### **Reducing No-load Input Power**

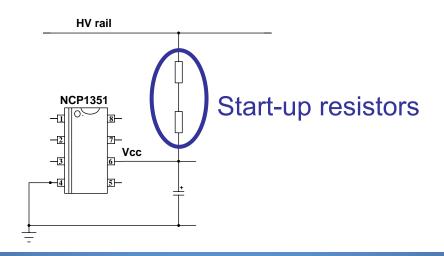

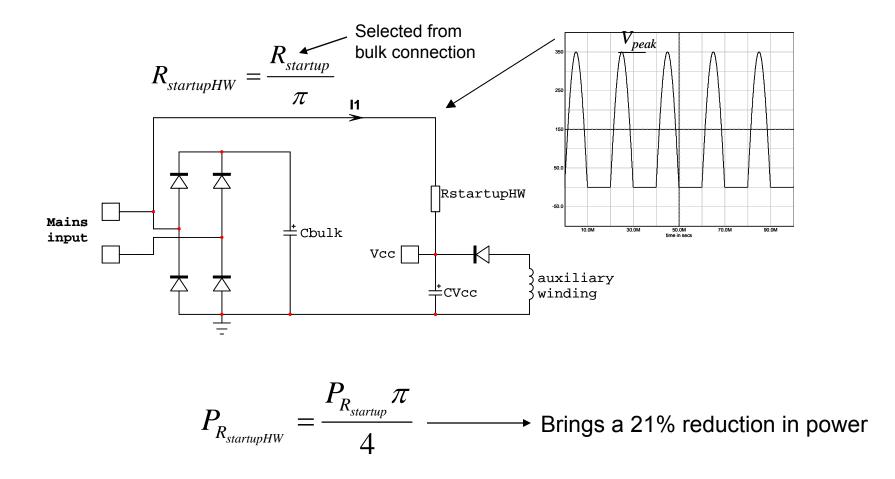

- Static losses in the start-up circuit:

- Start-up resistor permanently drawing current from the bulk capacitor

- Ways to lower the start-up circuit losses

- − With external start-up resistor → Extremely low start-up current

- Integrated start-up current source → Extremely low leakage when off

- Connect the start-up circuit to the half-wave rectified ac input

#### **Reducing No-load Input Power**

# Agenda

- New ENERGY STAR<sup>®</sup> requirements

- Needed features to meet the new specification

- New controller family NCP1237/38/87/88

- Design step 1: Power stage

- Design step 2: Set the compensations

- Design step 3: No Load Input Power

- Design step 4: Magnetics

- Design step 5: EMI

- Preliminary demo board example

- Conclusion

### NCP1237/38/87/88

#### **Value Proposition**

The NCP1237/38/87/88 series represents the next generation of fixed frequency PWM controllers. A targets applications where cost-effectiveness, reliability, design flexibility and low standby power are compulsory.

#### **Unique Features**

#### **Benefits**

Fewer components and

Extremely low no-load

Simple option to alter the

max. peak current set

rugged design

standby power

point at high line

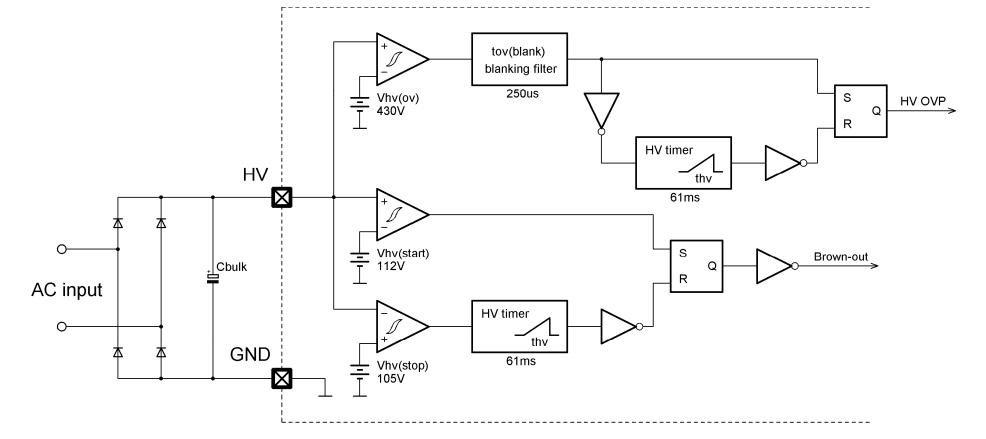

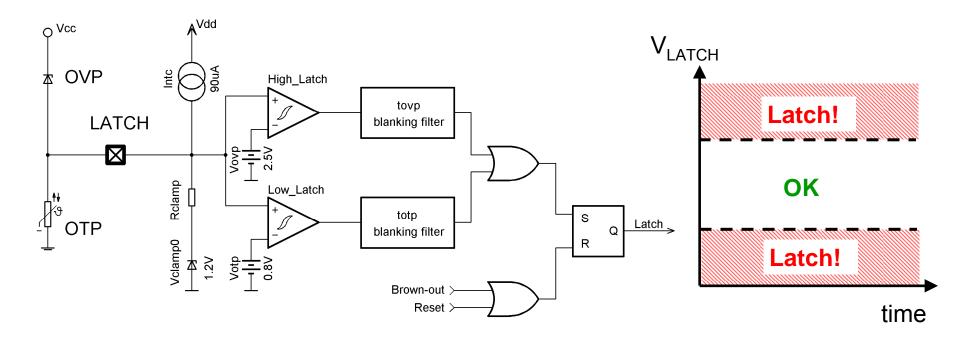

- High-voltage current source with built-in Brown-out and mains OVP

- Freq. reduction in light load conditions and skip mode

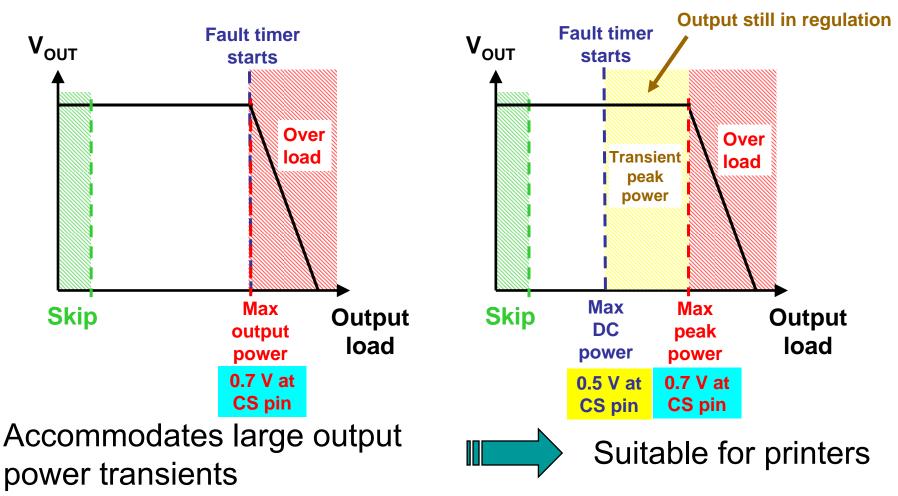

- Adjustable Over Power Protection

#### **Others Features**

- Latch-off input for severe fault conditions, allowing direct connection of NTC

- Timer-based protection: auto-recovery or latched

- Dual OCP option available

- Built-in ramp compensation

- Frequency jittering for a softened EMI signature

- Vcc operation up to 30 V

#### Market & Applications

- AC-DC adapters for notebooks, LCD monitor, game console, printers

- CE applications (DVD, STB)

#### **Application Data**

Avail. in Q1 2010

O, DW

|          | DSS     | Dual<br>OCP | Latch | Auto<br>Recovery |

|----------|---------|-------------|-------|------------------|

| NCP1237A | Yes     | Yes         | Yes   |                  |

| NCP1237B | Yes     | Yes         |       | Yes              |

| NCP1238A | Yes     | No          | Yes   |                  |

| NCP1238B | Yes     | No          |       | Yes              |

| NCP1287A | HV only | Yes         | Yes   |                  |

| NCP1287B | HV only | Yes         |       | Yes              |

| NCP1288A | HV only | No          | Yes   |                  |

| NCP1288B | HV only | No          |       | Yes              |

Various options available depending upon end applications needs

#### **Ordering & Package Information**

- NCP1237/38xDR2G NCP1287/88xDR2G

- SOIC-7 2500p per reel

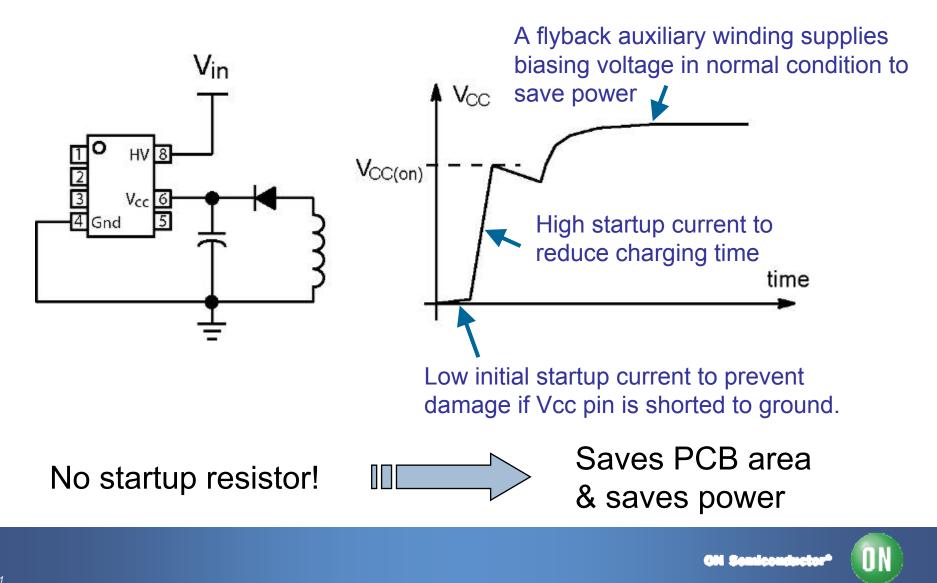

### NCP1237/38/87/88 – Built-in Startup FET

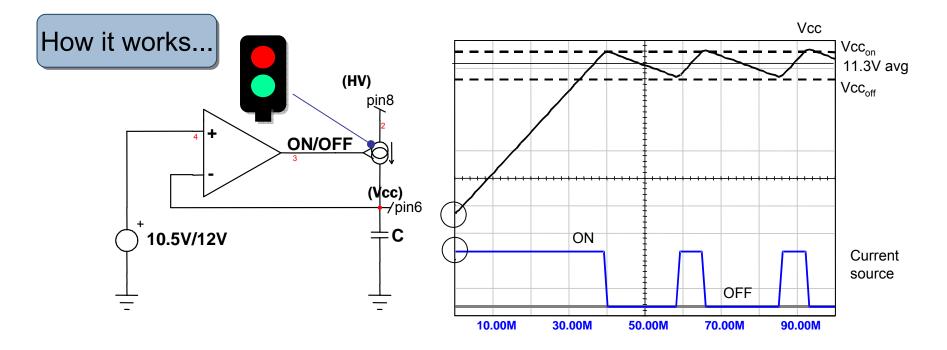

#### NCP1237/38/87/88 – Dynamic Self Supply (Optional)

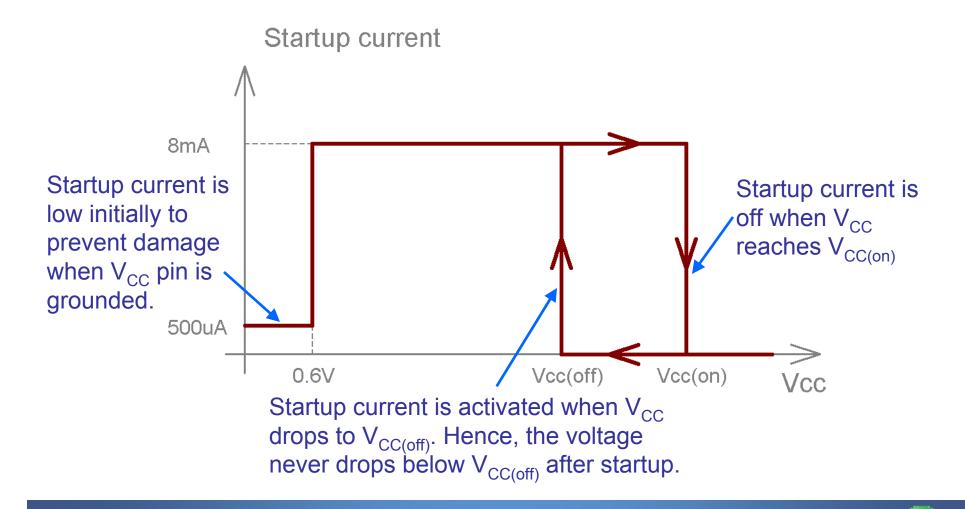

Power ON  $\rightarrow$  Current Source turns ON  $\rightarrow$  V<sub>cc</sub> is rising; no output pulses V<sub>cc</sub> reaches Vcc<sub>(on)</sub>  $\rightarrow$  Current Source turns OFF  $\rightarrow$  V<sub>cc</sub> is falling; output is pulsing V<sub>cc</sub> falls to Vcc<sub>(off)</sub>  $\rightarrow$  Current Source turns ON  $\rightarrow$  V<sub>cc</sub> is rising; output is pulsing

Dynamic Self-Supply

No need of auxiliary winding!

l Semiconductor\*

#### NCP1237/38/87/88 – Dual Startup Current Level

**IN Semiconductor**

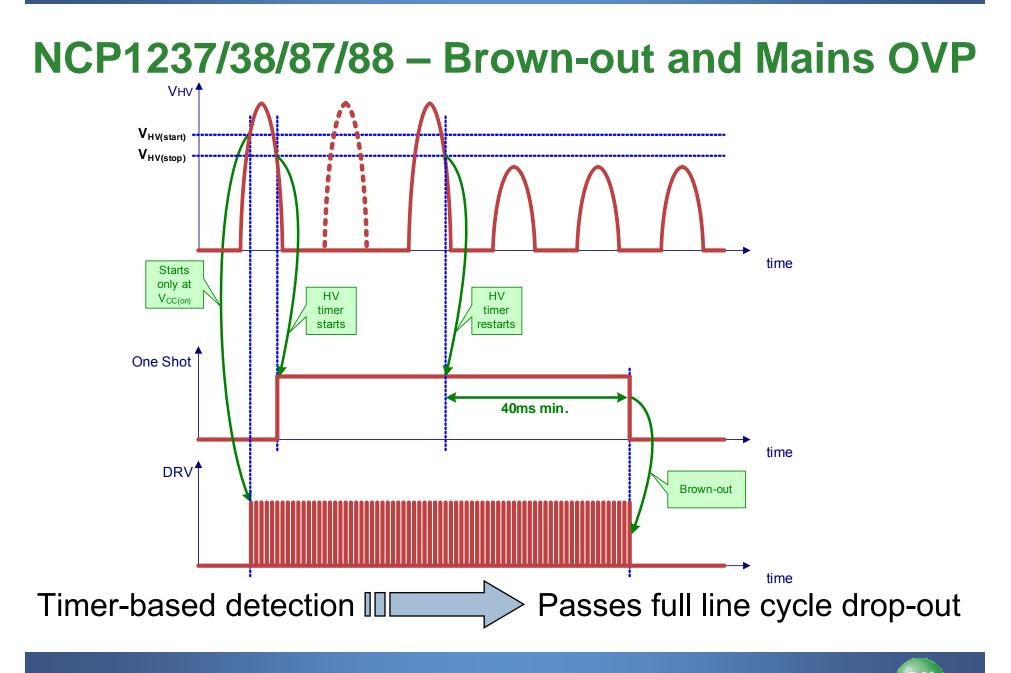

### NCP1237/38/87/88 – Brown-out and Mains OVP

Detection independent of Ripple on HV pin

Can be connected to the half-wave rectified ac line

N Semiconductor\*

N Semiconductor

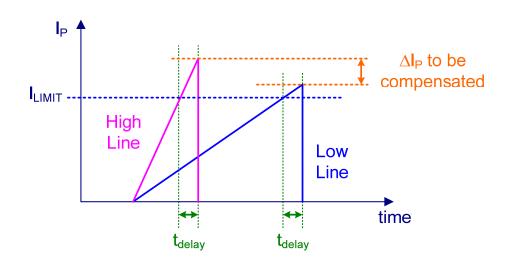

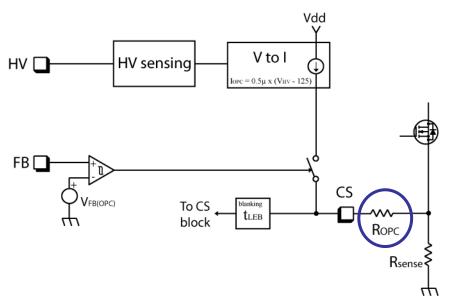

### NCP1237/38/87/88 – Over Power Protection

*Need to compensate for the effect of the propagation delay*

The compensation current creates an offset on the Current Sense signal

Over Power Protection

Maximum output power clamped

### NCP1237/38/87/88 – Dual OCP Threshold

These protections use the Up/Down counters, like classical analog integration.

N Semiconductor\*

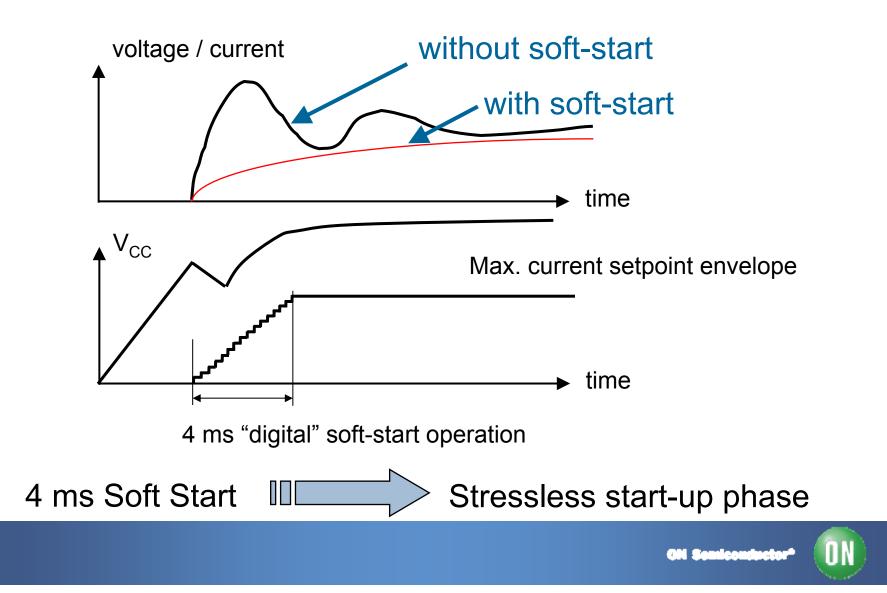

### NCP1237/38/87/88 - 4 ms Soft Start

### NCP1237/38/87/88 – Frequency Foldback

19

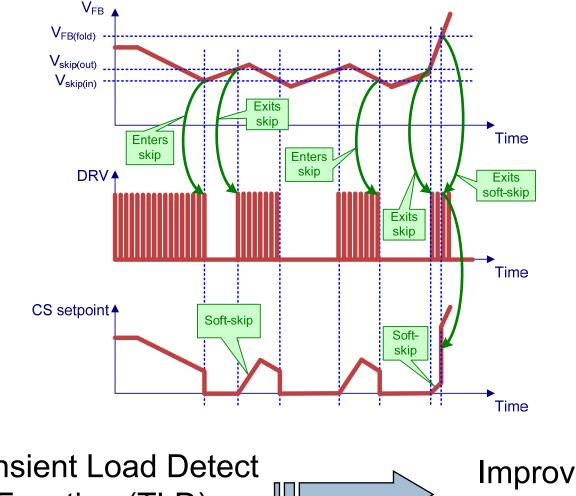

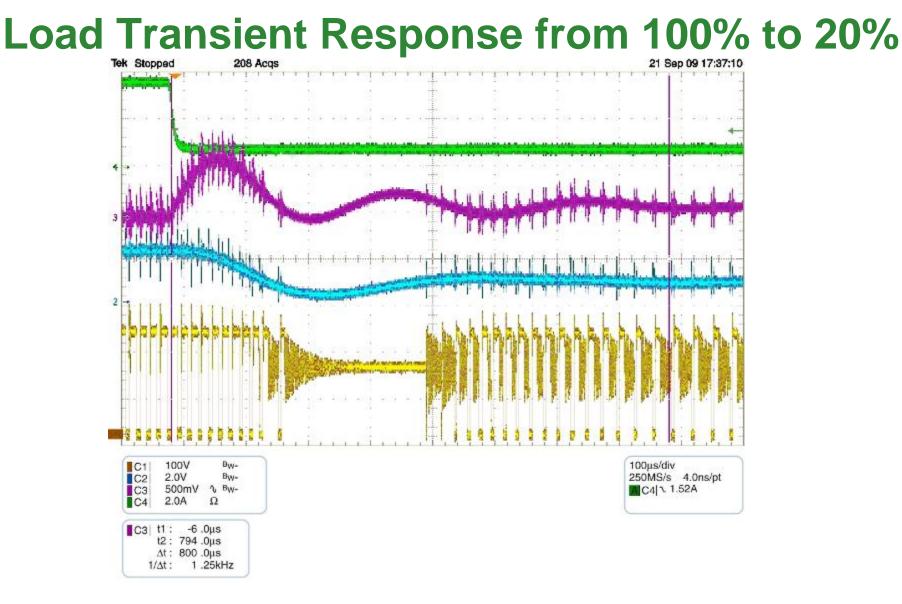

#### NCP1237/38/87/88 – Recover from Standby

Soft-Skip mode is left as soon as the voltage on the feedback pin reaches the TLD threshold

**Transient Load Detect** Function (TLD)

Improved Load Transient response time

#### NCP1237/38/87/88 – Latch-off Protection

An NTC thermistor can be directly connected to the IC

Less external components needed

N Semiconductor

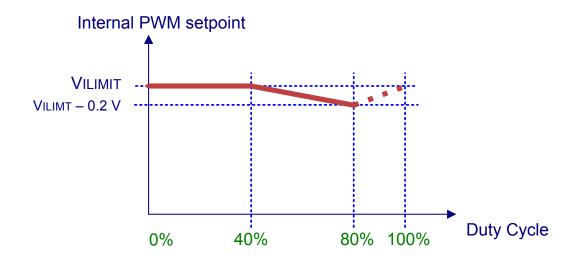

### NCP1237/38/87/88 – Slope Compensation

- There is a built in slope compensation with no external setting

- The internal slope compensation is activated if the duty cycle is higher than 40%

- The amount of slope compensation is 5mV/% observed at CS pin

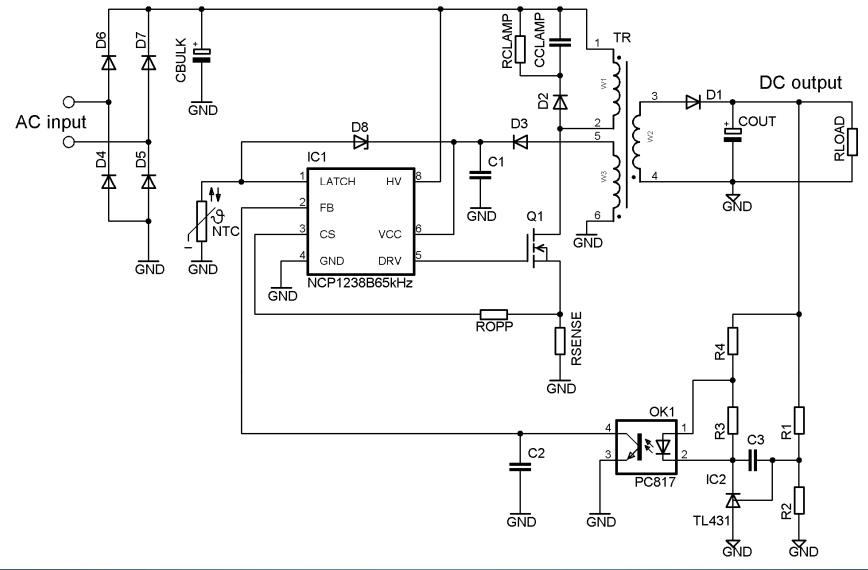

#### **Application Schematic**

**ON Semiconductor**<sup>\*</sup>

ON

## Agenda

- New ENERGY STAR<sup>®</sup> requirements

- Needed features to meet the new specification

- New controller family NCP1237/38/87/88

- Design step 1: Power stage

- Design step 2: Set the compensations

- Design step 3: No Load Input Power

- Design step 4: Magnetics

- Design step 5: EMI

- Preliminary demo board example

- Conclusion

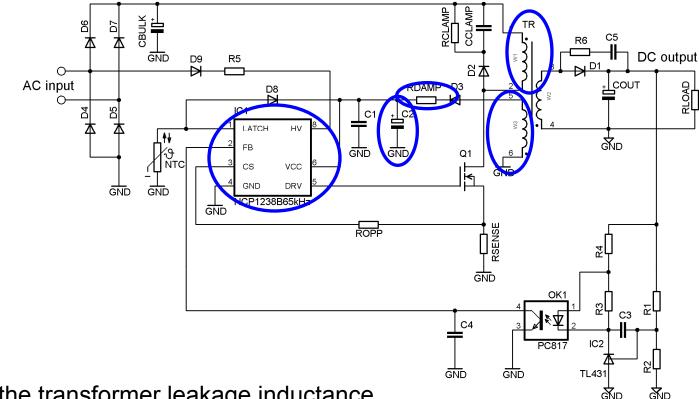

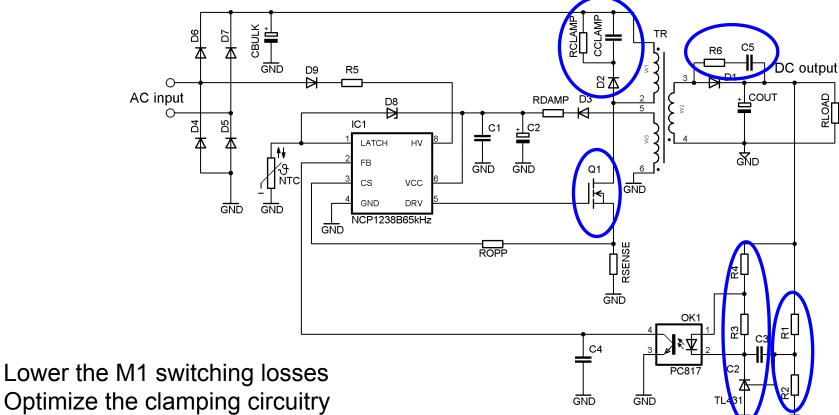

#### **Power stage: Schematic of Flyback Converter**

DN Semiconductor\*

#### **Power Stage Design: Bulk Capacitor**

• Output power P<sub>out</sub>

Average input current I<sub>in,avg</sub>

$$P_{out} = V_{out} \cdot I_{out}$$

$$I_{in,avg} = \frac{P_{in}}{V_{bulk,\min}}$$

- Estimation of input power P<sub>in</sub>

- Bulk capacitor value C<sub>bulk</sub>

$$C_{bulk} = \frac{I_{in,avg} \cdot t_{dis}}{\Delta V_{bulk}}$$

Semiconductor\*

$$P_{in} = \frac{P_{out}}{\eta}$$

D

Estimate the  $\eta$  based on the EPA standard

**ON Semiconductor**<sup>4</sup>

ON

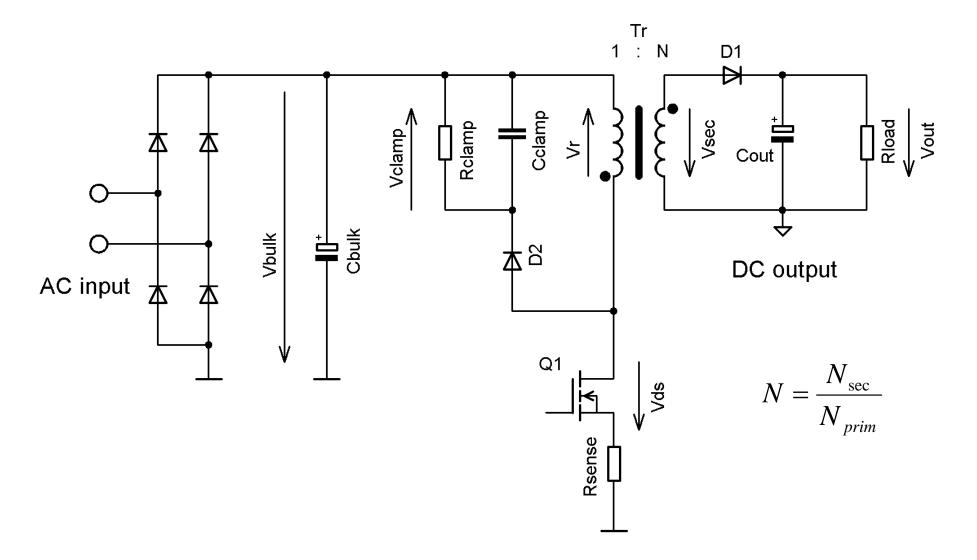

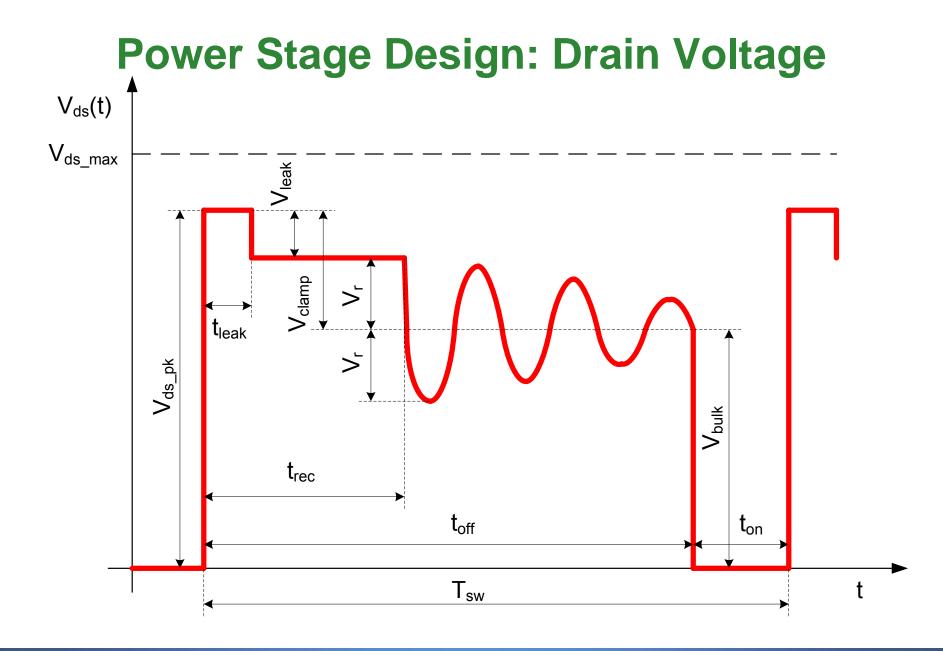

#### **Power Stage Design: Transformer Ratio**

Transformer ratio – consideration of the  $V_{DSS}$  of used Q1

$$N = \frac{k_C \cdot \left(V_{out} + V_{f,diode}\right)}{0.85 \cdot V_{DS,max} - 20V - V_{bulk,max}} \qquad k_C = \frac{V_{clamp}}{V_r}$$

The 20V means margin for clamping diode turning-on overshoot.

Reflected voltage V<sub>r</sub> at primary from secondary

$$V_{r} = \frac{V_{out} + V_{f,diode}}{N} \qquad \qquad N = \frac{N_{sec}}{N_{prim}}$$

Maximum duty cycle  $\mathrm{DC}_{\mathrm{max}}$

In CCM operation:

In DCM operation doesn't depend on N:

$$DC_{\max} = \frac{V_r}{V_r + V_{bulk,\min}} \qquad DC_{\max} = \frac{V_{out}}{V_{bulk,\min}} \cdot \sqrt{\frac{2 \cdot L_{prim} \cdot F_{sw}}{R_{load,\min}}}$$

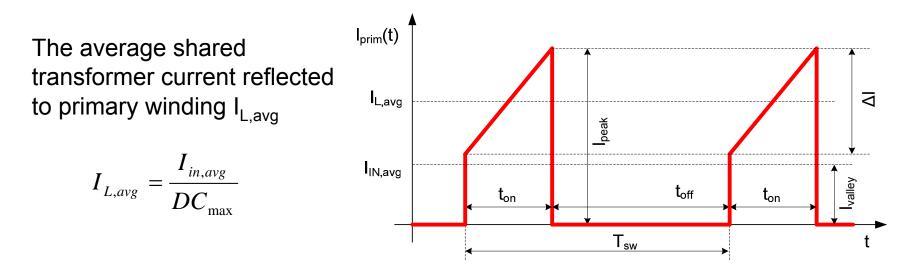

#### **Power Stage Design: Current Ripple**

Choose the relative ripple  $\delta I_r$ : it affects the operation in the CCM or DCM

- For universal AC input design use the  $\delta$  Ir in range 0.5 to 1.0 ٠

- For European AC input use the  $\delta$  Ir in range 0.8 to 1.6 ٠

$$\Delta I = \delta I_r \cdot I_{L,avg}$$

$$\Delta I = I_r - I_r$$

$$I = I_{peak} - I_{valley}$$

$$I_{peak} = I_{L,avg} \cdot \left(1 + \frac{\delta I_r}{2}\right)$$

$$I_{valley} = I_{L,avg} \cdot \left(1 - \frac{\delta I_r}{2}\right)$$

$\delta I_r = \frac{\Delta I}{I_{L,avg}}$

#### **Power Stage Design: Primary Inductance**

Transformer primary winding inductance L<sub>prim</sub>

$$L_{prim} = \frac{V_{bulk,\min} \cdot DC_{\max}}{F_{sw} \cdot \Delta I}$$

Maximum RMS value of the current flowing through primary winding Iprim.RMS

$$I_{primRMS} = \sqrt{DC_{max} \cdot \left(I_{peak}^{2} - I_{peak} \cdot \Delta I + \frac{\Delta I^{2}}{3}\right)}$$

Maximum RMS value of the current flowing through secondary winding  $I_{sec,RMS}$

$$I_{\text{sec, peak}} = \frac{I_{\text{peak}}}{N} \qquad \Delta I_{\text{sec}} = \frac{\Delta I}{N}$$

$$I_{\text{sec, RMS}} = \sqrt{\left(1 - DC_{\text{max}}\right) \cdot \left(I_{\text{sec, peak}}^2 - I_{\text{sec, peak}} \cdot \Delta I_{\text{sec}} + \frac{\Delta I_{\text{sec}}^2}{3}\right)}$$

#### **Power Stage Design: Q1 Selection**

Conduction loss at Q1 should be approx. 1% of the Pout

$$R_{DSon} \leq \frac{P_{out}}{100 \cdot I_{prim,RMS}^{2}}$$

Then the right device is chosen by parameters V<sub>DSmax</sub>, I<sub>peak</sub>, t<sub>on</sub>, t<sub>off</sub>

Current sensing resistor  $R_{sense}$  selection

$$R_{sense} = \frac{V_{ILIM}}{1.1 \cdot I_{peak}} \qquad P_{sense} = I_{primRMS}^{2} \cdot R_{sense}$$

The 1.1 factor means 10% margin for  $L_{prim}$  and other parameters spread, to be able to deliver maximum power.

N Semiconductor\*

#### **Power Stage Design: Secondary Rectification**

#### D1 selection:

Reflected voltage across D1

$PIV = V_{bulk, \max} \cdot N + V_{out}$

The next important parameters for D1 selection are  $I_{sec,peak}$ ,  $I_{out}$  and the fast and soft recovery

#### **Cout selection:**

Minimum C<sub>out</sub> value

$$C_{out} \geq \frac{I_{out} \cdot DC_{\max}}{V_{out,ripple} \cdot F_{sw}}$$

The maximum allowed ESR of  $C_{out}$

$$ESR \leq \frac{V_{out,ripple}}{I_{sec,peak}} \quad \text{Dominant part}$$

$$T_{Cout,rms} = \sqrt{I_{sec,rms}^2 - I_{out}^2}$$

it is recommended to use more parallel  $C_{out}$  for lowering the output voltage ripple.

32

#### **Power Stage Design: Clamping Network**

TVS – losses in the suppressor: better at no load conditions

$$P_{clamp} = E_{clamp} \cdot F_{sw} = \frac{1}{2} \cdot L_{leak} \cdot I_{peak}^{2} \cdot F_{sw} \cdot \frac{V_{clamp}}{V_{clamp} - V_{r}}$$

RCD clamp – 1<sup>st</sup> iteration:

better EMI response

$$R_{clamp} = \frac{2 \cdot V_{leak} \cdot V_{clamp}}{L_{leak} \cdot I_{peak}^{2} \cdot F_{sw}}$$

$$P_{clamp} = \frac{V_{clamp}^{2}}{R_{clamp}}$$

$$C_{clamp} > rac{V_{clamp}}{V_{ripple} \cdot R_{clamp} \cdot F_{sw}}$$

These values need to be optimized for the no load consumption and losses in slow clamping diode D2

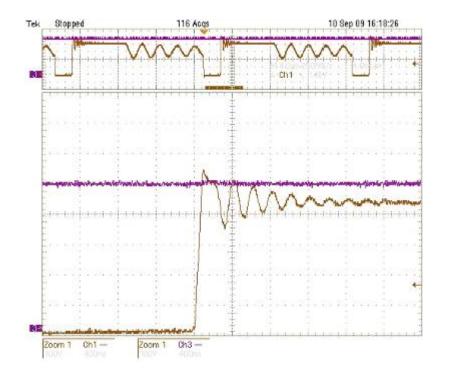

#### **TVS vs RCD Clamp Comparison**

Drain voltage ringing with TVS as clamp

Drain voltage ringing with RCD as clamp

Different R<sub>damp</sub> used in clamp

M Semiconductor\*

### Agenda

- New ENERGY STAR<sup>®</sup> requirements

- Needed features to meet the new specification

- New controller family NCP1237/38/87/88

- Design step 1: Power stage

- Design step 2: Set the compensations

- Design step 3: No Load Input Power

- Design step 4: Magnetics

- Design step 5: EMI

- Preliminary demo board example

- Conclusion

## **Over Power Compensation**

The overpower compensation affects the primary peak current, by the following formula:

$$I_{PEAK} = \frac{V_{CS\,\text{int}}}{R_{sense}} + V_{bulk} \cdot \left(\frac{t_{PROP}}{L_P} - g_{OPP} \cdot \frac{R_{OPP}}{R_{sense}}\right) + V_{off} \cdot g_{OPP} \cdot \frac{R_{OPP}}{R_{sense}}$$

Then the overpower compensation resistor can be calculated:

$$R_{OPP} = \frac{t_{PROP} \cdot R_{sense}}{L_P \cdot g_{OPP}}$$

The over power compensating resistor affects only the  $I_{peak}$  value, but in CCM the output power is given by the following formula, where  $I_{valley}$  plays a role:

$$P_{out} = \frac{1}{2} \cdot \eta \cdot L_{prim} \cdot F_{sw} \cdot \left(I_{peak}^{2} - I_{valley}^{2}\right)$$

N Semiconductor\*

#### **2<sup>nd</sup> Level Over Power Protection**

The overpower compensation affects the 2<sup>nd</sup> level over power protection by the addition of bulk voltage feed forward.

$$I_{TRAN} = \frac{V_{CStran}}{R_{sense}} - \left(V_{bulk} - V_{off}\right) \cdot g_{OPP} \cdot \frac{R_{OPP}}{R_{sense}}$$

The overpower compensation can be used for reducing the transformer size to  $\frac{1}{2}$  and keeping the peak power capability.

## **Spread Sheet Design of OPC**

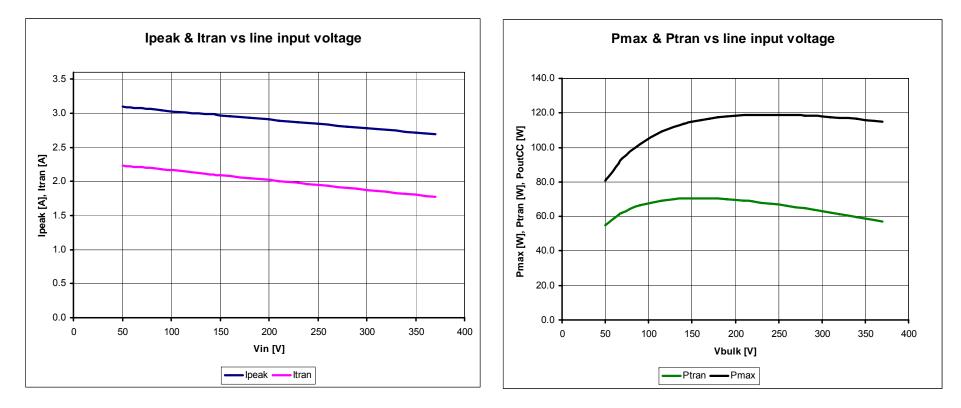

OPC design spread sheet was created and the user can choose the right  $R_{OPP}$  and it's effect to  $I_{peak}$ ,  $I_{tran}$ ,  $P_{out}$  and  $P_{tran}$ :

Inputs:

| Output voltage             | Vout [V]     | 19    |

|----------------------------|--------------|-------|

| Primary turns              | N1 [-]       | 100   |

| Secondary turns            | N2 [-]       | 25    |

| Ramp Comp at CS            | RaCo [mV/%]  | 5     |

| Maximum int set point      | Vilimit [V]  | 0.7   |

| Sensing resistor           | Rsense [Ohm] | 0.235 |

| Propagation delay          | tprop [ns]   | 100   |

| Primary inductance         | Lp [uH]      | 560   |

| Vin to lopp ratio          | gopp [uS]    | 0.5   |

| Over power comp resistor   | Ropp [Ohm]   | 680   |

| Switching frequency        | Fsw [kHz]    | 65    |

| 2nd level overcurrent prot | Vcstran [V]  | 0.5   |

Will be available soon, while NCP1237/38/87/88 will be released

# **Spread Sheet Design of OPC**

Keeping constant  $I_{peak}$  in CCM mode tends to  $I_{valley}$  decreasing with increasing the Vin. That's why the maximum output deliverable power  $P_{out}$  increases with increasing Vin. Choose the right compensation.

## **Loop Compensation**

Download the work sheet at:

http://www.onsemi.com/pub/Collateral/FLYBACK DWS.XLS.ZIP

# Agenda

- New ENERGY STAR<sup>®</sup> requirements

- Needed features to meet the new specification

- New controller family NCP1237/38/87/88

- Design step 1: Power stage

- Design step 2: Set the compensations

- Design step 3: No Load Input Power

- Design step 4: Magnetics

- Design step 5: EMI

- Preliminary demo board example

- Conclusion

### **No Load Input Power Reducing Approach**

- Decrease the transformer leakage inductance

- Use the controller IC with the frequency foldback and skip mode features

- Do not allow the DSS operation (Vcc cap increase)

- In case of low Vcc and high aux winding leakage increase the aux number of turns to disable the DSS

- Decrease the value of the Vcc damping resistor (may affect the EMI)

## **No Load Input Power Reducing Approach**

- Reduce the losses in the secondary rectifier and its snubber

- Decrease the TL431 biasing

- Decrease the cross current through the feedback resistor divider

- Set a stable operation for all loading currents

- Do not use the output voltage indication LED

٠

٠

# Agenda

- New ENERGY STAR<sup>®</sup> requirements

- Needed features to meet the new specification

- New controller family NCP1237/38/87/88

- Design step 1: Power stage

- Design step 2: Set the compensations

- Design step 3: No Load Input Power

- Design step 4: Magnetics

- Design step 5: EMI

- Preliminary demo board example

- Conclusion

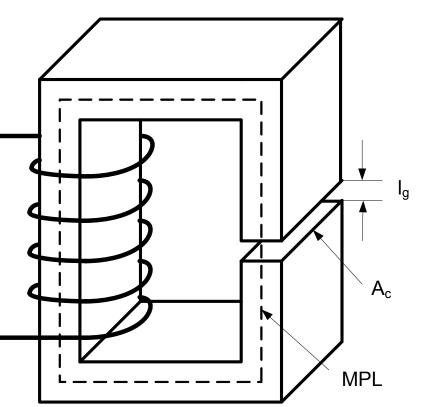

## Area Product A<sub>P</sub>

- There is defined the area product  $A_P [m^4]$

- Product of effective window area W<sub>a</sub> [m<sup>2</sup>] and iron cross section area A<sub>c</sub> [m<sup>2</sup>]

$$A_P = W_a \cdot A_c$$

- Allows fast, effective and optimal magnetic design

- Should be published in core datasheet

## **Window Utilization Factor Ku**

Ku is a measure of the amount of copper that appears in the window area of transformer. This window utilization factor is affected by:

- 1) Wire insulation

- 2) Wire lay (fill factor)

- 3) Bobbin area

- 4) Insulation required for multilayer windings or between windings

Typical values lay in range 0.35 to 0.48

# The Load Coefficient K<sub>load</sub>

- Flux density in magnetic should be designed at I<sub>peak</sub> with some margin (5%) to avoid saturation

- Do you really need 100% lout for 100% time??

# If not, decrease core size!!

$$K_{load} = \frac{I_{out,RMS}}{I_{out,RMS,\max}}$$

Example:

- Maximum DC output current is 3.5 A, but it's only needed for transients

- The long term RMS value is only 1.75 A (at least 10 min.)

- Loading coefficient is only 0.5 (not 1) → core size is smaller

→ losses in core and in copper are smaller

## **Flyback Transformer Core Sizing**

The core size can be calculated by the  $A_P$  factor in case of these inputs:

- 1. Converter parameters:  $L_{prim}$ ,  $I_{peak}$ ,  $K_{load}$ ,  $\delta I_r$ ,  $DC_{max}$

- 2. Core maximum flux density  $B_{max}$  considered with the hysteresis and eddy current losses at switching frequency  $F_{sw}$

- 3. Winding parameters (utilization factors for primary and secondary windings  $Ku_{prim}$ ,  $Ku_{sec}$ ), (current densities in primary and secondary windings  $J_{prim}$ ,  $J_{sec}$

$$A_{P} = \frac{L_{prim} \cdot I_{peak}^{2}}{B_{max}} \cdot K_{load} \cdot \left(\frac{\sqrt{DC_{max}}}{J_{prim}} + \frac{\sqrt{1 - DC_{max}}}{J_{sec}} \cdot Ku_{sec}\right) \cdot \sqrt{\frac{\delta I_{r}^{2} + 12}{3 \cdot (\delta I_{r} + 2)^{2}}}$$

Now the appropriate core can be selected from the vendor products list by the  $A_{\rm P}$  factor .

## **Windings Design**

• Number of turns of primary winding

$$NT_{prim} = \frac{L_{prim} \cdot I_{peak}}{B_{max} \cdot A_{c}}$$

• Number of turns of secondary winding

$NT_{\rm sec} = N \cdot NT_{\it prim}$

• Number of turns of auxiliary winding

$$NT_{aux} = \frac{V_{CC} + V_{f,Vcc}}{V_{out} + V_{f,diode}} \cdot NT_{sec}$$

N Semiconductor\*

# Air Gap Length I<sub>g</sub>

$$l_g = \frac{N \cdot \mu_0 \cdot I_{peak}}{B_{max}} - \frac{MPL}{\mu_r}$$

of

$$l_g \ll MPL$$

MPL – core magnetic path length

- $\mu_0$  permeability of vacuum

- $\mu_{\rm r}~$  permeability of core

In case an EE, RM or pot core is used, divide the calculated  $I_g$  by factor 2, because your core has 2 air gaps in magnetic path

# Agenda

- New ENERGY STAR<sup>®</sup> requirements

- Needed features to meet the new specification

- New controller family NCP1237/38/87/88

- Design step 1: Power stage

- Design step 2: Set the compensations

- Design step 3: No Load Input Power

- Design step 4: Magnetics

- Design step 5: EMI

- Preliminary demo board example

- Conclusion

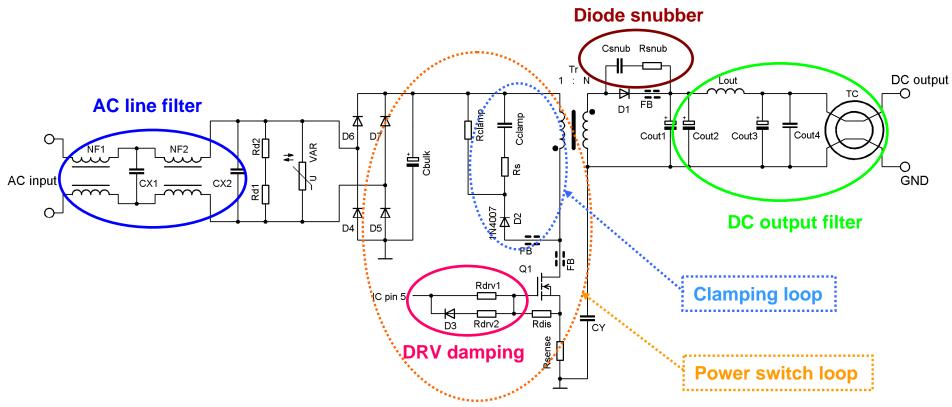

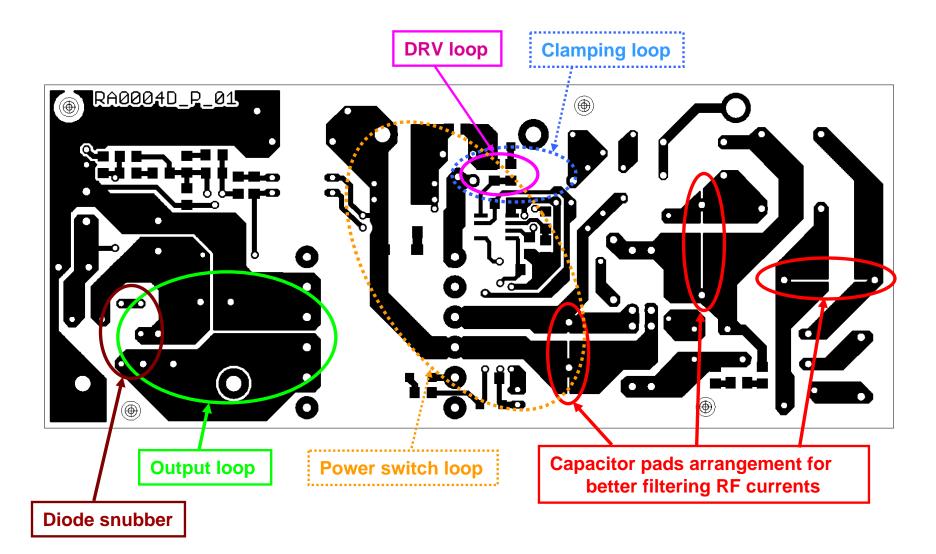

# How to improve EMI of my design?

- All switching loops with RF currents should have small area

- Divide input AC filter at two chokes to decrease the parasitic capacitance coupling

- CY closes the current loop for the RF currents injected via transformer

## **Diode Snubber Design**

Snubber resistance value should be close to the characteristic impedance of ringing circuitry

$$R_{snubber} = \sqrt{\frac{L_{leak,SEC}}{C_d}}$$

inductance observed from

secondary side

$$C_d - reverse direction diodecapacitance$$

Luckoro –the transformer leakage

• RC time constant of the snubber should be small compared to the switching period but long compared to the voltage rise time

$$C_{snubber} \approx 3 \div 4 \cdot C_d$$

ON Semiconductor\*

#### **PCB Layout Tips**

# Agenda

- New ENERGY STAR<sup>®</sup> requirements

- Needed features to meet the new specification

- New controller family NCP1237/38/87/88

- Design step 1: Power stage

- Design step 2: Set the compensations

- Design step 3: No Load Input Power

- Design step 4: Magnetics

- Design step 5: EMI

- Preliminary demonstration board example

- Conclusion

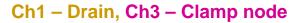

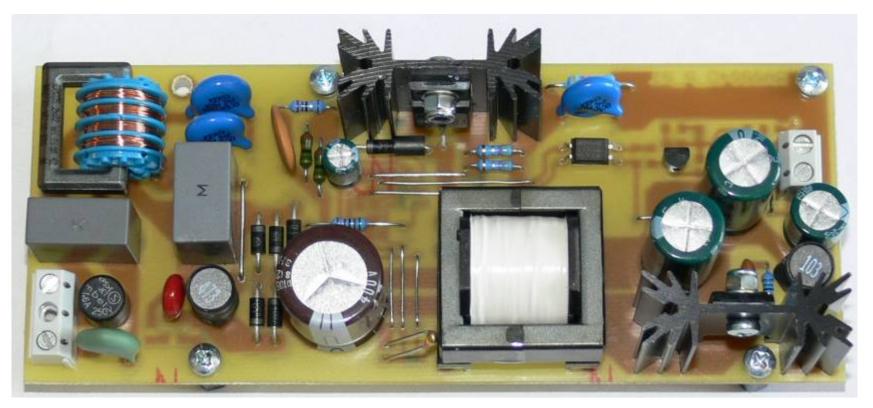

#### **Preliminary Demonstration Board**

#### A typical 65 W notebook adapter (19 V output)

#### (optimized for EPS 2.0)

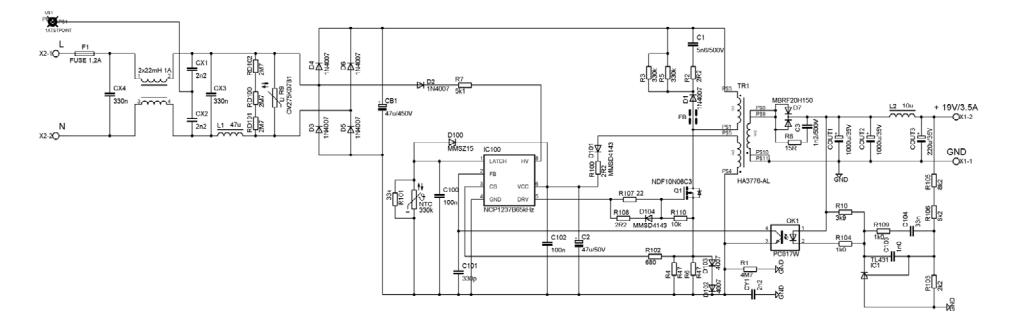

#### **Schematic of Preliminary Demonstration Board**

A typical 65 W notebook adapter (19 V output)

#### (optimized for EPS 2.0)

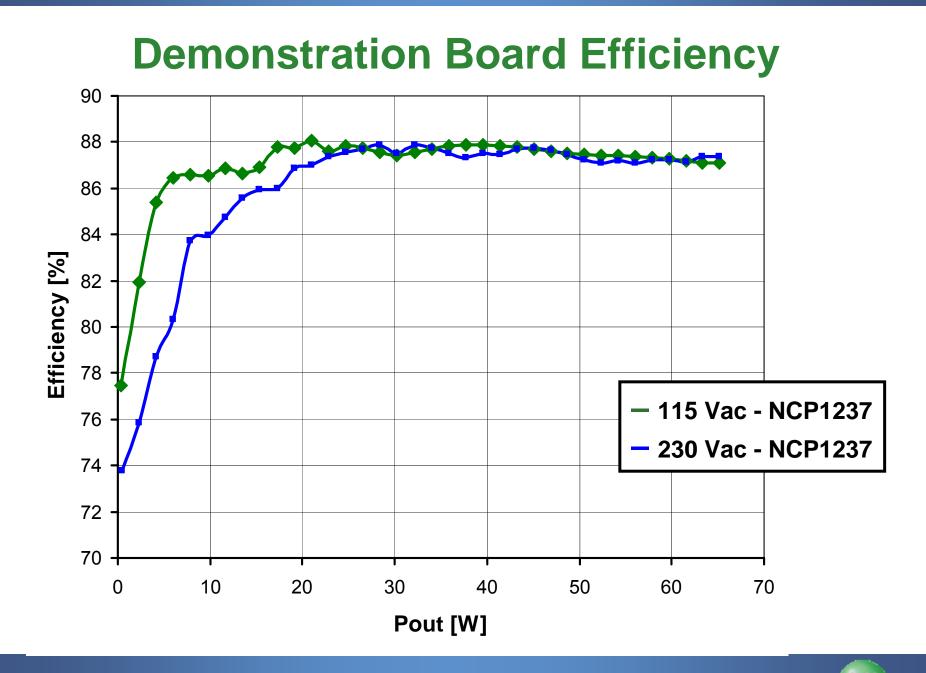

#### Demonstration Board Efficiency (Measured with DC Cord)

The DC cord length is 1.05m and copper cross sec. is 0.75mm<sup>2</sup>

| $V_{\rm IN}$ % of P <sub>OUTnom</sub> | 115 Vac/60Hz | 230 Vac/60Hz |

|---------------------------------------|--------------|--------------|

| 100 %<br>(65 W)                       | 87.10 %      | 87.37 %      |

| 75 %<br>(49 W)                        | 87.52 %      | 87.63 %      |

| 50 %<br>(32 W)                        | 87.54 %      | 87.88 %      |

| 25 %<br>(16 W)                        | 87.79 %      | 85.96 %      |

Average at 115Vac is 87.32% and at 230 Vac is 87.21 %

### **Demonstration Board Standby Power**

Light load and no load input power with the NCP1237

| V <sub>IN</sub><br>P <sub>OUT</sub> | 115 Vac/60 Hz | 230 Vac/50 Hz |

|-------------------------------------|---------------|---------------|

| 10 %<br>(6.5 W)                     | 86.55 %       | 83.74 %       |

| 5 %<br>(3.3 W)                      | 85.40 %       | 78.72 %       |

| 1 %<br>(0.65 W)                     | 77.49 %       | 73.77 %       |

| No load                             | 51.1 mW       | 73.5 mW       |

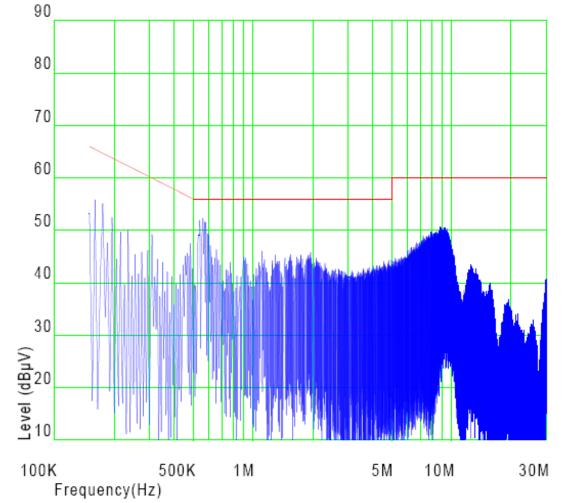

#### **Demonstration Board Conducted EMI**

80% of full load (2.72 A) at 230 V/50 Hz NCP1237B 65 kHz

┛╾┥┥┶┶┶┼┼┶┶┙┢┎┥┥┥┙┥┥┥┥┥┥┫╝┥┥┙┥┥┿╸┙┥╠┓╸┥┥╸╸┙┪┥┥┥┥╺┟┥╴╸

2.0ms/div 125MS/s 8.0ns/pt C1 5.8V

R1 11 : 93.2kHz 12: 105.4kHz ∆f: 12.21kHz

**ON Semiconductor**<sup>4</sup>

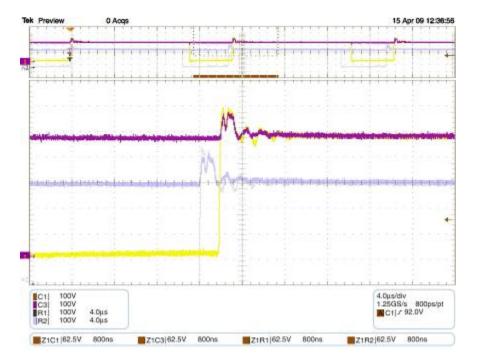

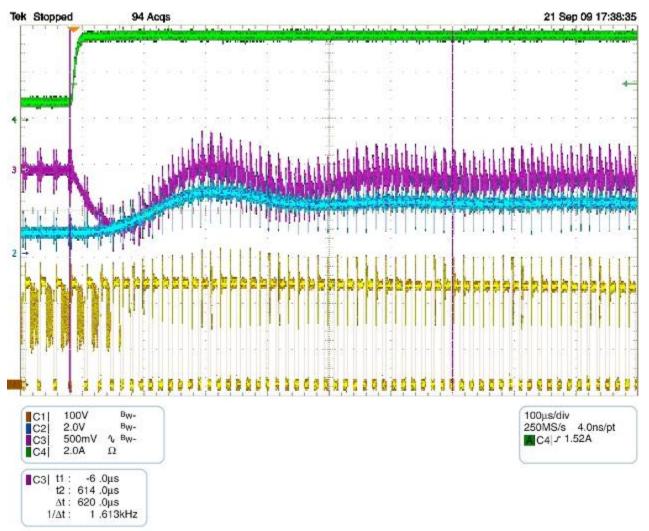

### Load Transient Response from 20% to 100%

Ch1 – Drain, Ch2 – FB, Ch3 – Vout (AC coupling), Ch4 - lout

NI Semiconductor

Ch1 – Drain, Ch2 – FB, Ch3 – Vout (AC coupling), Ch4 - lout

**ON Semiconductor**

# Agenda

- New ENERGY STAR<sup>®</sup> requirements

- Needed features to meet the new specification

- New controller family NCP1237/38/87/88

- Design step 1: Power stage

- Design step 2: Set the compensations

- Design step 3: No Load Input Power

- Design step 4: Magnetics

- Design step 5: EMI

- Preliminary demo board example

Conclusion

# Conclusion

- Meeting the most recent requirements from ENERGY STAR<sup>®</sup> or IEC is possible with the classical <u>Flyback</u> converter

- The new controller NCP1237/37/87/88 with frequency foldback and skip-mode at light load makes it possible

- Average efficiencies above <u>87%</u> are possible

- No-load input power below <u>**300 mW</u>** is possible</u>

- No-load input power below <u>100 mW</u> is achievable, although the controller alone cannot ensure this. The whole power supply must be designed to reduce power waste.

## **For More Information**

- View the extensive portfolio of power management products from ON Semiconductor at <u>www.onsemi.com</u>

- View reference designs, design notes, and other material supporting the design of highly efficient power supplies at <u>www.onsemi.com/powersupplies</u>