#### **Features**

- Cell Balance Controller for Li-ion, LiFePO<sub>4</sub>

Battery Pack

- Active Charge Balance

- Automatic Synchronous Work

- Programmable Separated Balancing and Detecting Time

- Constant Off-time Modulation

- Balancing Current Operate in CCM

- External On/Off Control

- Programmable Working Voltage

- Over Temperature Protection

- Manage 1% Voltage Difference Between Two Cells

- Off Current under 1uA

- SOP-16 Package

## **Applications**

- Portable Consumer Electronics

- Electric traffic tools(E-Bike, E-Car)

- Hand-Held Tools

### **General Description**

The GS7708 is a cell balance controller design for Li-ion/LiFePO<sub>4</sub> battery Pack, especially for high capacity battery and high balancing current applications.

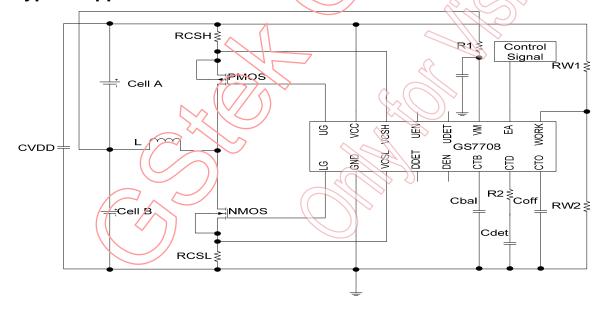

The GS7708 uses inductor to reserve energy and drives an external PMOS and an external NMOS for energy diversion between two cells. The balancing current can be set by external components L, Rcs and Coff as shown in figure 1.

To get the accurate voltage of battery, The GS7708 will stop balancing when detecting. The length of balancing time and detecting time can be set by external capacitors Cbal and Cdet as shown in figure 1.

For N cells balancing, there must be N-1 GS7708 working in a series. All the chips can synchronous working automatically, which eliminate interference of voltage detection in detecting time. Programmable working voltage function helps users

to define the minimal voltage of two cells to start balance.

External On/Off Control makes GS7708 compatible with MCU controlled BMS.

# **Typical Application**

Figure 1 Typical Application Circuit of GS7708

This document is GStek's confidential information. Anyone having confidential obligation to GStek shall keep this document confidential. Any unauthorized disclosure or use beyond authorized purpose will be considered as violation of confidentiality and criminal and civil liability will be asserted.

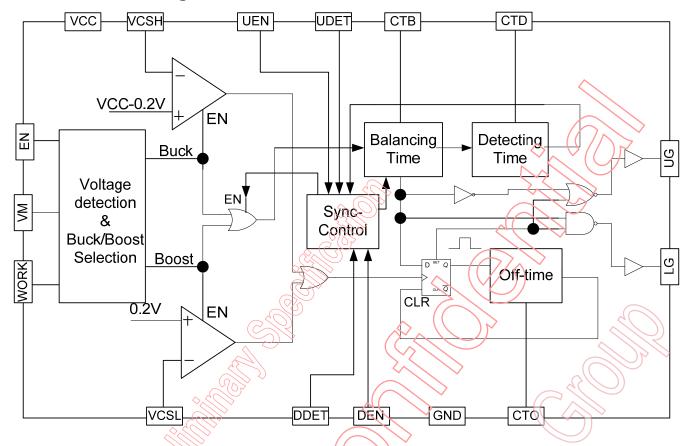

# **Function Block Diagram**

Figure 2 Function Block Diagram

# **Ordering Information**

| No | Item     | Contents                |

|----|----------|-------------------------|

| 1  | Package  | SO: SOP-16              |

| 2  | Shipping | R. Tape & Reel, T: Tube |

Example: GS7708 SOP-16 Tape & Reel ordering information is "GS7708SO-R"

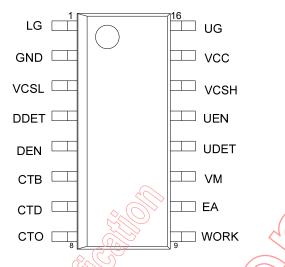

# **Pin Configuration**

Figure 3, SOP-16 Package

## **Pin Descriptions**

| Pin Descri    | ptions |                |                                                       |

|---------------|--------|----------------|-------------------------------------------------------|

| No.<br>SOP-16 | Name   | I/O type       | Rin Function                                          |

| 1             | LG     |                | Gate driver of external NMOSFET                       |

| 2             | GND    | 0,00           | Ground pin.                                           |

| 3             | VCSL   | ı              | Sense the low-side peak current                       |

| 4             | DDET   | ı              | Synchronous pin for receiving lower-side chip signal. |

| 5             | DEN    | 0              | Synchronous pin for enabling lower-side chip.         |

| 6             | СТВ    | 0              | Setting balancing time by a capacitor connect to gnd. |

| 7             | CTD    | 0              | Setting detecting time by a capacitor connect to gnd. |

| 8             | СТО    | (Q             | Setting off-time by a capacitor connect to gnd.       |

| 9             | WORK   |                | Setting the starting voltage for cell balancing       |

| 10            | EA     | $_{\sim}(()/)$ | Chip enable pin                                       |

| 11            | VM     |                | Battery voltage sensing pin                           |

| 12            | UDET   |                | Synchronous pin for receiving upper-side chip signal. |

| 13            | UEN    | 0              | Synchronous pin for enabling upper-side chip.         |

| 14            | VCSH   | ı              | Sense the high-side peak current                      |

| 15            | vcc    | I/O            | Chip power supply                                     |

| 16            | UG     | 0              | Gate driver of external PMOSFET                       |

**Absolute Maximum Rating (Note 1)**

| Parameter                                         | Symbol                                | Limits                 | Units |

|---------------------------------------------------|---------------------------------------|------------------------|-------|

| VCC to GND                                        | V <sub>VCC</sub>                      | -0.3 ~14               | V     |

| Analogy Output Voltage                            | $V_{CTB}, V_{CTD}, V_{CTO}$           | -0.3 ~6                | V     |

| Analogy Output Voltage                            | $V_{UG}, V_{LG}$                      | -0.3~ V <sub>VCC</sub> | V     |

| Analogy Output Voltage                            | V <sub>UEN</sub> , V <sub>DEN</sub>   | -0.37 VVCC             | ٧     |

| Analogy Input Voltage                             | V <sub>VCSL</sub> , V <sub>WORK</sub> | 0.3~6                  | V     |

| Analogy Input Voltage                             | VDDET, VEA, VVM, VUDET, VVCSH         | -0.3~ V <sub>VCC</sub> | V     |

| Package Power Dissipation at T <sub>A</sub> ≤25°C | P <sub>D_SOP-16</sub>                 | 1000                   | mW    |

| Junction Temperature Range                        | T,                                    | -45 ~ 150              | °C    |

| Storage Temperature Range                         | T <sub>STG</sub>                      | -65 ~ 150              | °C    |

| Lead Temperature (Soldering, 10sec)               | TLEAD                                 | 260                    | %C    |

| ESD (Human Body Mode) (Note 2)                    | Vesd_HBM                              | 2K                     | X     |

| ESD (Machine Mode) (Note 2)                       | V <sub>ESD_MM</sub>                   | 200                    | V     |

Thermal Information (Note 3)

| Parameter                              | Symbol                 | Limits | Units |

|----------------------------------------|------------------------|--------|-------|

| Thermal Resistance Junction to Ambient | O <sub>JA_SOP-16</sub> | 100    | °C/W  |

Recommend Operating Condition (Note 4)

| Parameter            | Symbol           | Limits     | Units |

|----------------------|------------------|------------|-------|

| VCC to GND           | V <sub>vcc</sub> | 5 ~ 8.4    | V     |

| Junction Temperature | 17               | - 40 ~ 125 | °C    |

| Ambient Temperature  | T <sub>A</sub>   | -40 to 85  | °C    |

# **Electrical Characteristics**

(VCC =6.5V, VGND=0V,  $T_A = 25$ °C, unless noted.)

| Parameter                  | Symbol              | Conditions          | Min  | Тур                   | Max | Units |

|----------------------------|---------------------|---------------------|------|-----------------------|-----|-------|

| Supply Voltage Section     |                     |                     |      |                       |     |       |

| VDD operation voltage      | VDD                 |                     | 5    |                       | 8.4 | V     |

| IC off current             | loff                |                     |      | $\Diamond_{\Diamond}$ |     | uA    |

| IC operation current       | lop                 | Balancing, =200KHz  |      | 10                    |     | mA    |

| To operation outlett       | 101                 | Static              | <    |                       | 600 | uA    |

| Enable On/Off Control      |                     |                     |      |                       |     |       |

| Turn on threshold          | V <sub>ON</sub>     | T=-40°C~125°C       | 2    |                       | C   | V     |

| Turn off threshold         | VoFF                | 140 0 123 0         |      |                       | 0.8 |       |

| Programmable Working Vol   | tage                |                     | >    |                       |     |       |

| Working threshold voltage  | V <sub>WK</sub>     |                     |      | 1                     |     | V     |

| Hysteresis                 | $V_{WKHYS}$         |                     |      | 100                   |     | mV    |

| Timing Section             |                     |                     | ٥,(( |                       |     |       |

| CT_BAL threshold voltage   | V <sub>CT_BAL</sub> |                     |      | 2                     |     | V     |

| CT_BAL source current      | CT_BAL              |                     |      | 10                    |     | uA    |

| CT_DET threshold voltage   | ACT DEL             |                     | )    | 2                     |     | ٧     |

| CT_DET source current      | CT_DET              |                     |      | 10                    |     | uA    |

| CT_OFF threshold voltage   | VCT_OFF             |                     |      | 2                     |     | ٧     |

| CT_OFF source current      | I <sub>CT_OFF</sub> |                     |      | 10                    |     | uA    |

| Current Sense Section      |                     |                     |      |                       |     |       |

| VCSH turn point voltage    | $V_{CSH}$           | 'VCC-VCSH'          |      | 200                   |     | mv    |

| VCSL turn point voltage    | $V_{CSL}$           |                     |      | 200                   |     | mv    |

| Leading edge blanking time | $T_LEB$             | Guarantee by design |      | 300                   |     | ns    |

| Propagation delay to turn off                                                           | $T_{PDH}$           | VCSH PIN                           |      | 130  |             | ns |

|-----------------------------------------------------------------------------------------|---------------------|------------------------------------|------|------|-------------|----|

| the Gate                                                                                | $T_PDL$             | VCSL PIN                           |      | 70   |             | ns |

| Gate Section                                                                            |                     |                                    |      |      |             |    |

|                                                                                         | $T_RH$              | High-side Gate,C <sub>L</sub> =3nF |      | 25   |             | ns |

| Rising Time                                                                             | $T_RL$              | Low-side Gate,C <sub>L</sub> =3nF  |      | 25   |             | ns |

| Falling Time                                                                            | $T_FH$              | High-side Gate,C <sub>L</sub> =3nF |      | 25   |             | ns |

| T dilling Tillic                                                                        | $T_{FL}$            | Low-side Gate,C <sub>L</sub> =3nF  | Ç    | 25   | <b>&gt;</b> | ns |

| Dead Time                                                                               | $T_DH$              | High to Low,C <sub>L</sub> =3nF    |      | 10   |             | ns |

| Dead Time                                                                               | T <sub>DL</sub>     | Low to High,C <sub>L</sub> =3nF    |      | 10   |             | ns |

| SYN Control (Note 5)                                                                    |                     |                                    |      |      |             |    |

| UEN sink current                                                                        | IUEN                |                                    |      | -120 |             | uA |

| DEN source current                                                                      | IDEN                |                                    |      | 120  |             | uA |

| UDET sink current                                                                       | ludet               |                                    |      | -90  |             | uA |

| DDET source current                                                                     | IDDET               |                                    | < (( | 90   | :           | uA |

| Balancing Function                                                                      |                     |                                    |      |      |             |    |

| Balancing function start when the difference voltage of two cells greater than V UBAL   | V <sub>UBA</sub> I. |                                    |      | )    | 0.01*VCC    | mV |

| The difference voltage of two cells is less than V_BAL when balancing function finished | Уваь                |                                    |      |      | 0.007*VCC   | mV |

| Over Temperature Protection                                                             |                     |                                    |      |      |             |    |

| Threshold Temperature                                                                   | Тотр                |                                    |      | 150  |             | °C |

| Hysteresis                                                                              | Thys                |                                    |      | 30   |             | °C |

| Threshold Temperature                                                                   | Тотр                |                                    |      |      |             |    |

Note 1. Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note 2. Devices are ESD sensitive. Handling precaution recommended.

- **Note 3.**  $\theta_{JA}$  is measured in the natural convection at  $T_A$ =25°C on a high effective thermal conductivity test board (4 Layers, 2S2P) of JEDEC 51-7 thermal measurement standard.

- **Note 4.** The device is not guaranteed to function outside its operating conditions.

- Note 5. Negative value means current flow into this pin.

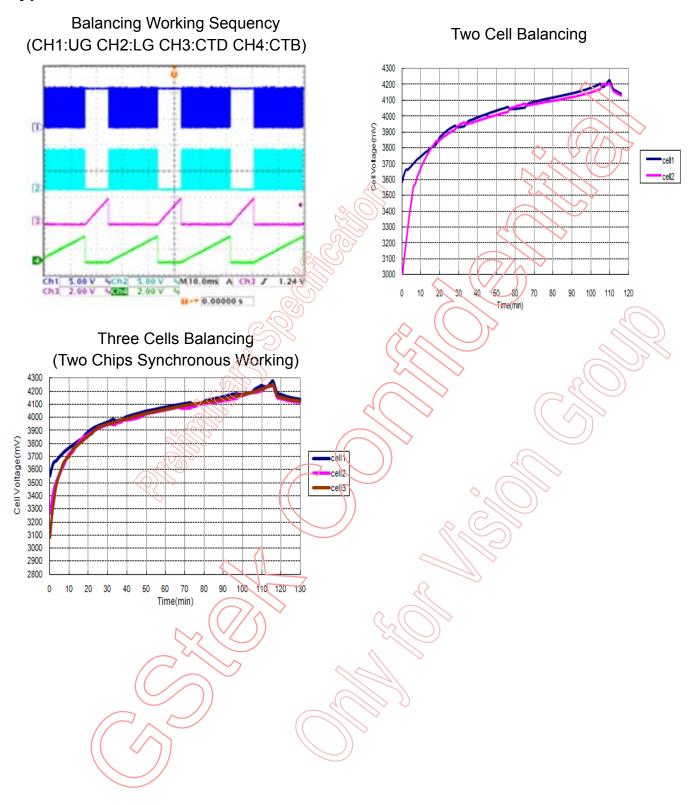

# **Typical Performance**

8

## **Functional Descriptions**

#### **EA On/Off Control**

The GS7708 is turned off when  $V_{EA}$ <0.8V and consume under 1uA current; GS7708 is turned on when  $V_{EA}$ >2V.

#### **Programmable Working Voltage**

The starting voltage of balancing function can be programmed in GS7708. User may define it by adjusting RW1 and RW2. The defined starting voltage is

$$V_{defined} = V_{WK}^* (1 + RW1/RW2)$$

For example, if RW1=40k $\Omega$ , RW2=10k $\Omega$ , then the defined working voltage is 5V.

#### **Cell Balance Movements**

The GS7708 drives a PMOS switch which is in parallel with the upper cell and a NMOS switch which is in parallel with the lower one.

The GS7708 turns on the PMOS switch first when the upper cell voltage is higher than the lower one, otherwise, it turns on the NMOS switch first if the lower cell voltage is higher.

#### Separated Detection and Balance

The GS7708 will stop balancing when detecting the middle voltage of two cells, thus, the interference caused by balancing current can be avoided, a much more reliable battery voltage we could get for the next period of balancing.

#### Programmable Balancing Time

The balancing time of GS7708 can be programmed by capacitor  $C_{\text{Bal}}$  seen in fig. 1. The timing current of CTB pin is  $V_{\text{CT\_BAL}}$ , the threshold voltage is  $V_{\text{CT\_BAL}}$ , thus

$$T_{Bal} = (C_{Bal} * V_{CT\_BAL}) / I_{CT\_BAL}$$

### **Programmable Detecting Time**

The same as balancing time, the detecting time of GS7708 can be programmed by capacitor  $C_{Det}$   $T_{Det}=(C_{Det}*V_{CT\ DET})/I_{CT\ DET}$

#### **Programmable Off-time**

The GS7708 is off-time modulation, the off-time can be programmed by capacitor  $C_{\text{Off}}$  seen in Figure 1.

#### **Balancing Current Design**

To design the balancing current, the balancing current waveform (peak and ripple) should be determined first,

$$||\mathbf{f}_{\text{Balance}}||_{\text{peak}} - ||\mathbf{f}_{\text{ripple}}||_{2}$$

(1)

For example, a 4.5A balancing current with peak current 6A, ripple 3A and frequency is 200KHz, assume the voltage of each cell is 3.2V, thus, the off-time T<sub>OFF</sub> is 1/21, 2.5us,

$$R_{CS} = V_{CS} I_{peak} = 0.2/6 = 33 \text{m}\Omega \tag{3}$$

$$L = \sqrt{c_{\text{cell}} + c_{\text{cell}}} = 3.2 \times 2.5 \text{ u/3} = 2.67 \text{ uH}$$

(4)

Make sure that the balancing current is operating in CCM.

### Synchronous Control

To eliminate interference of voltage detection in detecting time, the GS7708 can automatic synchronous balancing and detecting while two or more chips working together. This function is realized by connecting UDET, UEN pin to DEN, DDET pin of the upper chip and connecting DEN, DDET pin to UDET, UEN pin of the lower one.

The max number  $N_{MAX}$  of GS7708 that can work in a series is determined by the SYN control time and the propagation delay time of SYN signals. Assume UEN rising delay time (or DEN fall delay

time) is  $T_{OD}$  and UEN falling delay time (or DEN rise delay time) is  $T_{CD}$ , usually  $T_{OD} < T_{CD}$ , thus

$$N_{MAX} = T_{CLOSE SYN} / T_{CD} + 1$$

(1)

If T<sub>OD</sub>>T<sub>CD</sub> for special reasons, then

$$N_{MAX} = T_{OPEN SYN} / T_{OD} + 1$$

(2)

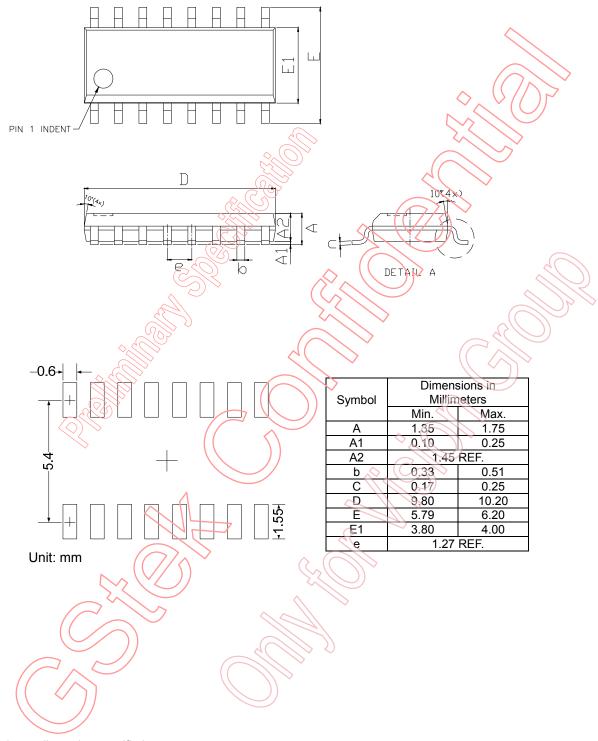

## **Package Dimensions, SOP-16**

<u>Note</u>

1. Min.: Minimum dimension specified.

2. Max.: Maximum dimension specified.

3. REF.: Reference. Normal/Regular dimension specified for reference.

Please read the notice stated in this preamble carefully before Admission e accessing any contents of the document attached. Admission of GStek's statement therein is presumed once the document is released to the receiver.

Notice:

Firstly, GREEN SOLUTION CO., LTD. (GStek) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its information herein without notice. And the aforesaid information does not form any part or parts of any quotation or contract between GStek and the information receiver.

Further, no responsibility is assumed for the usage of the aforesaid information. GStek makes no representation that the interconnect of its circuits as described herein will not infringe on exiting or future patent rights and other intellectual property rights, nor do the descriptions contained herein express or imply that any licenses under any GStek patent right, copyright, mask work right, or other GStek intellectual property right relating to any combination, machine, or process in which GStek products or services are used.

Besides, the product in this document is not designed for use in life support appliances, devices, or systems where malfunction of this product can reasonably be expected to result in personal injury. GStek customers' using or selling this product for use in such applications shall do so at their own risk and agree to fully indemnify GStek for any damage resulting from such improper use or sale.

At last, the information furnished in this document is the property of GStek and shall be treated as highly confidentiality; any kind of distribution, disclosure, copying, transformation or use of whole or parts of this document without duly authorization from GStek by prior written consent is strictly prohibited. The receiver shall fully compensate GStek without any reservation for any losses thereof due to its violation of GStek's confidential request. The receiver is deemed to agree on GStek's confidential request therein suppose that said receiver receives this document without making any expressly opposition. In the condition that aforesaid opposition is made, the receiver shall return this document to GStek immediately without any delay.