# 80V Half Bridge Gate Driver

## **General Description**

The RT9622 is an 80V gate driver designed to drive both the high side and low side N-MOSFET in a half-bridge configuration or a synchronous Buck. The high side driver is capable of working with rail voltage up to 80V. The input of the driver is compatible with standard TTL logic level. The internal level shifter design enables the RT9622 to operate at high speed while providing clean transitions under high dv/dt noise circumstances. The RT9622 is available in a small SOP-8 package.

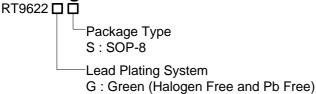

## **Ordering Information**

#### Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

## **Marking Information**

RT9622GS: Product Number

YMDNN: Date Code

### **Features**

- High Voltage Driver Up to 80V

- 500mA Driving Current

- Output in Phase with Input

- Independent Control for High/Low Side Gates

- TTL Compatible Input Controls

- VCC and VB Operate from 10V to 20V

- Small SOP-8 Package

- RoHS Compliant and Halogen Free

## **Applications**

- E-Bike Drivers

- Half-Bridge and Full-Bridge Converters

- Push-Pull Converters

- Synchronous Buck Converters

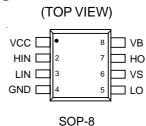

## **Pin Configurations**

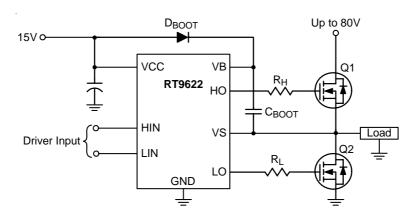

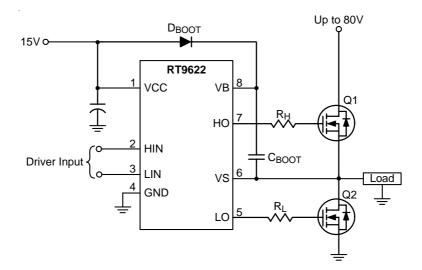

## **Simplified Application Circuit**

Copyright ©2012 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                                         |  |  |

|---------|----------|----------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | VCC      | Power Supply Input. Connect a low ESR capacitor from this pin to GND f good bypass.                                  |  |  |

| 2       | HIN      | Logic Input for High Side Gate Driver. It is pulled low by an internal $500k\Omega$ resistor if it is not connected. |  |  |

| 3       | LIN      | Logic Input for Low Side Gate Driver. It is pulled low by an internal $500k\Omega$ resistor if it is not connected.  |  |  |

| 4       | GND      | Ground.                                                                                                              |  |  |

| 5       | LO       | Output of Low Side Gate Driver.                                                                                      |  |  |

| 6       | VS       | Switch Node.                                                                                                         |  |  |

| 7       | НО       | Output of High Side Gate Driver.                                                                                     |  |  |

| 8       | VB       | Bootstrap for High Side Gate Driver. Connect a $1\mu F$ capacitor between the VB and VS pins.                        |  |  |

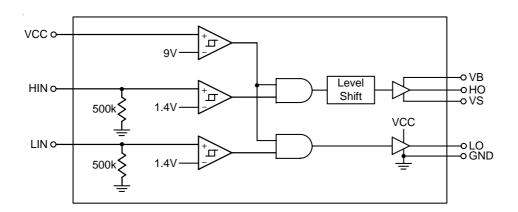

# **Function Block Diagram**

# Absolute Maximum Ratings (Note 1)

| Supply Voltage, VCC                                                         | - −0.3V to 25V                   |

|-----------------------------------------------------------------------------|----------------------------------|

| Bootstrap Voltage, VB                                                       | V <sub>CC</sub> to 95V           |

| • Switch Voltage, VS                                                        | $(V_B - 10V)$ to $(V_B + 0.3V)$  |

| • High Side Output, HO                                                      | $(V_S - 0.3V)$ to $(V_B + 0.3V)$ |

| • Low Side Output, LO                                                       | $-0.3V$ to $(V_{CC} + 0.3V)$     |

| • Inputs HIN, LIN                                                           | - −0.3V to 10V                   |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                                  |

| SOP-8                                                                       | · 0.625W                         |

| Package Thermal Resistance (Note 2)                                         |                                  |

| SOP-8, $\theta_{JA}$                                                        | - 160°C/W                        |

| Junction Temperature                                                        |                                  |

| • Lead Temperature (Soldering, 10 sec.)                                     | · 260°C                          |

| Storage Temperature Range                                                   | - −65°C to 150°C                 |

| ESD Susceptibility (Note 3)                                                 |                                  |

| HBM (Human Body Mode), Except HO & LO Pin                                   | · 2kV                            |

| MM (Machine Mode)                                                           | · 200V                           |

|                                                                             |                                  |

| Recommended Operating Conditions (Note 4)                                   |                                  |

| Supply Voltage VCC, VBS                                                     | - 10V to 20V                     |

• Junction Temperature Range ------ -40°C to 125°C

• Ambient Temperature Range ------ -40°C to 85°C

## **Electrical Characteristics**

( $V_{CC} = 15V$ ,  $V_{BS} = V_B - V_S = 15V$ ,  $T_A = 25^{\circ}C$ , unless otherwise specified)

| Parameter                               |            | Symbol                  | Test Conditions         | Min | Тур                      | Max | Unit |  |

|-----------------------------------------|------------|-------------------------|-------------------------|-----|--------------------------|-----|------|--|

| VCC Supply Voltage                      |            |                         |                         |     |                          |     |      |  |

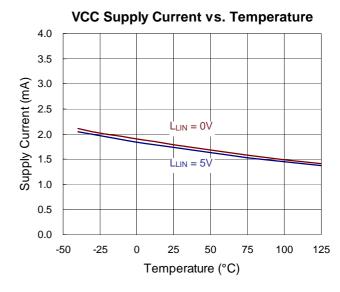

| Supply Current                          |            | I <sub>VCC_H</sub>      | V <sub>LIN</sub> High   |     | 1.8                      |     | mA   |  |

|                                         |            | I <sub>VCC_L</sub>      | V <sub>LIN</sub> Low    |     | 1.8                      |     |      |  |

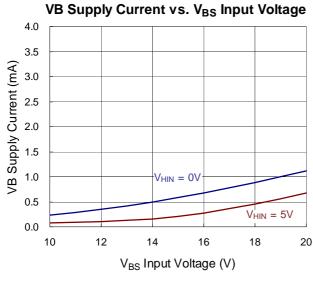

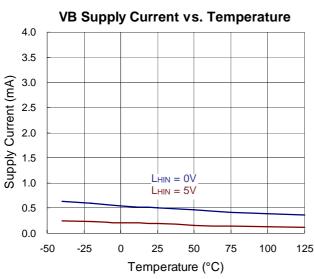

|                                         |            | I <sub>VB_H</sub>       | V <sub>HIN</sub> High   |     | 0.2                      |     |      |  |

|                                         |            | I <sub>VB_L</sub>       | V <sub>HIN</sub> Low    |     | 0.5                      |     |      |  |

| VCC Under Voltage Lock Out Threshold    |            | V <sub>UVLO_VCC</sub>   |                         |     | 8.7                      |     | V    |  |

| VCC UVLO Hysteresis                     |            | ΔV <sub>UVLO</sub> _VCC |                         |     | 0.5                      |     | V    |  |

| VBS Under Voltage Lock Out<br>Threshold |            | V <sub>UVLO_BS</sub>    |                         |     | 7.1                      |     | V    |  |

| VBS UVLO Hysteresis                     |            | ΔV <sub>UVLO_BS</sub>   |                         |     | 0.4                      |     | V    |  |

| Inputs and Outputs                      |            |                         |                         |     |                          |     |      |  |

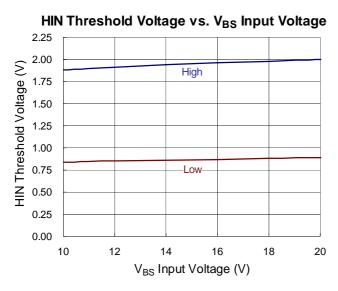

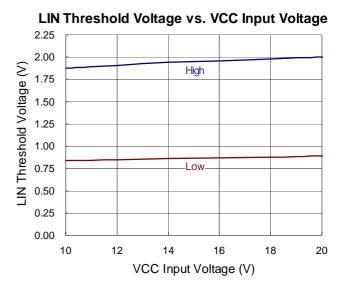

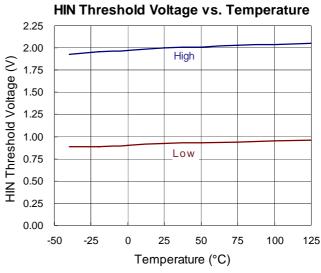

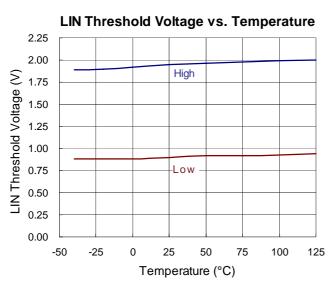

| HIN, LIN Input                          | Logic-High | V <sub>IH</sub>         |                         | 2.8 |                          |     | V    |  |

| Threshold Voltage                       | Logic-Low  | V <sub>IL</sub>         |                         |     |                          | 1.2 |      |  |

| HO Output Voltage                       | High-Level | V <sub>HO_H</sub>       | I <sub>HO</sub> = -10mA |     | V <sub>VB</sub><br>- 0.2 |     | · V  |  |

| Tio Output voltage                      | Low-Level  | V <sub>HO_L</sub>       | I <sub>HO</sub> = 10mA  |     | V <sub>VS</sub><br>+ 0.2 |     |      |  |

Copyright ©2012 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Parameter                        | Symbol                              | Test Conditions            | Min | Тур | Max | Unit |  |

|----------------------------------|-------------------------------------|----------------------------|-----|-----|-----|------|--|

| Input Current                    | I <sub>HIN</sub> , I <sub>LIN</sub> | $V_{HIN}$ , $V_{LIN} = 5V$ |     | 50  |     | μΑ   |  |

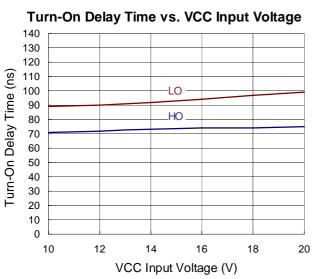

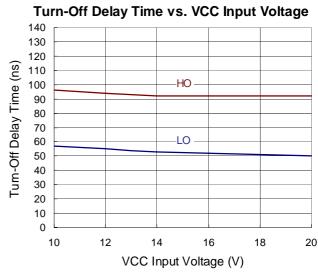

| HO Proposition Polov             | ton_ho                              | Low to High                |     | 70  |     | ns   |  |

| HO Propagation Delay             | toff_ho                             | High to Low                |     | 95  |     |      |  |

| LO Propagation Delay             | ton_lo                              | Low to High                |     | 90  |     | 20   |  |

| LO Propagation Delay             | toff_LO                             | High to Low                |     | 55  |     | ns   |  |

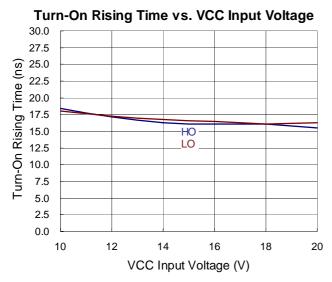

| Turn-On Rising Time (LO to HO)   | t <sub>r</sub>                      | C <sub>LOAD</sub> = 1nF    |     | 17  |     | ns   |  |

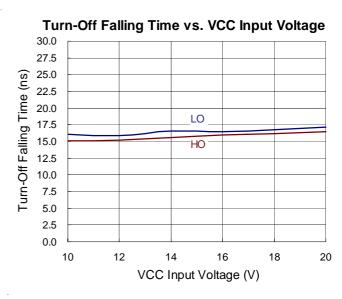

| Turn-Off Falling Time (HO to LO) | t <sub>f</sub>                      | C <sub>LOAD</sub> = 1nF    |     | 15  |     | ns   |  |

- Note 1. Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}$ C on a low effective thermal conductivity single-layer test board per JEDEC 51-3.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

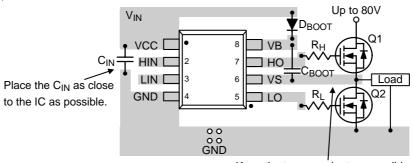

# **Typical Application Circuit**

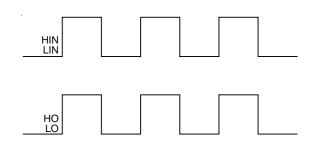

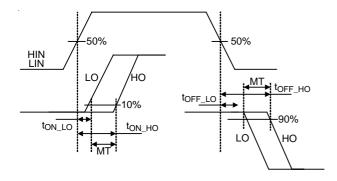

## **Timing Diagram**

Figure 1. Input/Output Timing Diagram

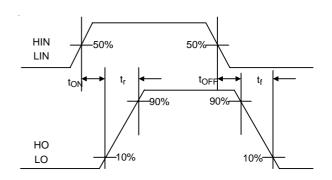

Figure 2. Switch Time Waveform Definitions

Figure 3. Delay Matching Waveform Definitions

Copyright ©2012 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

**RT9622**

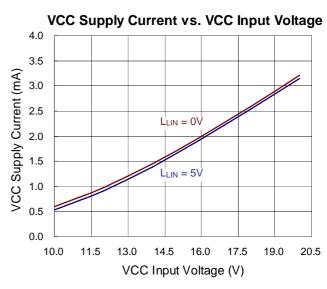

## **Typical Operating Characteristics**

Copyright ©2012 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Copyright ©2012 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

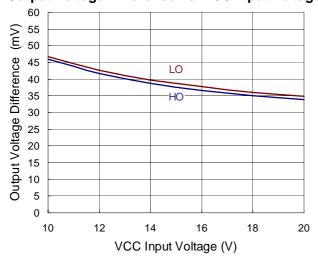

### **Output Voltage Difference vs. VCC Input Voltage**

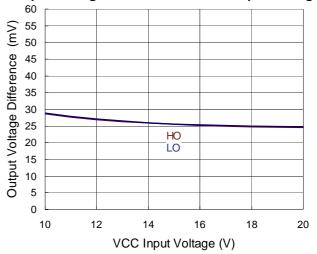

### Output Voltage Difference vs. VCC Input Voltage

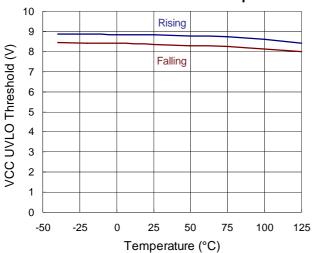

## VCC UVLO Threshold vs. Temperature

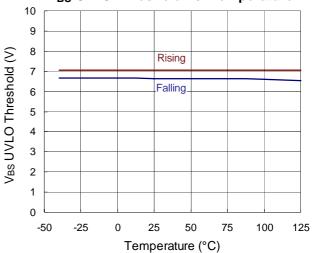

### **V<sub>BS</sub> UVLO Threshold vs. Temperature**

## **Application Information**

The RT9622 are designed to drive up to six MOSFET or IGBT power devices. The output that drives the gate of the external power switch is defined as HO for the high side power switch and LO for the low side power switch.

#### **Switching and Timing Relationships**

The relationship between the input and output signals of the RT9622 are illustrated in Figure 2. The definitions of several timing parameters ( $t_{ON}$ ,  $t_{OFF}$ , tr, and tf) associated with this device are showed in this figure.

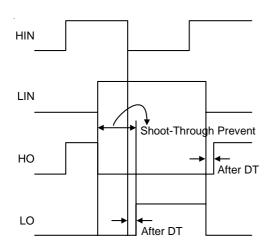

### **Dead Time and Shoot-Through Prevention**

In Figure 4, the RT9622 receives the input command to turn on both the high side and low side switches at the same time; as a result, the shoot-through protection of the RT9622 has prevented this condition and both the high side and low side outputs are held at off state.

The RT9622 features integrated dead time protection circuitry. The dead time is designed to be fixed (DT). A minimum dead time will be automatically inserted whenever the external dead time is shorter than DT.

Figure 4. Shoot-Through Prevention

#### **Under Voltage Lockout Protection**

The UVLO protection ensures that the RT9622 drives the external power devices only when the gate supply voltage is sufficient to fully turn on the power devices. Without this feature, when the gate of the external power switch is driven with a low voltage, resulting in the power switch conducting current while the channel impedance is high; this will result in a very high conduction loss within the power device and lead to power device failure.

#### **Thermal Considerations**

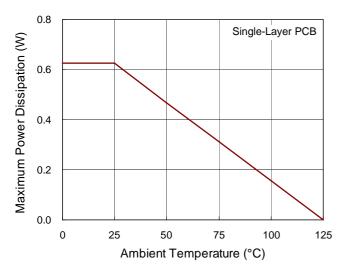

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For SOP-8 package, the thermal resistance,  $\theta_{JA}$ , is 160°C/W on a standard JEDEC 51-3 single-layer thermal test board. The maximum power dissipation at  $T_A=25^{\circ}C$  can be calculated by the following formula :

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (160^{\circ}C/W) = 0.625W$$

for SOP-8 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 5 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Copyright ©2012 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

**RT9622** Preliminary

Figure 5. Derating Curve of Maximum Power Dissipation

#### **Layout Consideration**

For best performance of the RT9622, the following layout guidelines must be strictly followed.

- VS node is with high frequency voltage swing and should be kept at small area. Keep the trace between high side MOSFET source, low side MOSFET drain and VS pin as short as possible.

- ▶ The trace from HO, LO to power MOSFET should be short to reduce the noise.

- ▶ Put the bypass capacitor C<sub>IN</sub> as close as possible to the VCC pin.

- ▶ The bootstrap capacitor (C<sub>BOOT</sub>) should be placed as close to the IC as possible.

Keep the trace as short as possible.

Figure 6. PCB Layout Guide

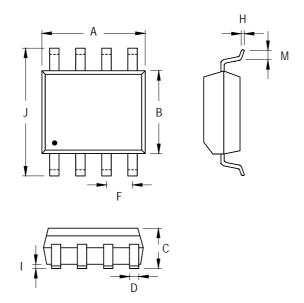

## **Outline Dimension**

| Symbol | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|--------|------------|----------------|----------------------|-------|--|

|        | Min        | Max            | Min                  | Max   |  |

| А      | 4.801      | 5.004          | 0.189                | 0.197 |  |

| В      | 3.810      | 3.988          | 0.150                | 0.157 |  |

| С      | 1.346      | 1.753          | 0.053                | 0.069 |  |

| D      | 0.330      | 0.508          | 0.013                | 0.020 |  |

| F      | 1.194      | 1.346          | 0.047                | 0.053 |  |

| Н      | 0.170      | 0.254          | 0.007                | 0.010 |  |

| I      | 0.050      | 0.254          | 0.002                | 0.010 |  |

| J      | 5.791      | 6.200          | 0.228                | 0.244 |  |

| М      | 0.400      | 1.270          | 0.016                | 0.050 |  |

8-Lead SOP Plastic Package

### **Richtek Technology Corporation**

5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

# **Datasheet Revision History**

| Version | Data      | Page No. | ltem                                                                                                                                                                                                                                               | Description                                                                                  |

|---------|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| P00     | 2010/4/6  |          |                                                                                                                                                                                                                                                    | First Edition                                                                                |

| P01     | 2011/7/19 |          | Ordering Information                                                                                                                                                                                                                               | Modify                                                                                       |

| P02     | 2012/4/24 |          | General Description Features Applications Simplified Application Circuit Functional Pin Description Absolute Maximum Ratings Recommended Operating Conditions Electrical Characteristics Typical Operating Characteristics Application Information | Modify & New Format (some item) Add Simplified Application Circuit & Application Information |