## Investigation of High-density Integrated Solution for AC/DC Conversion of a Distributed Power System

Bing Lu

Dissertation submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy In Electrical Engineering

Fred C. Lee, Chairman Daan Van Wyk Fei Wang Douglas K. Lindner Guo-Quan Lu

May 5th, 2006 Blacksburg, Virginia

Keywords: High frequency, High density, Front-end, DPS, AC/DC, DC/DC, PFC, Three-level, Bridgeless PFC, Resonant converter, LLC, IPEM, Embedded power, Power integration

## Investigation of High-density Integrated Solution for AC/DC Conversion of a Distributed Power System

#### Bing Lu

#### **ABSTRACT**

With the development of information technology, power management for telecom and computer applications become a large market for power supply industries. To meet the performance and reliability requirement, distributed power system (DPS) is widely adopted for telecom and computer systems, because of its modularity, maintainability and high reliability.

Due to limited space and increasing power consumption, power supplies for telecom and server systems are required to deliver more power with smaller volume. As the key component of DPS system, front-end AC/DC converter is under the pressure of continuously increasing power density. For conventional industry practices, some limitations prevents front-end converter meeting the power density requirement. In this dissertation, different techniques have been investigated to improve power density of front-end AC/DC converters.

For PFC stage, at low switching frequency, PFC inductor size is large and limits the power density. Although increasing switching frequency can dramatically reduce PFC inductor size, EMI filter size might be larger at higher switching frequency because of the change of noise spectrum. Since the relationship between EMI filter size and PFC switching frequency is unclear for industry, PFC circuits always operate with switching frequency lower than 150 kHz. Based on the EMI filter design method, together with a simple EMI noise prediction model, relationship between EMI filter corner frequency and PFC switching frequency was revealed. The analysis shows that switching frequency

of PFC circuit should be higher than 400 kHz, so that both PFC inductor and EMI filter size can be reduced.

Although theoretical analysis and experimental results verify the benefits of high switching frequency PFC, it is essential to find a suitable topology that allows high switching frequency operation while maintains high efficiency. Three PFC topologies, single switch PFC, three-level PFC with range switch and dual Boost PFC, were evaluated with analysis and experiments. By using advanced semiconductor devices, together with proposed control methods, these topologies could achieve high efficiency at high switching frequency. Thus, the benefits of high frequency PFC can be realized.

In front-end converter, large holdup time capacitor size is another barrier for power density improvement. To meet the holdup time requirement, bulky holdup time capacitor is normally used to provide energy during holdup time. Holdup time capacitor requirement can be reduced by using wider input voltage range DC/DC converte. Because LLC resonant converter can realized with input voltage range without sacrificing its normal operation efficiency, it becomes an attractive solution for DC/DC stage of front-end converters. Moreover, its small switching loss allows it operating at MHz switching frequency and achieves smaller passive component size. However, lack of design methodology makes the topology difficult to be implemented. An optimal design methodology for LLC resonant converter has been developed based on the analysis on the circuit during normal

operation condition and holdup time. The design method is verified by a 1 MHz switching frequency LLC resonant converter with 76W/in<sup>3</sup> power density.

When front-end converter operates at high switching frequency, negative effects of circuit parasitics become more pronounced. By integrating active devices together with their gate drivers, Active Integrated power electronics module (IPEM) can largely reduce circuit parasitics. Therefore, switching loss and voltage stress on switching devices can be reduced. Moreover, IPEM concept can be extended into passive integration and EMI filter integration By using this power integration technology, power density and circuit performance of front-end converter can be improved, which is verified by theoretical analysis and experimental results.

# To Whom It is needed

#### **ACKNOWLEDGMENT**

I would like to thank my advisor, Dr. Fred C. Lee for his guidance and help during my Ph. D. program. His knowledge, research attitude and ways of thinking are most valuable during my years of study and they will keep help me in my future life. I also want to thank his challenge during my past researches, which could always help me find issues in my work and lead to the right direction. Without his challenges, I might not be able to accomplish this

I am grateful to my committee members, Dr. Daan van Wyk, Dr. Fred Wang, Dr. Douglas Lindner and Dr. Guo-Quan. Lu, for their valuable suggestions and numerous help.

It has been a great pleasure to work in the Center for Power Electronics Systems (CPES). I would like to acknowledge the CPES administrative and management staff, Ms. Teresa Shaw, Ms. Linda Gallagher, Ms. Trish Rose, Ms. Ann Craig, Ms. Marianne Hawthome, Ms. Elizabeth Tranter, Ms. Michellel Czamanske, Ms. Linda Long, Mr. Robert Martin, Mr. Steve Chen, Mr. Dan Huff, Mr. Gary Kerr, Mr. Jamie Evans and Mr. Callaway Cass, for their countless help.

I am especially indebted to my teammates in my research group, Dr. Ming Xu, Dr. Peter Barabosa, Dr. Qun Zhao, Dr. Francisco Canales, Dr. Wei Dong, Dr. Bo Yang, Dr. Yong Li, Dr. Yang Qiu, Mr. Liyu Yang, Ms. Manjing Xie, Miss Tingting Sang, Ms. Juanjuan Sun, and Mr. Dianbo Fu, Mr. Chuanyun Wang, Mr.

Yonghan Kang, Mr. Clark Person, Dr. Zhiguo Lu, Dr. Jinjun Liu, Dr. Zhenxian Liang, Dr. Zhou Chen, Dr. Wenduo Liu, Ms. Yan Liang. It was a pleasure to work with such a talented, hard-working and creative group.

I would like to thank my colleagues, Dr. Jingdong Zhang, Dr. Peng Xu, Dr. Sihua Wen, Dr. Jinghong Guo, Dr. Kaiwei Yao, Mr. Mao Ye, Mr. Yu Meng, Dr. Yuancheng Ren, Dr. Jinghai Zhou, Ms. Li Ma, Dr. Xigen Zhou, Dr. Bin Zhang, Dr. Zhiye Zhang, Dr. Guofeng Bai, Dr. Huiyu Zhu, Dr. Jian Ying, Dr. Ning Zhu, Dr. Haifei Deng, Dr. Xudong Huang, Dr. Huijie Yu, Mr. Wei Shen, Ms. Shen Wang, Mr. Luis Arnemod, Mr. Carson Baisden, Mr. Arthus Ball, Mr. Bryan Charboneau, Mr. Yan Dong, Mr. Jerry Francis, Mr. Bin Huang, Miss Yan Jiang, Dr. Ching-Shan Leu, Mr. Jian Li, Dr. Qian Liu, Mr. Ya Liu, Mr. Anish Prasai, Mr. Andew Shmit, Mr. Honggang Sheng, Mr. Time Thacker, Mr. Alex Uan-Zo-Li, Mr. Yuvcheng Ying. Their friendships and help have made my stay at CPES pleasant and enjoyable.

I would like to give my special thanks to my family, my wife and my parents, their love and support make my life more colorful and meaningful.

## **Table of Contents**

| Chapte | er 1. | Introduction                                               | 1     |

|--------|-------|------------------------------------------------------------|-------|

| 1      | .1    | Research Background                                        | 1     |

| 1      | .2    | Issues with Existing Solutions                             | 6     |

| 1.     | .3    | Dissertation structure                                     | 11    |

| Chapte | er 2. | Investigation of High Switching Frequency PFC              | 15    |

| 2      | .1    | Introduction                                               | 15    |

| 2      | .2    | Switching frequency impact on the PFC inductor             | 17    |

| 2      | .3    | Switching frequency impacts on EMI filter design           | 21    |

|        | 2.3.  | 1 EMI filter design procedure                              | 22    |

|        | 2.3.  | 2 EMI noise prediction of PFC circuit                      | 27    |

|        | 2.3.  | Filter size evaluation for different switching frequencies | 39    |

|        | 2.3.  | 4 Experimental verification                                | 47    |

| 2      | .4    | Further benefits brought by high switching frequency       | 49    |

| 2      | .5    | Summary                                                    | 53    |

| Chapte | er 3. | PFC Topologies Evaluation for High Switching Frequen       | ncy55 |

| 3      | .1    | Introduction                                               | 55    |

| 3      | .2    | High frequency opportunity of Conventional PFC             | 58    |

| 3      | .3    | PFC topologies evaluation for high switching frequency     | 67    |

|     | 3.3     | .1    | Three-level PFC                                      | 67  |

|-----|---------|-------|------------------------------------------------------|-----|

|     | 3.3     | .2    | Dual Boost PFC (Bridgeless PFC)                      | 79  |

|     | 3.4     | Sun   | nmary                                                | 99  |

| Cha | pter 4. |       | High Frequency LLC Resonant Converter                | 102 |

|     | 4.1     | Intro | oduction                                             | 102 |

|     | 4.2     | Ope   | eration principles of LLC Resonant Converter         | 109 |

|     | 4.2     | .1    | Switching frequency equal to resonant frequency      | 110 |

|     | 4.2     | .2    | Switching frequency higher than resonant frequency   | 113 |

|     | 4.2     | .3    | Switching frequency lower than resonant frequency    | 115 |

|     | 4.3     | Perf  | formance Analysis of LLC resonant converter          | 117 |

|     | 4.3     | .1    | Loss analysis on the operation at resonant frequency | 117 |

|     | 4.3     | .2    | Performance Analysis During holdup time              | 123 |

|     | 4.4     | Des   | ign of LLC Resonant Converter                        | 127 |

|     | 4.4     | .1    | Choosing Transformer turns-ratio                     | 129 |

|     | 4.4     | .2    | Choosing of magnetizing inductor                     | 129 |

|     | 4.4     | .3    | Choosing inductor ration $L_n$                       | 133 |

|     | 4.5     | Meg   | ga Hz LLC Resonant Converter                         | 139 |

|     | 4.6     | Futi  | ure work for LLC resonant converter                  | 151 |

|     | 4.7     | Sun   | nmary                                                | 153 |

| Chapter 5. | Prospects of Power Integration                        | . 156 |

|------------|-------------------------------------------------------|-------|

| 5.1        | Introduction                                          | . 156 |

| 5.2        | Power Converter Improvement through Power Integration | . 159 |

| 5.2        | .1 Active integration (Active IPEM)                   | . 161 |

| 5.2        | .2 Passive Integration                                | . 166 |

| 5.2        | .3 Integrated DC/DC converter                         | . 169 |

| 5.3        | Prospects of power integration                        | . 173 |

| 5.4        | Summary                                               | . 188 |

| Chapter 6. | Summary and Future Work                               | . 191 |

| 6.1        | Summary                                               | . 191 |

| 6.2        | Future work                                           | . 194 |

| Reference  | 197                                                   |       |

# **List of Figures**

| Figure 1-1 Distributed power system                                           | 2      |

|-------------------------------------------------------------------------------|--------|

| Figure 1-2. DPS for server system.                                            | 5      |

| Figure 1-3. Power density trends for front-end AC/DC converters.              | 6      |

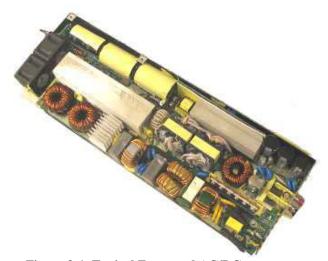

| Figure 1-4. Typical front-end AC/DC converter                                 | 8      |

| Figure 1-5. State of art front-end converter.                                 | 8      |

| Figure 2-1. Typical Front-end AC/DC converter                                 | 15     |

| Figure 2-2. Single switch CCM PFC.                                            | 17     |

| Figure 2-3. PFC duty cycle along half line cycle for different input voltages | 18     |

| Figure 2-4. Current ripple along the line cycle for different input voltages  | 19     |

| Figure 2-5. PFC inductor for different switching frequencies.                 | 20     |

| Figure 2-6. EN55022 Class B EMI standard.                                     |        |

| Figure 2-7. Two-stage EMI filter.                                             | 23     |

| Figure 2-8. Two-stage differential mode filter; (a) Equivalent circuit, (b) I | Filter |

| attenuation.                                                                  | 24     |

| Figure 2-9. Two-stage common mode filter, (a) Equivalent circuit, (b) 1       | Filter |

| attenuation.                                                                  | 25     |

| Figure 2-10. Equivalent corner frequency of two stage filter                  | 26     |

| Figure 2-11. PFC circuit with LISN and parasitic capacitor.                   | 29     |

| Figure 2-12. DM current transferring path.                                    | 30     |

| Figure 2-13. CM current transferring path                                     | 30     |

| Figure 2-14. Equivalent circuit for EMI noise.                                | 31     |

| Figure 2-15. Spectrum of voltage source.                                      |        |

| Figure 2-16. Spectrum envelope of PFC noise source.                           | 33     |

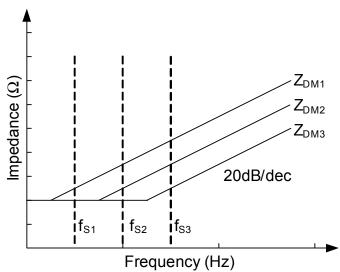

| Figure 2-17. DM noise path impedance for different switching frequency        | 34     |

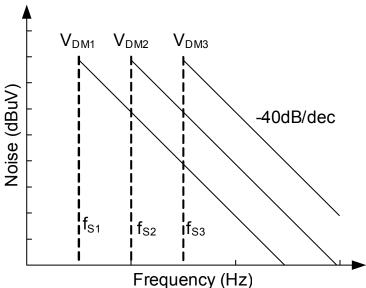

| Figure 2-18. DM noise spectrum envelope for different switching frequencies   | 35     |

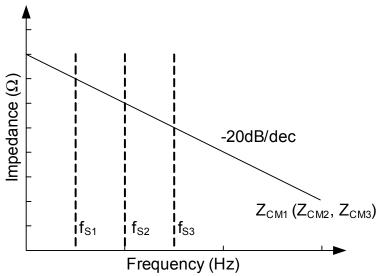

| Figure 2-19. CM noise path impedance for different switching frequency        |        |

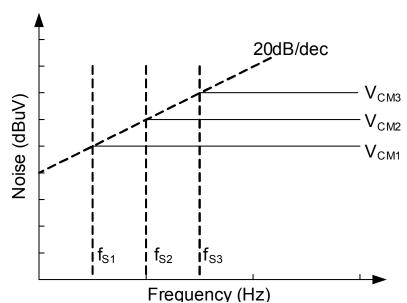

| Figure 2-20. CM noise spectrum envelope for different switching frequencies   | 37     |

| Figure 2-21. Measured common mode noise.                                      | 38     |

| Figure 2-22. Worst frequency vs. switching frequency                          | 40     |

| Figure 2-23. DM filter attenuation requirement.                               | 42     |

| Figure 2-24. Corner frequency of DM filter vs. switching frequency            | 44     |

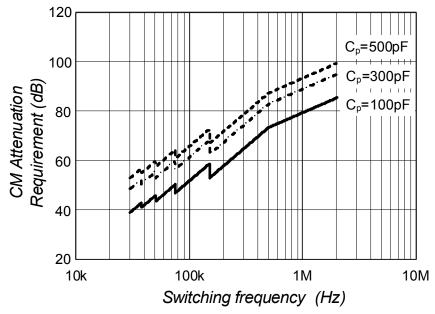

| Figure 2-25. CM attenuation requirement.                                      | 45     |

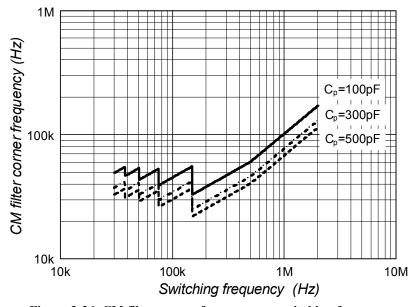

| Figure 2-26. CM filter corner frequency vs. switching frequency               |        |

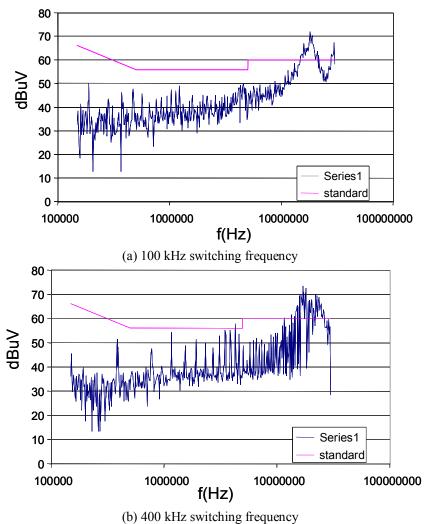

| Figure 2-27. EMI noise after filtering for different switching frequencies    | 48     |

| Figure 2-28. EMI noise after filtering and EMI filter size comparison         | 49     |

| Figure 2-29. Equivalent circuit for DM noise modeling.                        |        |

| Figure 2-30. 100 kHz switching frequency PFC.                                 |        |

| Figure 2-31. Impedances for two PFC inductors for different switch            | _      |

| frequencies.                                                                  | 51     |

| Figure 2-32. EMI noise comparison between two different switching frequence                          |      |

|------------------------------------------------------------------------------------------------------|------|

| Figure 3-1. Single Switch CCM PFC.                                                                   |      |

| Figure 3-2. Efficiency for 1kW single switch PFC with 100 kHz switch                                 |      |

| frequency. Figure 3-3. Loss breakdown for 100 kHz, 1kW PFC with IRFP460A a                           |      |

| RHRP860                                                                                              |      |

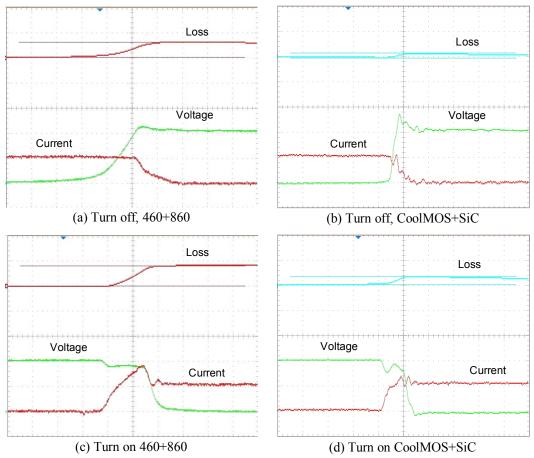

| Figure 3-4. Switching Waveform comparison (20nS/div, 200V/div, 20A/d                                 |      |

| 400uJ/div)                                                                                           |      |

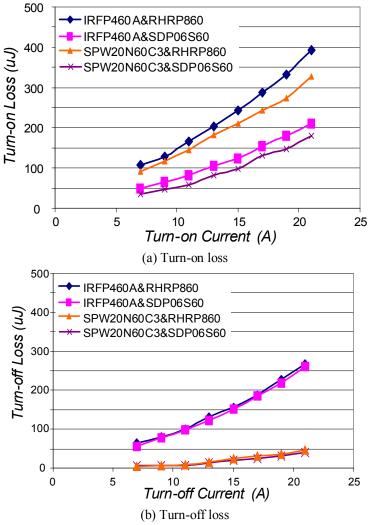

| Figure 3-5. Switching loss comparison for different device combinations                              | 62   |

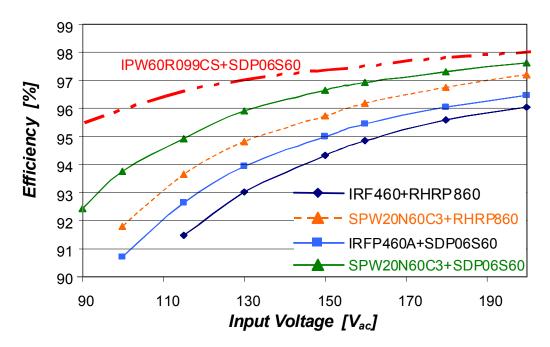

| Figure 3-6. 100 kHz 1kW PFC efficiency using different devices.                                      |      |

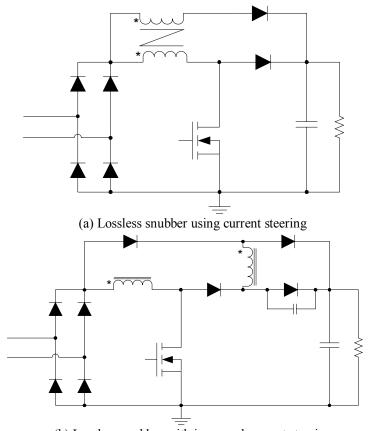

| Figure 3-7. PFC circuit with different lossless snubbers.                                            |      |

| Figure 3-8. Efficiency of high frequency PFC.                                                        | 65   |

| Figure 3-9. Hardware comparison of PFC circuit with different switch frequencies.                    | _    |

| Figure 3-10. Three level PFC with range switch.                                                      |      |

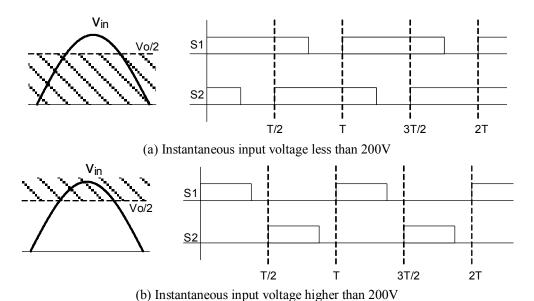

| Figure 3-11. Two-level control method for three-level PFC.                                           | 69   |

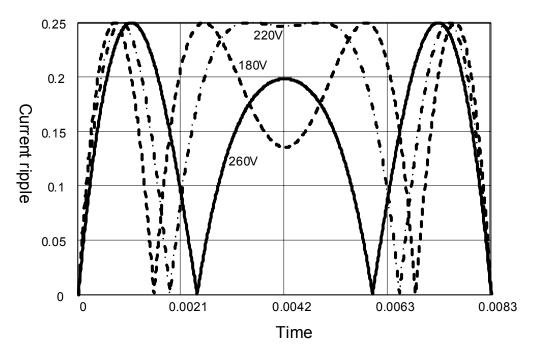

| Figure 3-12. Inductor ripple current for different input line with simple cont                       |      |

| method.                                                                                              |      |

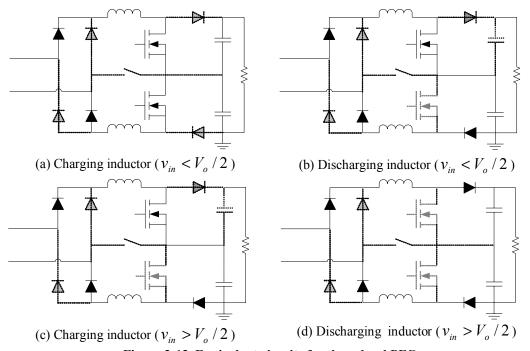

| Figure 3-13. Equivalent circuits for three-level PFC.                                                |      |

| Figure 3-14. Gate signals for two MOSFETs.                                                           |      |

| Figure 3-15. Inductor ripple current for three-level PFC with other cont method                      | trol |

| Figure 3-16. Equivalent circuit for three-level PFC with range switch at low in                      |      |

| line.                                                                                                | _    |

| Figure 3-17. Comparison between conventional PFC and three=level PFC                                 |      |

| 110V input                                                                                           |      |

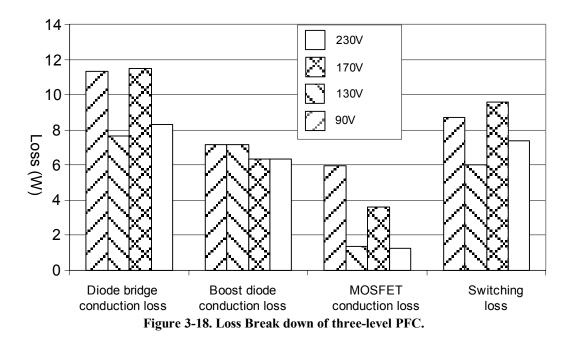

| Figure 3-18. Loss Break down of three-level PFC                                                      |      |

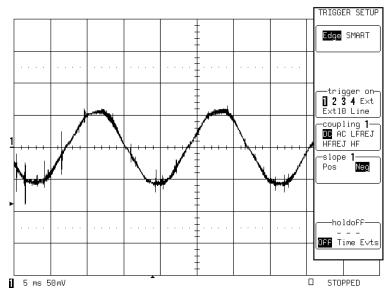

| Figure 3-19. Input current for three-level PFC at 110V input (10A/div, 5mS/div                       |      |

|                                                                                                      |      |

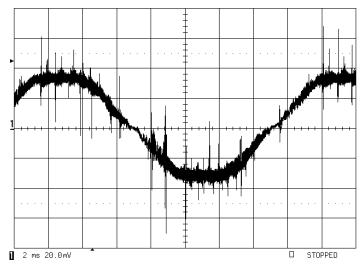

| Figure 3-20. Input current for three-level PFC at high input line (4A/d                              |      |

| 2mS/div).                                                                                            |      |

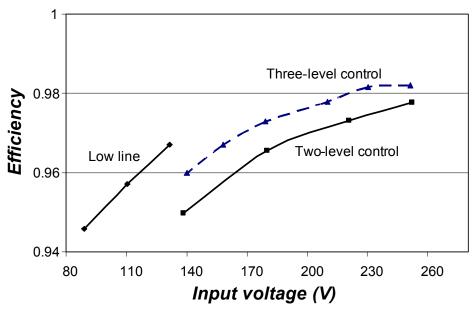

| Figure 3-21. Efficiency for three-level PFC with range switch.  Figure 3-22. Bridgeless PFC circuit. |      |

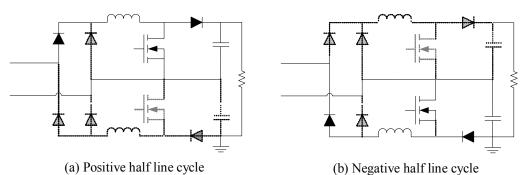

| Figure 3-23. Equivalent circuit of bridgeless PFC.                                                   |      |

| Figure 3-24. Forward voltage drop comparison.                                                        |      |

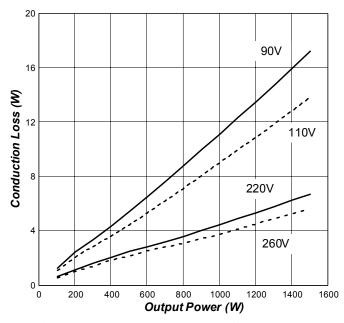

| Figure 3-25. Diode conduction loss comparison.                                                       |      |

| Figure 3-26. Power loss improvement at different input voltages.                                     |      |

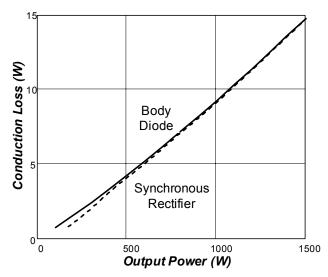

| Figure 3-27. MOSFET loss comparison between the body diode and synchronic                            |      |

| rectifier at 25°C                                                                                    |      |

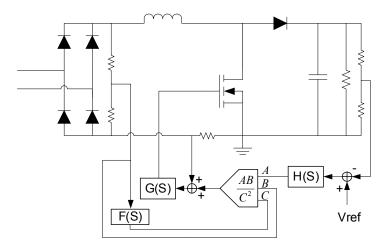

| Figure 3-28. Average current control for PFC circuit.                                                | 85   |

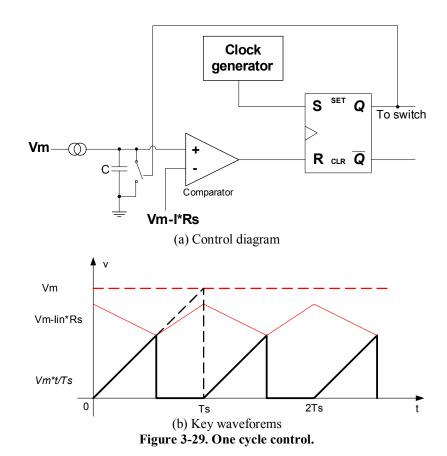

| Figure 3-29. One cycle control.                                                                      |      |

| Figure 3-30. Input voltage sensing for conventional PFC.                                             |      |

| Figure 3-31. Voltage sensing for bridgeless PFC.                                                     |      |

| Figure 3-32. Current sensing for conventional PFC.                         | 20   |

|----------------------------------------------------------------------------|------|

| Figure 3-33. Current sensing for bridgeless PFC.                           |      |

| Figure 3-34. Parasitic capacitor contributes to common mode noise          |      |

| conventional PFC.                                                          | . 92 |

| Figure 3-35. Parasitic capacitances contribute to common mode noise        |      |

| bridgeless PFC.                                                            |      |

| Figure 3-36. Voltage on the parasitic capacitor of bridgeless PFC.         |      |

| Figure 3-37. EMI noise for bridgeless PFC without EMI reduction circuit    |      |

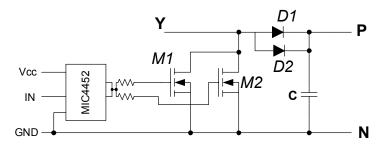

| Figure 3-38. An improved EMI performance bridgeless PFC circuit            |      |

|                                                                            |      |

| Figure 3-39. Input voltage and current waveforms of the bridgeless PFC     |      |

| Figure 3-40. Efficiency comparison between conventional PFC and bridge     |      |

| PFC                                                                        |      |

| Figure 3-41. PF comparison at different input line.                        |      |

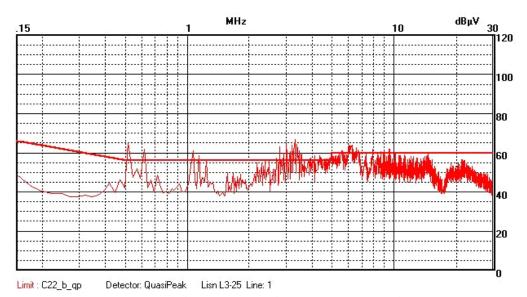

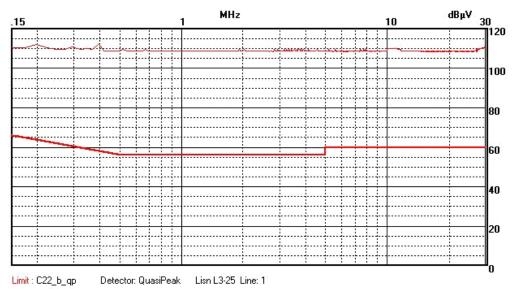

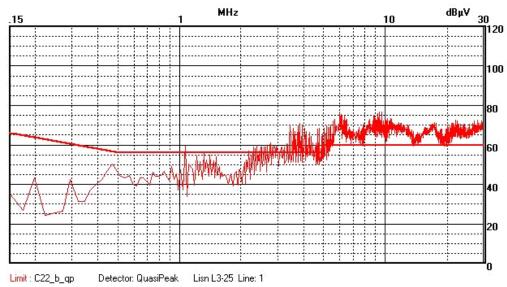

| Figure 3-42. EMI noise of the conventional PFC.                            |      |

| Figure 3-43. EMI noise for bridgeless PFC without EMI reduction circuit    |      |

| Figure 3-44. EMI noise of bridgeless PFC with noise reduction circuit      |      |

| Figure 4-1. 1200W front-end AC/DC converter.                               |      |

| Figure 4-2. Holdup time requirement for front-end AC/DC converters         | 103  |

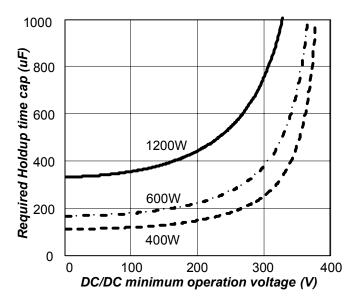

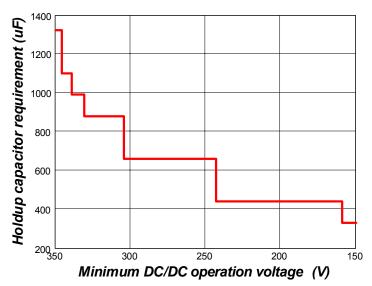

| Figure 4-3. Holdup time capacitor vs. minimum DC/DC stage input voltage    | 104  |

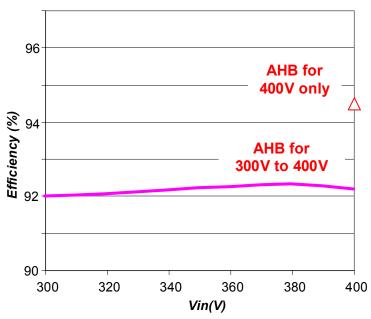

| Figure 4-4. Asymmetrical half bridge efficiency.                           | 105  |

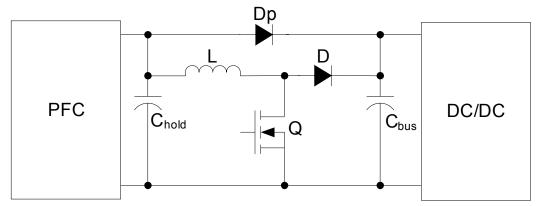

| Figure 4-5. Holdup extension by range winding concept                      | 106  |

| Figure 4-6. Holdup extension circuit.                                      | 107  |

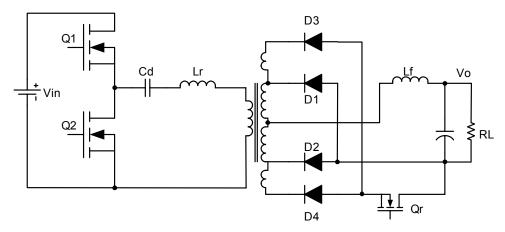

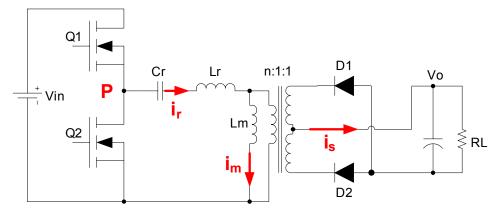

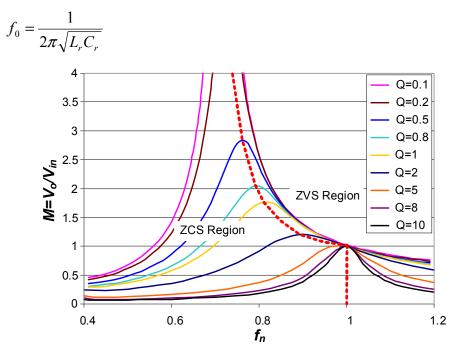

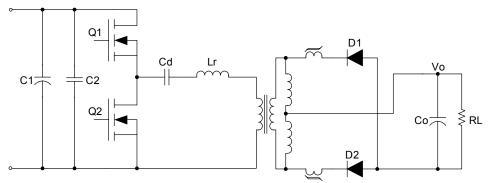

| Figure 4-7. LLC Resonant Converter.                                        | 108  |

| Figure 4-8. Gain characteristic for LLC resonant converter.                | 110  |

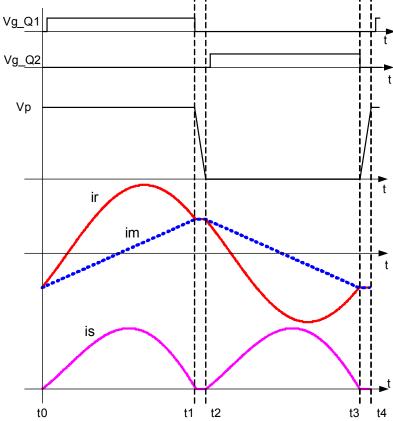

| Figure 4-9. LLC resonant converter operates at resonant frequency          | 111  |

| Figure 4-10. Equivalent circuit for LLC circuit at resonant frequency      |      |

| Equivalent circuit from t0 to t1, (b) Equivalent circuit from t1 to t2,    |      |

| Equivalent circuit from t2 to t3                                           |      |

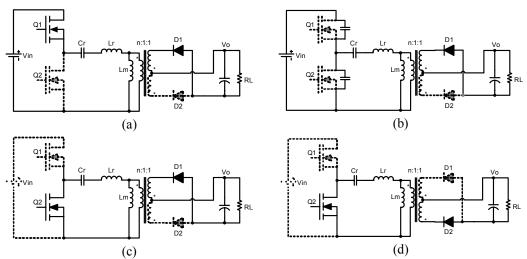

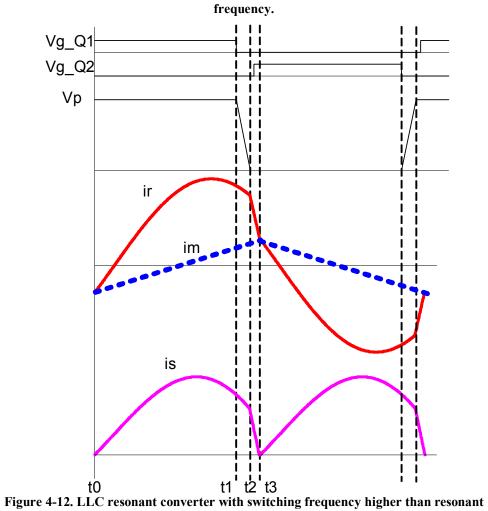

| Figure 4-11. Equivalent circuits for LLC switching frequency higher t      |      |

| resonant frequency.                                                        |      |

| Figure 4-12. LLC resonant converter with switching frequency higher t      |      |

| resonant frequency.                                                        |      |

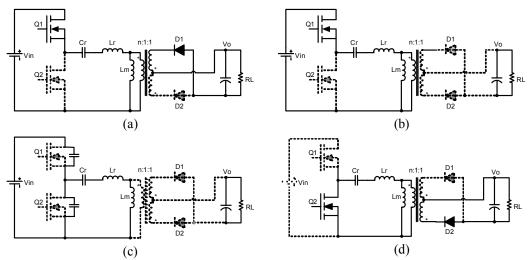

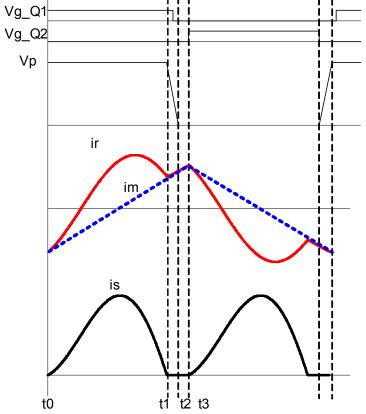

| Figure 4-13. Equivalent circuit with switching frequency lower than resor  |      |

| frequency                                                                  |      |

| Figure 4-14. LLC resonant converter with switching frequency lower t       |      |

| resonant frequency.                                                        |      |

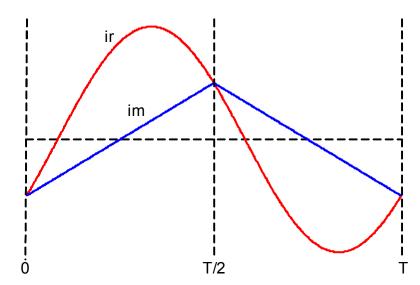

| Figure 4-15. Resonant tank current and magnetizing current at resor        |      |

|                                                                            |      |

| frequency.                                                                 | 110  |

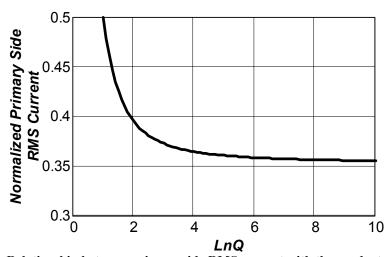

| Figure 4-16. Relationship between primary side RMS current with the produc |      |

| Ln and Q.                                                                  |      |

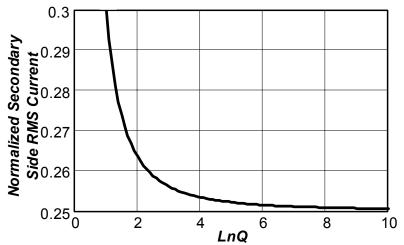

| Figure 4-17. Normalized secondary side RMS current.                        |      |

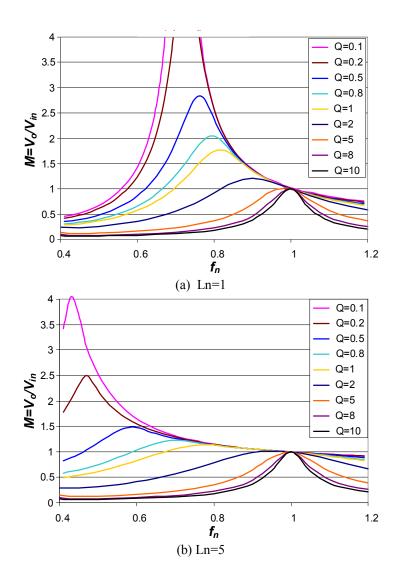

| Figure 4-18. Gain characteristics for different Ln and Q.                  |      |

| Figure 4-19. Achievable peak gain for different Ln and Q values            |      |

| Figure 4-20. Design procedure for LLC resonant converter                   | 128  |

| Figure 4-21. Equivalent circuit during dead-time.                          | 130     |

|----------------------------------------------------------------------------|---------|

| Figure 4-22. Contour curves for LLC converter peak gains                   |         |

| Figure 4-23. Design example of LLC converter.                              |         |

| Figure 4-24. Impacts of Ln.                                                | 138     |

| Figure 4-25. 200 kHz LLC resonant converter prototype.                     | 140     |

| Figure 4-26. 400 kHz LLC resonant converter prototype.                     | 140     |

| Figure 4-27. Relationship between holdup time capacitor and minimum D      | C/DC    |

| input voltage by considering limited capacitor choices.                    | 142     |

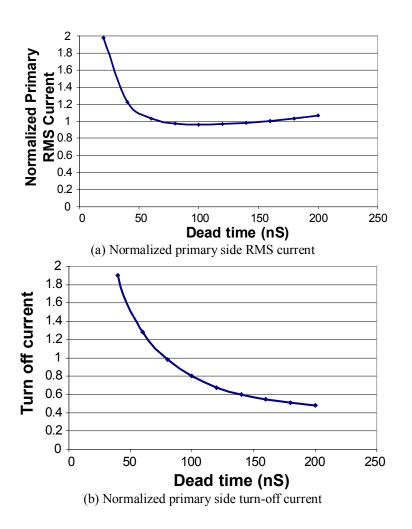

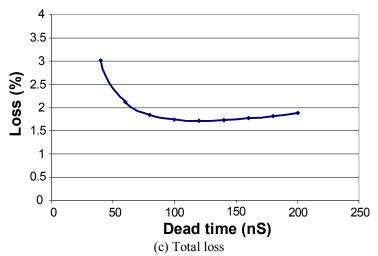

| Figure 4-28. Relationship between dead-time and converter losses, (a) cond | uction  |

| loss, (b) switching loss, (c) total loss.                                  | 145     |

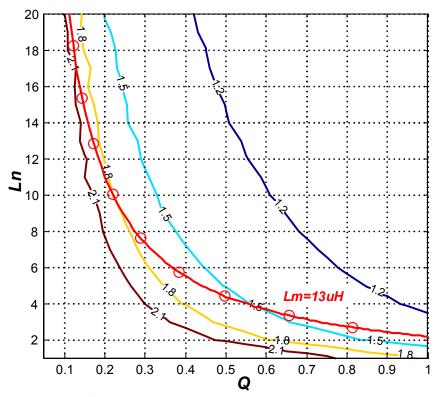

| Figure 4-29. Design curves for 1MHz LLC resonant converter.                | 146     |

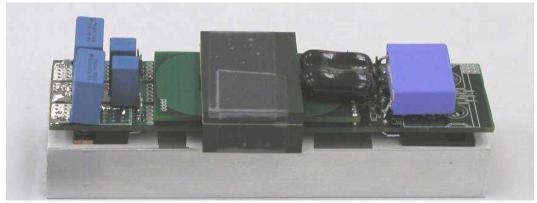

| Figure 4-30. Prototype of 1MHz LLC resonant converter.                     |         |

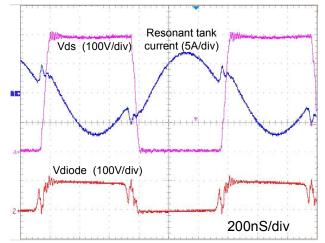

| Figure 4-31. Experimental waveform at resonant frequency                   | 148     |

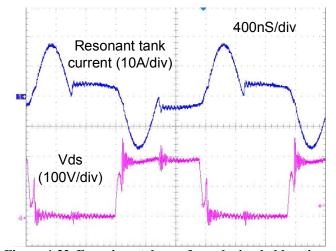

| Figure 4-32. Experimental waveform during holdup time.                     | 148     |

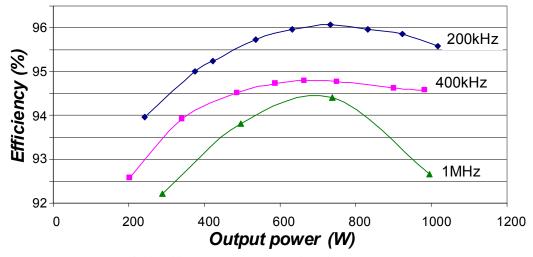

| Figure 4-33. Efficiency comparison of LLC resonant converter               | 149     |

| Figure 4-34. Loss breakdown of designed converter.                         | 150     |

| Figure 4-35. Equivalent circuit for ideal LLC resonant tank.               | 152     |

| Figure 4-36. LLC Passive IPEM with leakage inductance                      |         |

| Figure 5-1. 200 kHz asymmetrical half bridge with discrete devices         | 160     |

| Figure 5-2. Circuit diagram of AHB converter.                              |         |

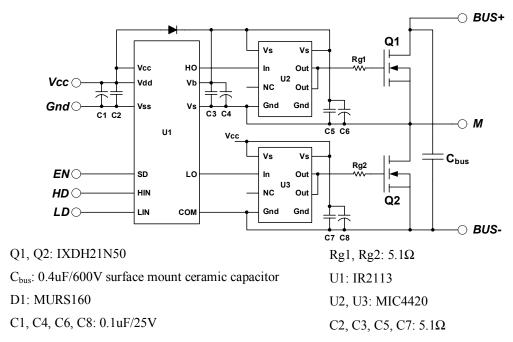

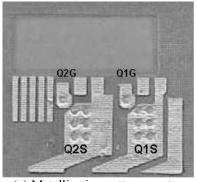

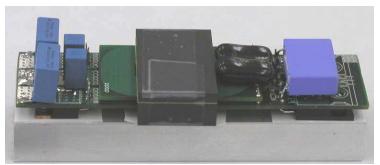

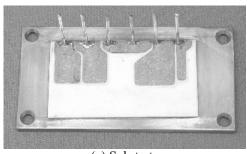

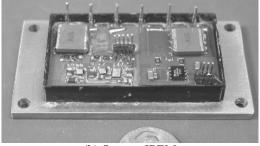

| Figure 5-3. DC/DC Active IPEM.                                             | 162     |

| Figure 5-4. Fabrication of DC/DC integrated multi-chip stage               | 163     |

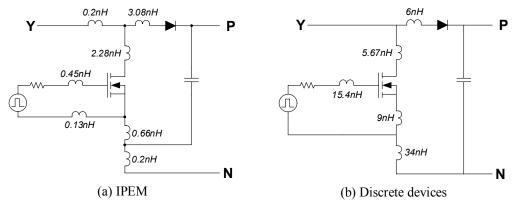

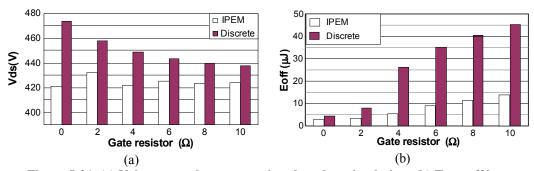

| Figure 5-5. Switching stage parasitics.                                    | 164     |

| Figure 5-6. Switching performance comparison for different gate resistors  | 165     |

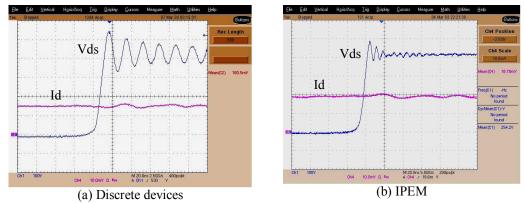

| Figure 5-7. Discrete device test waveform.                                 | 166     |

| Figure 5-8. IPEM measurement results.                                      | 166     |

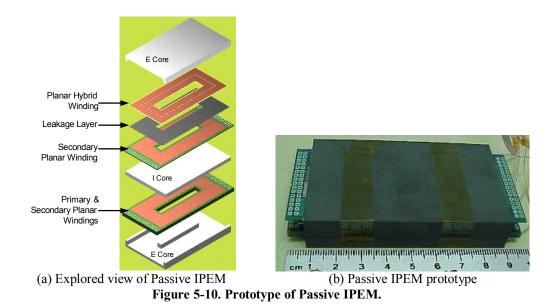

| Figure 5-9. Passive IPEM for Asymmetrical Half Bridge.                     | 166     |

| Figure 5-10. Prototype of Passive IPEM.                                    |         |

| Figure 5-11. 200 kHz asymmetrical half bridge with IPEMs.                  | 169     |

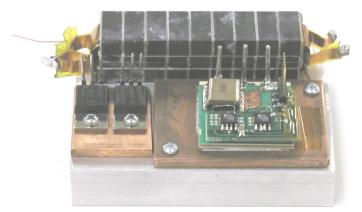

| Figure 5-12. 400 kHz LLC resonant converter with discrete devices          | 170     |

| Figure 5-13. IPEM-based 400 kHz LLC resonant converter.                    | 171     |

| Figure 5-14. 1MHz LLC resonant converter with discrete devices.            | 172     |

| Figure 5-15. 1 MHz LLC resonant converter with IPEMs.                      | 173     |

| Figure 5-16. Front-end AC/DC converter based on discrete devices           | 174     |

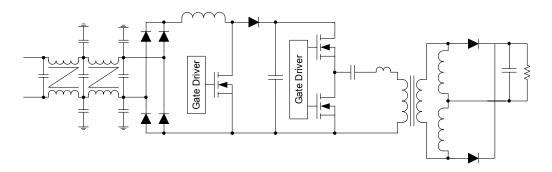

| Figure 5-17. Schematic of front-end converter benchmark.                   | 174     |

| Figure 5-18. System IPEM PFC part.                                         |         |

| Figure 5-19. IPEM assembly from the integrated chip stages.                | 176     |

| Figure 5-20. Parasitic comparison between PFC IPEM and discrete devices.   | 177     |

| Figure 5-21. (a) Voltage overshoot comparison based on simulation; (b) Tu  | ırn off |

| loss comparison based on simulation.                                       |         |

| Figure 5-22. MOSFET drain to source voltage during turn off 100V/div, 5    | A/div,  |

| 20nS/div.                                                                  |         |

| Figure 5-23. EMI filter                                                    |         |

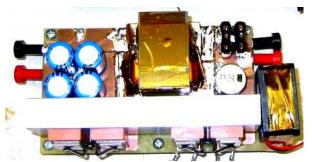

| Figure 5-24. Discrete version of front-end AC/DC converter.                | 180     |

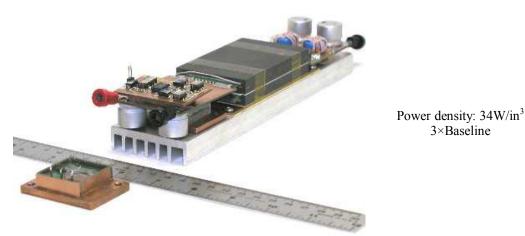

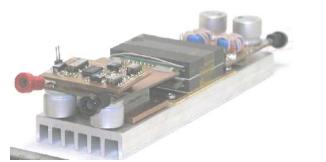

| Figure 5-25. IPEM-based front-end AC/DC converter.                   | 180   |

|----------------------------------------------------------------------|-------|

| Figure 5-26. Assembly of IPEM-based front-end AC/DC converter        | 181   |

| Figure 5-27. PFC stage efficiency comparison.                        | 183   |

| Figure 5-28. Efficiency comparison between two converters            | 183   |

| Figure 5-29. EMI performance comparison between two converters       | 185   |

| Figure 5-30 Thermal Measurement results                              | 186   |

| Figure 5-31. IPEM-based front-end converter with 400 kHz PFC and 400 | ) kHz |

| LLC.                                                                 | 187   |

| Figure 5-32. Summary of IPEM improvement on DC/DC converter          | 189   |

| Figure 6-1. Simplified DPS system.                                   | 194   |

| Figure 6-2. DPS system with unregulated intermediated bus.           | 195   |

| Figure 6-3. Improved DPS system                                      | 196   |

## **List of Tables**

| Table 2-1. PFC inductor comparison for different switching frequencies      | 21  |

|-----------------------------------------------------------------------------|-----|

| Table 2-2. Loss comparison between two PFC inductors.                       |     |

| Table 2-3. EMI model prediction vs. experimental results                    |     |

| Table 3-1. Different control method for three-level PFC at high input line. | 71  |

| Table 3-2. Three-level PFC at low input line with range switch on           |     |

| Table 3-3. Differences between conventional PFC and bridgeless PFC          |     |

| Table 4-1. Normalization for LLC resonant converter.                        | 136 |

| Table 4-2. Design Parameter for LLC Resonant converter.                     | 147 |

| Table 5-1. Parameters comparison between discrete device and Passive IPF    |     |

### Chapter 1. Introduction

#### 1.1 Research Background

With the development of information technology, telecom and computer systems become a large market for power supply industry. Recent statistic data show that the demands for these systems are continuously increasing [A-1]. Moreover, because of the improving of integrated circuit technology, which follows Moor's Law, computers and telecom equipments keep increasing their density and functionality. The increasingly functionality requires more power consumption and higher density requires less size on the power supplies. Therefore, the power supplies for the telecom and computer applications are required to provide more power with less size and cost [A-2][A-3].

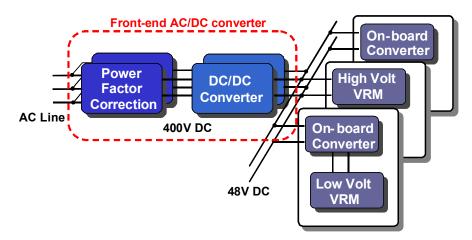

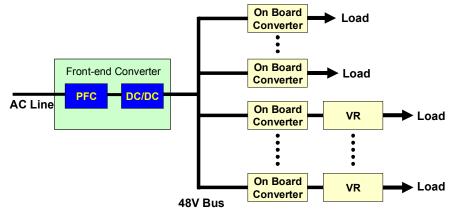

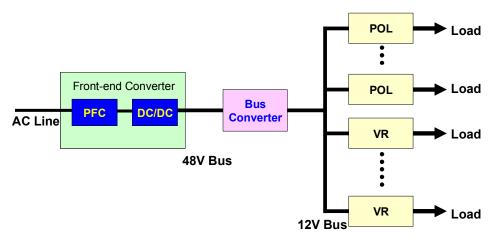

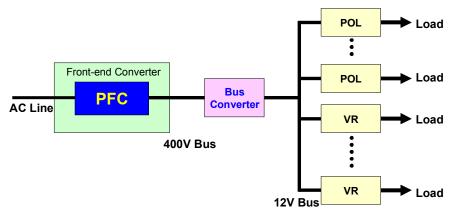

To meet these requirements, distributed power system (DPS) is widely adopted. Instead of using a single bulky power supply to provide the final voltages required by the load, distributed power system distributed the power processing functions among many power processing unites [A-4]-[A-7]. One typical DPS structure is the intermediate bus structure [A-8][A-9], as shown in Figure 1-1. In this system, the voltages that are needed for loads are generated through two stage approach. In first stages, many front-end converters are parallel together to generate the intermediated bus voltage, which is normally 48V, or 12V. After that, the following load converters then transfer the intermediate bus voltage into the voltages that load need. Because of this modular approach, DPS

system has many advantages comparing with centralized power system, and it is widely adopted for telecom and computer system, such as easier thermal management, higher reliability, modularity and easy maintainability [A-6][A-7].

Figure 1-1 Distributed power system

#### A) Easier thermal management

Because several front-end converters are parallel together to provide the total power, each converter only handles part of the total power. Thus, power loss is distributed among different converter, and the thermal design could be much easier. Moreover, because of less loss generated in each module, each module could have its own thermal management mechanism. The system thermal design is much simplified comparing with centralized power system.

#### *B)* Higher reliability

For computer and telecom applications, it is required to have high reliability so that the service providers can continuous pride service to customers. In DPS systems, because of modular approach, each module only handles part of the total power. Thus, electrical and thermal stresses on the devices are much reduced, which can result in higher reliability.

Besides less stress on the devices, DPS system can also improve its reliability by using N+1 redundancy. If N is defined as the minimum number of modules that is required to provide the total load power, by adding one additional module, higher reliability can be achieved. In this way, system can still maintain availability even with one module fail. Moreover, because the power handling capability of N+1 system is higher than the system power consumption requirement, each module handles even less power, which can further improve the reliability of the system.

#### *C) Modularity*

In DPS systems, identical front-end converter modules are parallel together.

This modular approach makes the system extendable, easy reconfiguration and less cost.

For instance, one the system power consumption requirement increase, users can simply parallel more modules to meet the requirement. However in the centralized power system, new power system has to be purchased to meet the power consumption requirement. In addition, because each module is identical, the design and manufacturing can be much easier and faster. Moreover, different

standard approvals, such as safety and harmonics standards, can be obtained much faster.

#### D) Maintainability

Hot-swap becomes popular feather for DPS systems, which allows users replace the deficit power module without interrupting the whole system operation (on-line replacement). Therefore, once the module is failure, power supply manufacture could provide system maintains without shutting down the whole system, which is very desirable for systems that require high availability, such as telecom and data centers.

Furthermore, by using system level controller, the interleaving operation between different modules becomes available. Through interleaving operation of different modules, input and output current ripple and harmonics could be canceled because of phase difference among different modules [A-10][A-11]. Thus, the EMI filter size could be reduced and system can achieve higher power density.

Because of these benefits comparing with the centralized power system, DPS systems are widely adopted by telecom and computer applications. One typical DPS system for server is shown in Figure 1-2. The front-end modules are on the bottom of the rack. It can be seen that several modules are putting side by side to provide the energy. The following stage load converters are on the circuit boards

on the equipment modules locating on the upper side of the rack. Therefore, these load converters are also called on-board modules.

Figure 1-2. DPS for server system.

Because size of the rack is fixed, it is desired to have more space for the equipments such as the telecom boards or computer servers. Thus, the power supply size has to be minimized. On the other hand, increasing of equipments requires more power consumption. The power supplies are in turn required to output more power within less volume, which means higher power density.

Furthermore, because the width of rack is fixed, such as 17U or 19U, and the power modules are vertically slide inside the rack, as shown in the bottom of Figure 1-2. By reducing the profile of power modules, more modules could fit into the rack and provide more power. Therefore, 1U (1.75 inches) becomes a standard profile for present power modules.

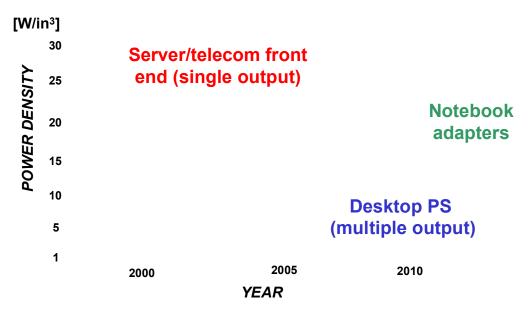

For DPS systems, front-end AC/DC converters are under the pressure of continuous increasing power density requirement. As shown in Figure 1-3, the power density of front-end converter for server and telecom is continuously increasing [A-12]. At year 2000, the power density is only around 7~8W/in<sup>3</sup>. However, the power density reaches 20W/in<sup>3</sup> at year 2005. And the power density of front-end converter is required to keep increasing. Therefore, the dissertation is mainly focus on the investigation of different techniques to improve the power density of front-end AC/DC converter, which includes higher switching frequency, better topology and the integration solutions.

Figure 1-3. Power density trends for front-end AC/DC converters.

#### 1.2 Issues with Existing Solutions

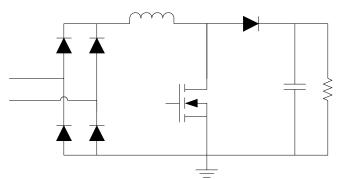

According to the requirements of input current harmonics and output voltage regulation, front-end converter is normally implemented by two-stage approach,

which is power factor correction (PFC) stage followed by the DC/DC stage. PFC stage rectifies the input AC voltage and transfers it into a regulated intermediate DC bus. At the same time, power factor correction function is achieved [A-13][A-14]. The following DC/DC stage then converters the DC bus voltage into a regulated output DC voltage for distribution bus, which is required to meet the regulation and transient requirement.

Due to two-stage power processing, system efficiency depends on the efficiencies on both stages. For instance, if both stages can achieve 90% efficiency, the whole system efficiency is only 81%, which is much lower than that of each stage. Therefore, it is essential to improve the efficiency for both the PFC stage and DC/DC stage.

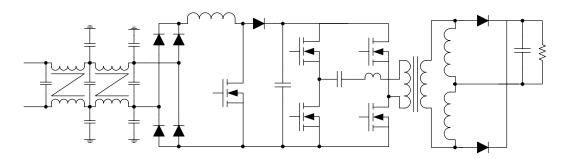

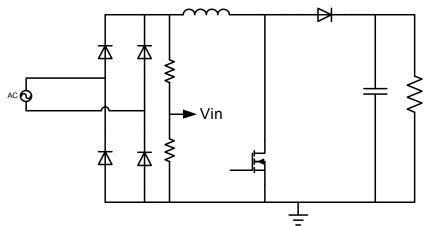

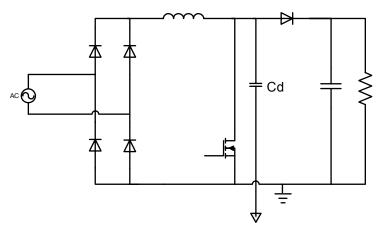

A typical front-end AC/DC converter is shown in Figure 1-4. Its PFC stage uses single switch continuous conduction mode (CCM) PFC with average current mode control, and DC/DC stage uses phase shift full bridge (PSFB) with current doubler. Because of simple structure and smaller EMI filter size, single switch CCM PFC is wide adopted for power factor correction applications. Meanwhile, PSFB is able to achieve high efficiency with soft switching capability. Thus, it is popular for kilo-watt range power supply designs. Because these circuit topologies have been existed for many years and they have been well understood and adopted by power supply industries.

Figure 1-4. Typical front-end AC/DC converter.

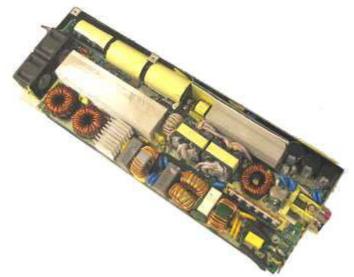

However, due to several limitations, it is difficult to further increasing the power density of the existing converters. A state of art front-end AC/DC converter is shown in Figure 1-5, although it can reach 25W/in<sup>3</sup> power density, several issues can still be observed [A-12].

Figure 1-5. State of art front-end converter.

PFC inductor and EMI filters takes about one third of the whole converter volume. PFC inductor is used to achieve power factor correction and shape the input current to be sinusoidal. To ensure smaller ripple current, PFC inductor is designed based on the switching frequency. It is desired to have higher switching

frequency to achieve smaller PFC inductor size. However, due to the large switching loss caused by PFC stage, it is difficult to increase the switching frequency. Meanwhile, the EMI filter is used to attenuate the EMI noise generated by the system. Because of stringent EMI standard requirement, large EMI filter is normally used in front-end converters. Since the relationship between EMI filter size and switching frequency is not clear for the industry, most PFC circuits in the real implementation are switching below 150 kHz [A-15].

As mentioned before, due to two-stage approach, system efficiency is low. Thus, large heat-sinks are required to maintain the thermal handling capability. To achieve higher power density, heat-sink size can be reduced by either improving the system efficiency or improve the system thermal design.

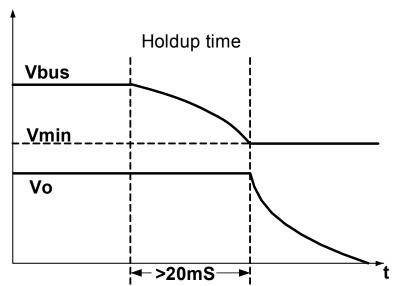

Another large component in front-end converter is the bulky holdup time capacitor. According to the specifications of server systems, front-end AC/DC converters are required to maintain regulated output voltage for more than 20mS when the input AC line is lost. During holdup time, all the energy transferred to the load comes from holdup time capacitor. Therefore, large holdup time capacitors are required to provide the energy during holdup time. Holdup time capacitor requirement is determined by the system power level and the input voltage range of DC/DC converter. Apparently, higher the system power level, more energy is required to transfer to the load. Thus, larger holdup time capacitor is required. On the other hand, wider the DC/DC stage input voltage range, more

energy stored in the holdup time capacitor could be used during holdup time. Thus, less holdup time capacitor can be used. However, in the conventional frontend AC/DC converters, DC/DC stage employs PWM converter, and it is difficult to achieve wide input range together with high efficiency. Therefore, to maintain high system efficiency, large holdup time capacitor has to be used [A-16].

Furthermore, it can be observed that the passive components in the DC/DC stage, such as the transformers and inductors, have large size. Similar to the PFC stage, large switching loss prevents DC/DC stage operating at high switching frequency, which results in large passive components size [A-17].

Moreover, components used in front-end converters are mainly customized designed, and lack of integration. Therefore, costs of components are high, especially for the inductors and transformer. Moreover, large amount of components and lack of integration make front-end converter difficult to be manufactured, which results in higher cost and long manufacturing cycle. [A-18]

To address these issues, the objective of dissertation is to investigation different solutions for front-end converters to achieve higher efficiency, higher power density through high switching frequency topologies and integration technologies.

#### 1.3 Dissertation structure

From the introductions, it can be observed that several fundamental limitations prevent further increasing power density of front-end AC/DC converter. To meet the increasing power density requirement, in this dissertation, different techniques has been investigated to improve the power density of front-end converter, which include high switching frequency, different circuit topologies and integrated solution for front-end converters.

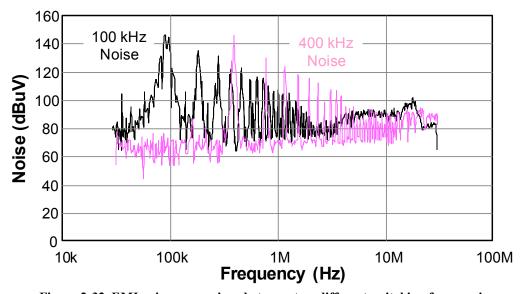

In Chapter 2, switching frequency impacts on PFC circuit has been discussed. For PFC stage, it is desirable to have higher switching frequency to shrink Boost inductor size, since the Boost inductor value is inverse proportional to the switching frequency for given ripple current. However, due to EMI noise standard requirement, EMI filter might increase dramatically even with higher switching frequency. Therefore, it is essential to find out the switching frequency design guideline to achieve higher power density. From the theoretical analysis and experimental verification, it demonstrated that by pushing the switching frequency higher than 400 kHz, both the Boost inductor and EMI filter size keep decreasing and higher power density can be achieved. Furthermore, through the analysis, several switching frequencies should be avoided due to the larger EMI filter size [A-19].

Because high switching frequency of PFC circuit can results in smaller EMI filter size and Boost inductor size, its switching frequency is desired to be higher

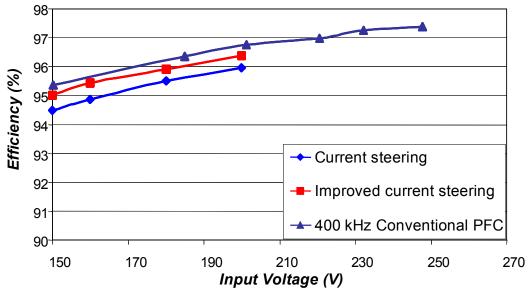

than 400 kHz. With higher switching frequency, switching loss is the major concern. To allow PFC circuit operating with switching frequency higher than 400 kHz, in Chapter 3, different solutions have been discussed. Firstly, the CoolMOS<sup>TM</sup> and SiC Schottky diode are introduced. These new devices can achieve higher switching speed and removes the reverse recovery current, which provides the high switching frequency operation capability. After that different circuit topologies have been discussed [A-20]

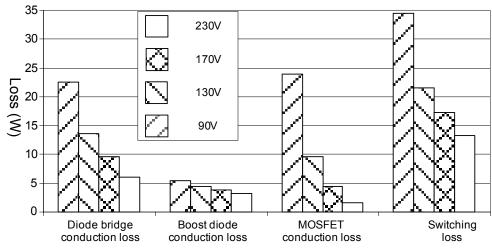

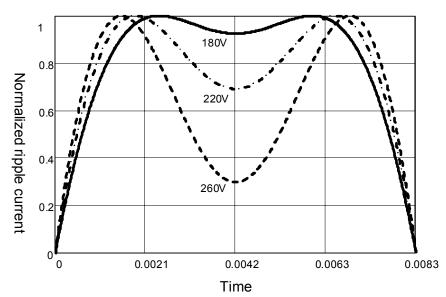

Three-level PFC with range switch could dramatically increase circuit efficiency at low input line by reducing the conduction loss and switching loss. Besides, different control method can also be implemented to further improve the converter efficiency at high input line.

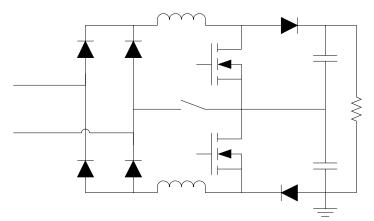

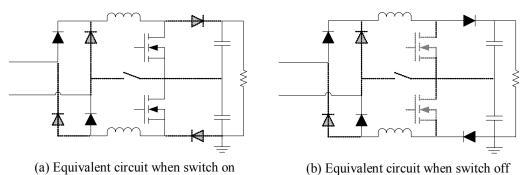

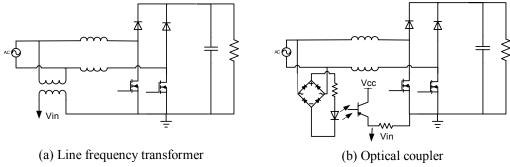

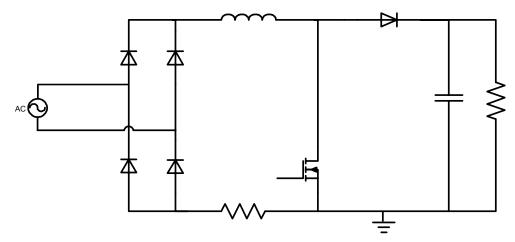

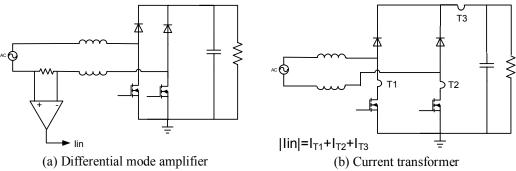

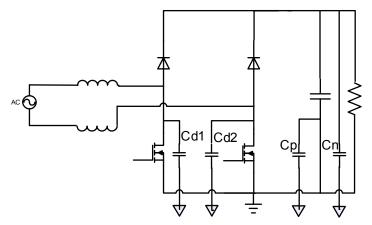

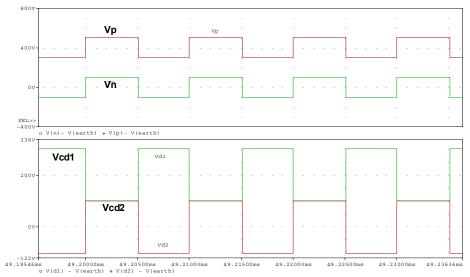

For Dual Boost PFC, by removing the input diode bridge, circuit conduction loss is reduced and higher efficiency can be achieved. However, without the input diode bridge, dual Boost PFC suffers from large common mode (CM) EMI noise. A new EMI noise reduction circuit has been proposed to control the CM noise of Dual Boost PFC [A-21].

Because of higher efficiency of these alternative PFC circuit topologies, PFC circuit switching frequency can be further pushed up to achieve even smaller EMI filter and Boost inductor size.

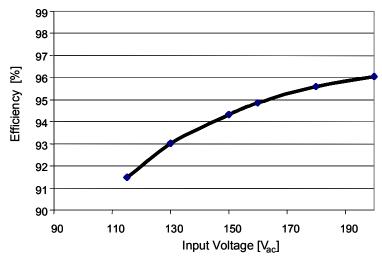

Besides PFC stage Boost inductor and EMI filter, front-end converter also has large holdup time capacitors, which prevents further improving power density. Holdup time capacitor requirement is only determined by the converter power level and DC/DC stage operation range. For conventional PWM DC/DC converters, it is difficult to achieve high efficiency and wide input voltage range together. Therefore, different holdup time extension circuits have been proposed to reduce DC/DC stage operation range requirement. However, these auxiliary circuits are complex and needs extra control circuit. Instead of using extra holdup time extension circuit, LLC resonant converter is able to achieve high efficiency together with wide input voltage range, which gives a promising solution for DC/DC stage of front-end converters. However, lack of design methodology makes the circuit difficult to be adopted by industry. In Chapter 4, an optimal deign methodology has been proposed. Through the analysis of circuit operation at normal condition and during holdup time, it shows that a successful LLC resonant converter design relies on choosing suitable magnetizing inductor and inductor ratio [A-22].

Furthermore, LLC resonant converter has very small switching loss, due to its soft switching capability and soft turn-off of secondary diode. Therefore, it is able to operate at very high switching frequency to achieve high power density while maintain high efficiency. In Chapter 4, an LLC resonant converter with 1MHz switching frequency has been demonstrated and achieves 76W/in<sup>3</sup> power density with 92.5% efficiency at full load.

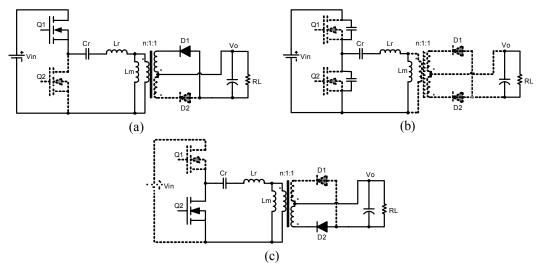

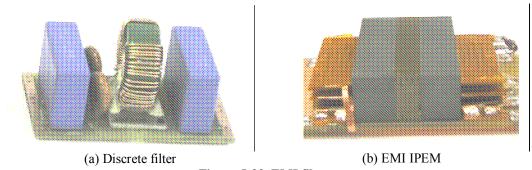

In Chapter 5, the integration solution for front-end AC/DC converter has been discussed. Because the power supplies are mainly customized design and lack of integration, the cost of manufacturing is high. By introducing Integrated Power Electronics Module (IPEM) concept, front-end converters can be simplified as putting several modules together, which can dramatically reduce the manufacturing cost and make automatically manufacturing capable.

Besides the cost, when front-end converter operates at very high switching frequency, circuit parasitic effects become more pronounced and hurt the circuit performance, especially the switching loss and voltage stress on the devices. By using integration technology, circuit parasitics can be dramatically reduced. Through the theoretical analysis and experimental results, the reduction of circuit parasitics could result in less switching loss and voltage stress.

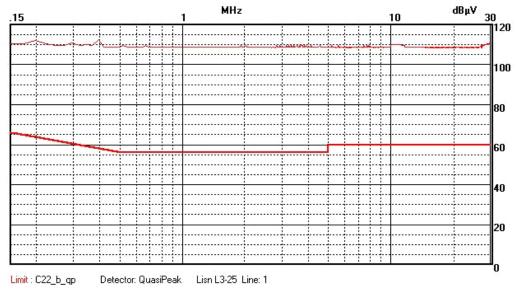

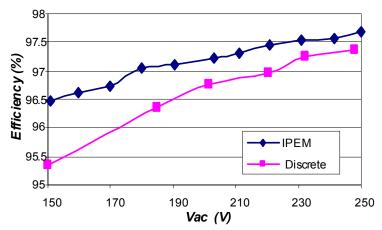

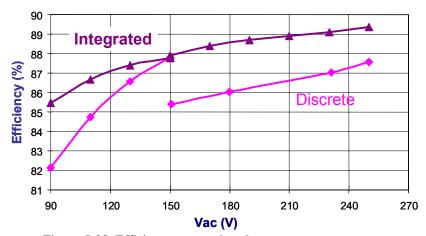

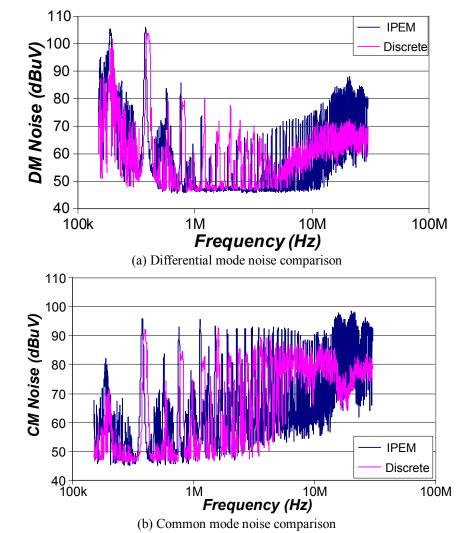

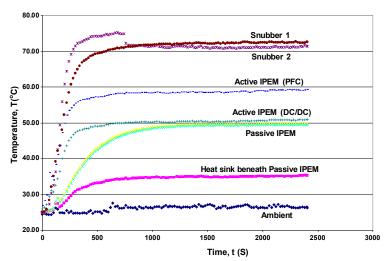

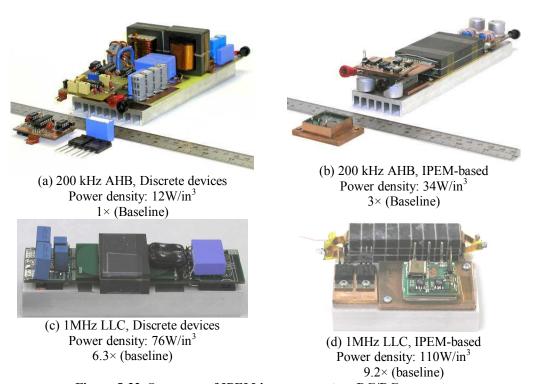

To demonstrate the benefits of IPEMs, DC/DC converters using asymmetrical half bridge (AHB) and LLC resonant topologies are implemented with Active and Passive IPEM. Power density improvement is demonstrated. Furthermore, IPEM concept is extended to whole front-end converter system. Two identical front-end converters with discrete devices and IPEMs have be built and evaluated in detail. The experimental results show that the IPEM version is able to achieve 1.5 time power density improvement and 2 to 3% efficiency improvement. Meanwhile, due to the higher switching speed and different circuit layout, IPEM version has higher EMI noise comparing with discrete version converter [A-23][A-24].

# Chapter 2. Investigation of High Switching Frequency PFC

#### 2.1 Introduction

For distributed power systems (DPS), high power density, low profile begins to be the standard approach. For a typical front-end AC/DC converter shown in Figure 2-1, EMI filter and PFC inductor take about half of the total converter volume. Therefore, it is essential to shrink the size of EMI filter and PFC inductor to achieve higher power density. Since the size of passive components of the converters decrease with the increasing of switching frequency, to achieve higher power density, converters are operating with continuously increasing switching frequencies.

Figure 2-1. Typical Front-end AC/DC converter.

Because PFC inductor design is based on the switching frequency current ripple, its size decreases with increasing switching frequency. Thus, high switching frequency is desirable to achieve higher power density. Furthermore, the higher switching frequency dramatically reduces PFC inductor size and inductance, as well as the parasitics, which further improves the circuit EMI performance.

However, the relationship between EMI filter size and switching frequency is not clear for PFC designers. As a result, limited efforts has been performed to push the PFC switching frequency higher, since the reduction of PFC inductor size could be easily overwhelmed by the increasing of EMI filter size and heat-sink size due to the higher switching loss.

In this Chapter, based on the simulation results and experimental results, a simple imperial equation was derived to predict the different mode (DM) and common mode (CM) noise for PFC circuit with different switching frequencies. According to the derived EMI noise, EMI filters can be designed for different switching frequencies to meet the EMI standard required. The analysis results showed that the switching frequency needs to be increased to certain level that both the PFC inductor size and EMI filter size can be reduced. According the analysis, switching frequency selection guideline is given. Later the experimental results verified the theoretical analysis.

#### 2.2 Switching frequency impact on the PFC inductor

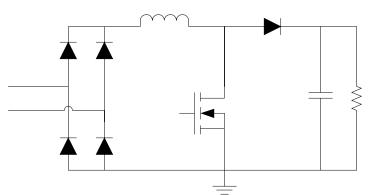

For power factor correction (PFC) circuit, constant switching frequency single switch PFC with continuous conduction mode (CCM) is the most widely used topology because of its simplicity and smaller EMI filter size [B-1][B-2]. The circuit diagram is shown in Figure 2-2, and it is constructed by the uncontrolled diode bridge, followed by a Boost converter.

Figure 2-2. Single switch CCM PFC.

For the CCM PFC circuit with constant switching frequency, PFC inductor (PFC inductor) is designed based on the switching frequency current ripple. To ensure smaller EMI filter size, current ripple peak to peak value is normally chosen as 20 to 30 % of maximum input line current. For instance, a 1kW PFC circuit with 150V minimum input voltage, considering 92% efficiency, the maximum input current is

$$I_{\text{max}} = \frac{1000}{150 \times 0.92} \times \sqrt{2} = 10.24 A$$

If considering 30% ripple current, the ripple current peak to peak value should be

$$I_{ripple} = 30\% \times I_{max} = 3.1A$$

Because of the input AC line voltage, duty cycle of PFC circuit changes along with the input line voltage. According to volt-second balancing on PFC inductor, duty cycle of PFC circuit can be calculated as

$$d = 1 - \frac{\left| v_{in} \right|}{V_{O}}$$

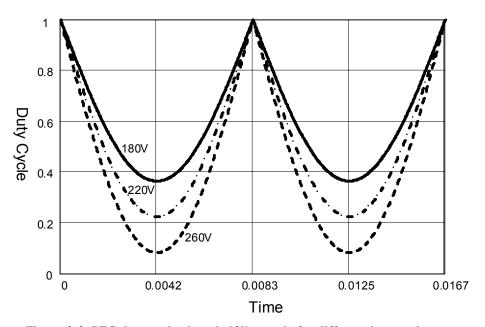

In this equation,  $V_O$  is the output voltage and  $v_{in}$  is the input line voltage instantaneous value. Normally, to ensure universal line input, the output voltage is chosen as 400V. Thus, the duty cycle along a half line cycle under different input line conditions can be calculated and demonstrated in Figure 2-3.

Figure 2-3. PFC duty cycle along half line cycle for different input voltages.

Based on the calculated duty cycle, current ripple can be calculated accordingly.

$$I_{ripple}(t) = \frac{V_o - |v_{in}|}{L_{boost}} (1 - d) T_S$$

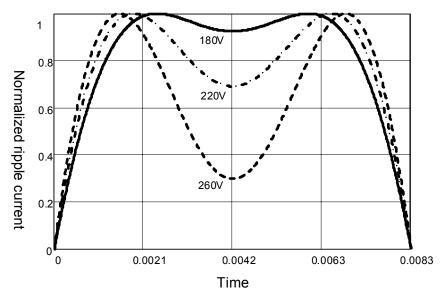

Here  $L_{boost}$  is the PFC inductor value and  $T_{S}$  is the switching cycle. Because the duty cycle changes along the line cycle, the ripple current changes correspondingly. As shown in Figure 2-4, current ripple reaches it maximum value when the input voltage instantaneous value is half of the output voltage. Because the input voltage is half of the output voltage, under this condition, the duty cycle of PFC circuit is 0.5.

Figure 2-4. Current ripple along the line cycle for different input voltages.

The maximum current ripple is used to design the PFC inductor. This maximum current ripple should be 20 to 30% of the maximum line current. Based on this, PFC inductor value can be calculated as

$$L_{boost}(f) = \frac{1}{2f} \frac{V_o}{2I_{ripple}}$$

From this equation, PFC inductor value is the function of switching frequency, ripple current amplitude and output voltage. For the predetermined output voltage and ripple current amplitude, PFC inductor value is inverse proportional to the switching frequency. The higher the switching frequency, the smaller the boot inductor value is.

As shown in Figure 2-5, for 100 kHz, to keep 30% current ripple, PFC inductor value is required to be 350uH. When the switching frequency is pushed up to 400 kHz, to keep the same amount to current ripple, inductance could be reduced to 90uH, which results in 66% reduction in volume. In Table 2-1, the detailed comparison between these two inductors is summarized.

(b) 400 kHz PFC inductor Figure 2-5. PFC inductor for different switching frequencies.

| Switching frequency | Kool Mu Core | Wire  | Turns | Dimension (D×L) |

|---------------------|--------------|-------|-------|-----------------|

| 100 kHz             | 77083 X 2    | AWG16 | 49    | 1.57in X 1.14in |

| 400 kHz             | 77059 X 4    | AWG16 | 26    | 0.9in X 1.2in   |

Table 2-1. PFC inductor comparison for different switching frequencies.

From the comparison, effectiveness of increasing switching frequency is demonstrated. Although the higher switching frequency can largely increase the core loss density of the PFC inductor, due to less core material, the core loss only increases 4W. Meanwhile, due to the much shorter winding length caused by smaller core size and less turns, copper loss of PFC inductor is largely reduced. The loss comparison between two inductors is summarized in Table 2-2.

Table 2-2. Loss comparison between two PFC inductors.

| Switching frequency | Core loss density     | Core loss | Winding loss |

|---------------------|-----------------------|-----------|--------------|

| 100 kHz             | $2.11 \text{W/in}^3$  | 2.95W     | 2.51W        |

| 400 kHz             | 14.9W/in <sup>3</sup> | 7.14W     | 1.4W         |

# 2.3 Switching frequency impacts on EMI filter design

As demonstrated before, PFC inductor and EMI filter size occupies large portion of total converter volume. Although by increasing the switching frequency, PFC inductor size can be largely reduced, it is still questionable that the EMI filter size might be increased at higher switching frequency. Therefore, it is essential to design the EMI filters for different switching frequencies and exam the switching frequency impacts on EMI filter size.

## 2.3.1 EMI filter design procedure

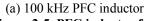

For telecom and server applications, EMI standard EN55022 Class B is widely used, as shown in Figure 2-6. [B-3][B-4] The standard begins to regulate at 150 kHz. For the EMI noise frequency lower than 150 kHz, there is no regulation requirement. For the noise frequency between 150 kHz and 500 kHz, the limit level decreases from 66dBuV to 56dBuV linearly with the logarithm of the frequency. For EMI noise frequency between 500 kHz and 5 MHz, limit level is 56dBuV. For EMI noise frequency between 5 MHz to 30 MHz, limit level is 60dBuV. Because there is no EMI noise requirement for the noise frequency lower than 150 kHz, the EMI filter design can take the advantage of that.

Figure 2-6. EN55022 Class B EMI standard.

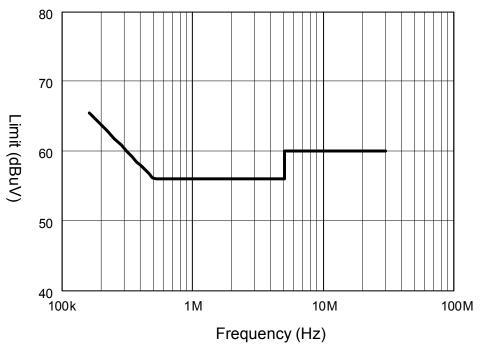

To meet the EMI standard requirement, passive EMI filters are widely used [B-5]. Normally two-stage EMI filters are used because they can achieve higher attenuation comparing with single stage EMI filter. A typical two stage EMI filter is demonstrated in Figure 2-7.

Figure 2-7. Two-stage EMI filter.

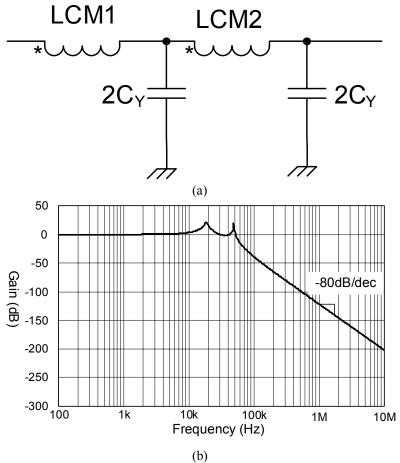

The filter is mainly constructed by common mode choke LCM1, LCM2 and corresponding X and Y capacitors. To achieve smaller filter size, leakage inductors of common mode chokes are used as different mode filter inductor LDM1 and LDM2. Because different noise transferring mechanisms, the two-stage EMI filter can be separated into differential mode (DM) filter and common mode (CM) filter.

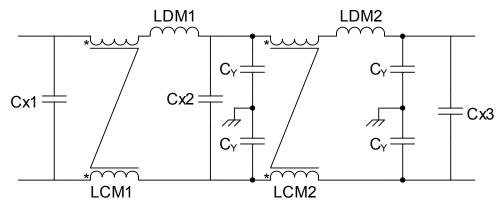

Equivalent circuit of different mode filter is shown in Figure 2-8 (a). Because it has two inductors and three capacitors, its gain gains characteristic keeps -100dB/dec decreasing slop, which ensures higher attenuation at higher frequencies.

Figure 2-8. Two-stage differential mode filter; (a) Equivalent circuit, (b) Filter attenuation.

The equivalent circuit of the CM filter is shown in Figure 2-9 (a). Due to the two-L and two-C structure, gain characteristic of CM filter has a -80dB/dec decreasing slope, as shown in Figure 2-9 (b), which means higher attenuation can be achieved at high frequency range.

Figure 2-9. Two-stage common mode filter, (a) Equivalent circuit, (b) Filter attenuation.

The design of EMI filter is to achieve desired noise attenuation to make the filtered noise meet EMI standard requirement. Different EMI filter design methods have been proposed by several references. According to the method discussed in [B-6][B-7][B-8], the design of EMI filter can be simplified as three steps.

Firstly, the circuit operates without EMI filter. The base-line CM and DM noises ( $V_{CM}$  and  $V_{DM}$ ) are measured through noise separator. After that, the

measured noises are compared with EMI noise standard to get the noise attenuation requirement curve for different frequencies.

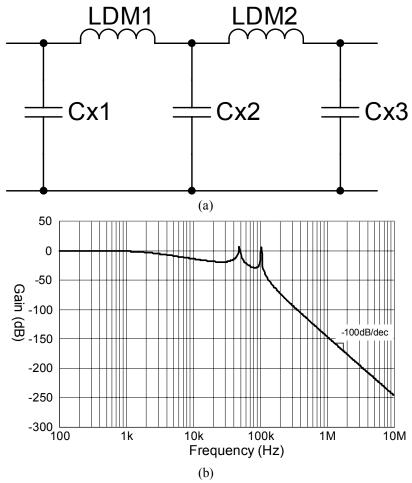

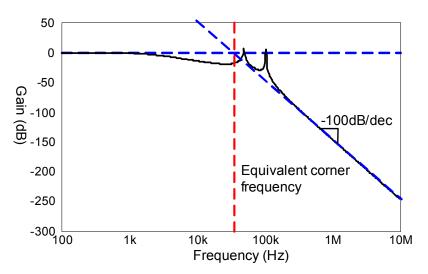

Finally, the corner frequency of CM filter is obtained by drawing a 40dB/dec-slope line to tangent to the required CM attenuation curve. The horizontal intercept of the line and 0dB axis determines the CM filter corner frequency. According to this corner frequency, the filter components can be designed accordingly. Same design process can be used to design the DM filter. This 40dB/dec-slope is based on the assumption of single stage EMI filter. However, for the two-stage EMI filter, it is required to use 80dB/dec-slope for CM filter design and 100dB/dec-slope for DM filter design. Furthermore, the determined the corner frequency is the equivalent corner frequency, as illustrated in Figure 2-10.

Figure 2-10. Equivalent corner frequency of two stage filter.

Although this equivalent corner frequency could represent infinite numbers of filters with different sizes, because of different filter design method, it is still can be used to evaluate the EMI filter size for the same filter design method. Higher equivalent corner frequency means smaller EMI filter size and higher power density.

Apparently, this design procedure assumes that the attenuation of EMI filter continuous increases with frequency. However, due to circuit parasitics, EMI filter attenuation decreases when the switching frequency is much higher than its corner frequency. Therefore, slightly modification might be required to meet the high frequency EMI specification. However, the EMI filter size is mainly determined by the low frequency noise.

## 2.3.2 EMI noise prediction of PFC circuit

Based on the described EMI filter design procedure, EMI filter can be designed with the measured CM and DM noise. To exam the switching frequency impacts on EMI filter, it is required to get the EMI noise for different switching frequencies. Since it is impossible to build the converters for all the frequency range, EMI noise of PFC circuit should be predicted by analytical model, which is much more time and cost effective.

During the past years, some research efforts have been executed to build the noise models to predict EMI performance of single switch CCM PFC circuit [B-

9][B-10][B-11][B-12][B-13]. Among different EMI noise prediction methods, the EMI noise is either calculated through time domain simulation or frequency domain calculation. Through simulation tools, EMI performance can be predicted and the effects of parasitic components can be analyzed. Most of the noise models are focus on precisely predicting the EMI performance of PFC circuit for whole conducted EMI frequency range. To accurately calculate the high frequency noise using time domain simulation, small simulation step and long simulation time are required. Thus, it is extremely time consuming and requires long data processing time. To reduce the simulation time, frequency domain simulation is proposed. Moreover, circuit parasitic components are required to be measured or extracted, because most of the circuit parasitic components, such as the trace inductances, will affect EMI noise at high frequency range.

According to the EMI filter design procedure, only low frequency noises are used to calculate EMI filter corner frequency. And those noise frequencies are the harmonics of the switching frequency. Therefore, the complex EMI model for PFC circuit is not necessary. Thus, instead of predicting the EMI performance for the whole conduction noise frequency range, a simplified EMI noised model can be used to predict the EMI noise for the switching frequency harmonics.

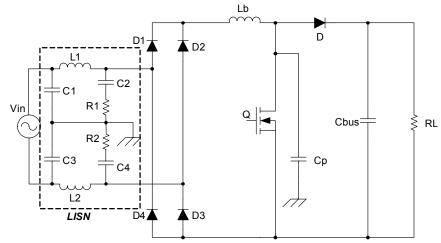

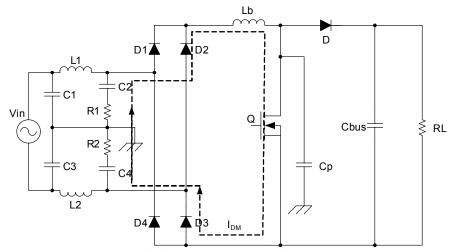

For conventional CCM PFC circuit with constant switching frequency and average current mode control, because of turning on and off of MOSFET, large EMI noise is generated. According to the different noise transferring mechanism,

the EMI noise can be separated into differential mode (DM) noise and common mode (CM) noise. DM noise is mainly affected by PFC inductor. And CM noise is determined by the parasitic capacitor between the MOSFET drain to the earth to ground. PFC circuit with parasitic capacitor is demonstrated in Figure 2-11.

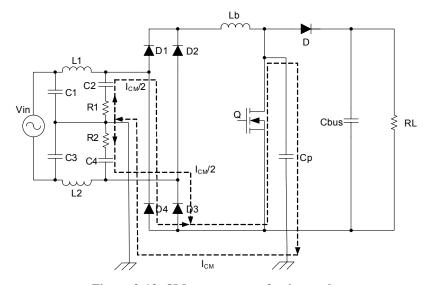

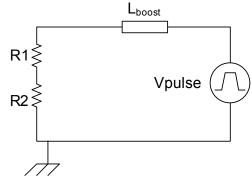

Figure 2-11. PFC circuit with LISN and parasitic capacitor.

In the circuit diagram shown in Figure 2-11, line impedance stabilize network (LISN) is the standard EMI measurement equipment, which can detect the EMI noise through LISN resistors R1 and R2. Because LISN inductors and capacitors construct a high pass filter, most of the EMI noise current goes through LISN resistors. Since the PFC circuit operates with CCM operation mode, input diode bridge can be ignored in the noise path. For the DM current transferring path, as demonstrated in Figure 2-12, includes the PFC inductor, switch circuit, LISN capacitors C2, C4 and LISN resistors R1, R2.

Figure 2-12. DM current transferring path.

As fort the CM current path, it includes the parasitic capacitor Cp, and LISN resistors. Because of large impedance of PFC inductor, most of CM current goes through the low-impedance negative bus. The CM current path is demonstrated in Figure 2-13.

Figure 2-13. CM current transferring path.

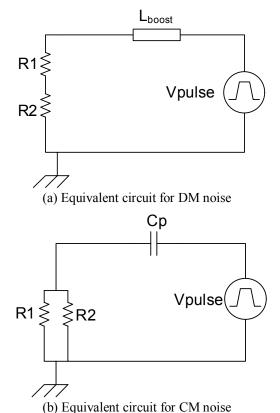

Because of the switching of MOSFET, voltage across MOSFET drain to source is a pulse voltage, which pulsates from 0 to output voltage (400V). Its

rising time and falling time is much smaller than the switching cycle and depends on the driving circuit and the switching performance of MOSFET. Therefore, the MOSFET diode and output circuit can be represented by a pulse voltage. This pulse voltage is the noise source for both DM and CM currents. To predict the EMI noise, this pulse voltage source shouldn't have DC component. Meanwhile, for the conduction EMI frequency range 150 kHz to 30 MHz, the impedance of capacitor C2 and C4 are much smaller than 50Ω LISN resistor. Therefore, for the EMI noise transferring path, LISN can be considered as two resistors. By doing these simplifications, the equivalent circuit for calculating DM and CM current can be illustrated by Figure 2-14 (a) and (b), respectively.

Figure 2-14. Equivalent circuit for EMI noise.

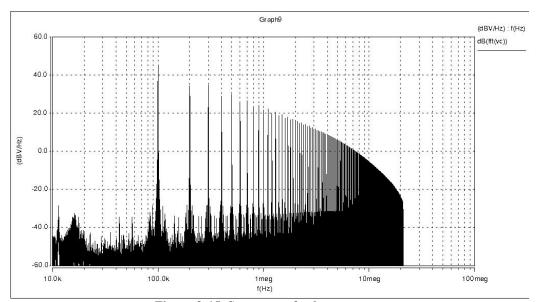

Because PFC circuit has a regulated 400V DC output voltage, its duty cycle is determined by the relationship between input voltage and output voltage, and varies along the line cycle. Spectrum of the voltage source cannot be express by a simple equation. Therefore, Saber simulation is used to get the spectrum of the noise source, as demonstrated in Figure 2-15.

Figure 2-15. Spectrum of voltage source.

From the spectrum, it can be observed that, at switching frequency, the noise source has the amplitude of 45.4dBV. The switching frequency harmonics keeps - 20dB/dec slope decreasing. Therefore, the noise source amplitude at harmonics of switching frequency can be derived as

$$V(nf_s) = 45.4 - 20\log(n) \text{ dBV}$$

In this equation,  $f_s$  is switching frequency and n is the harmonic order.

From the simulated spectrum, it also can be observed that at high frequency range, the enveloped changes into -40dB/dec, which is caused by the pulse voltage rise and fall time. However, for the EMI filter design, as described before, only the low frequency noise determines EMI filter components values and size. Therefore, the effects of rise and fall time can be ignored for this analysis, and the envelope of the voltage source can be simplified as a -20dB/dec slope, as demonstrated in Figure 2-16.

Figure 2-16. Spectrum envelope of PFC noise source.

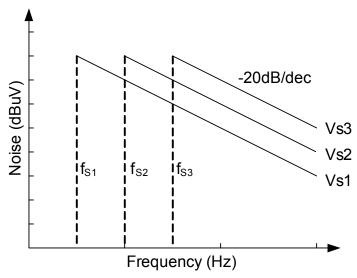

Moreover, because the spectrum is only determined by the voltage level and duty cycle, when the switching frequency changes, the whole spectrum moves along the frequency axis but keeps the same level.

Based on the principle of superposition, the measured EMI noise on LISN resistors can be calculated used the noise source spectrum and the path impedance.

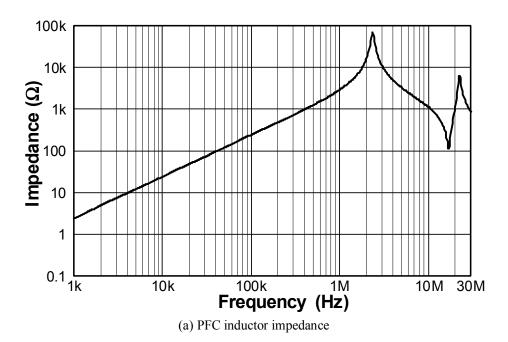

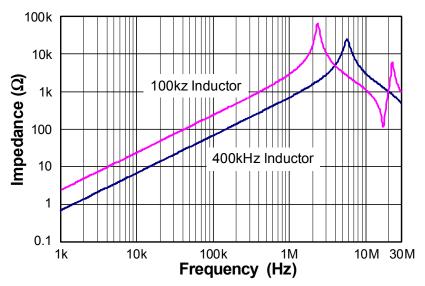

For DM noise, the path impedance is determined by the PFC inductor and LISN resistor. Because inductor impedance is proportional to the frequency, it has a 20dB/dec slope. For different switching frequencies, to keep the same ripple current, PFC inductor is reverse proportional to the switching frequency. Therefore, the loop impedance decreases with the increasing switching frequency.

Figure 2-17. DM noise path impedance for different switching frequency.

The voltage across the LISN resistor is determined by the impedance of PFC inductor at switching frequency. Because the noise source spectrum has a -20dB/dec slope envelop and loop impedance has a 20dB/dec slope, the measured DM noise spectrum has a -40dB/dec envelope slope. Thus, DM noise level can be calculated as

$$\begin{aligned} V_{DM}(nf_S) &= V(nf_S) - 20\log(Z_{Lboost}) + 20\log(50) \\ &= 200 - 20\log(2\pi f_S L_{boost}) - 40\log(n) \end{aligned}$$

In this equation, the unit for the amplitude changes into dBuV and same as the standard required. Because the PFC inductor is inverse proportional to the

switching frequency, the switching frequency has no impacts on the amplitude of DM noise. As shown in Figure 2-18, DM noise spectrum envelope moves horizontally with different switching frequency, while keeps the same amplitude.

Figure 2-18. DM noise spectrum envelope for different switching frequencies.

For CM noise, the path impedance is determined by the parasitic capacitor between MOSFET drain to earth ground, and LISN resistors. Because the impedance of capacitor is reverse proportional to frequency, it has a -20dB/dec slope. Moreover, this parasitic capacitor is determined by the circuit layout. Therefore, the capacitor keeps similar for different switching frequencies. As shown in Figure 2-19, CM noise path impedance keeps the same for different switching frequencies.

Figure 2-19. CM noise path impedance for different switching frequency.

Together with -20dB/dec slope of noise source spectrum envelope, CM noise should have a flat envelope. Because the CM current is evenly distributed into two LISN resistor, each LISN resistor sees half of CM current. CM noise amplitude can be calculated as

$$V_{CM}(nf_S) = V(nf_S) - 20\log(Z_{Cp}) + 20\log(25) = 193.4 + 20\log(2\pi f_S C_p)$$

In this equation, unite is also changed into dBuV and complied with the standard requirement. From the equation, CM noise envelope is proportional to the switching frequency. Furthermore, for different switching frequency harmonics, they keep the same amplitude.

Figure 2-20. CM noise spectrum envelope for different switching frequencies.

Apparently, these noise spectrum envelops only valid for the low frequency range, or in other words, the harmonics of switching frequency noises. It should not be used for high frequency noise prediction.

To verify the model, a 1kW, 100 kHz switching frequency single switch CCM PFC was built. The test data and predict data are shown in Table 2-3. The differential mode noise model can well predict the noise amplitude. Although there is several dBs error on the prediction noise, considering the design margin for the EMI filter, this simple equation can be used for the differential mode filter design for single switch CCM PFC circuit.

Table 2-3. EMI model prediction vs. experimental results.

| Frequency     | 100k      | 200k    | 300k    | 400k    |

|---------------|-----------|---------|---------|---------|

| Test Noise    | 149dBuV   | 127dBuV | 131dBuV | 121dBuV |

| Predict Noise | 149.5dBuV | 137dBuV | 130dBuV | 125dBuV |

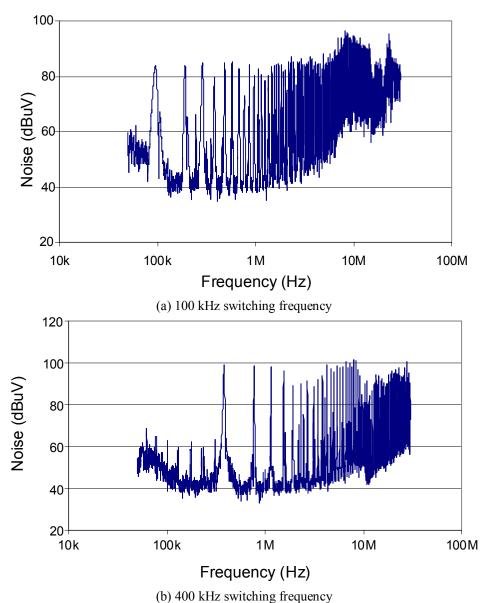

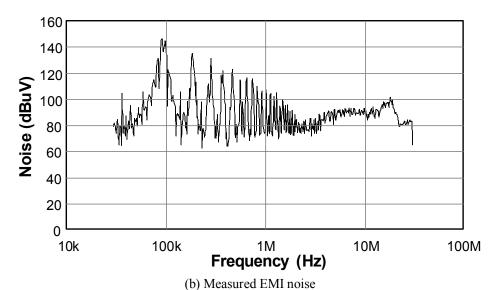

To verify the common mode noise model, the PFC circuit common mode noises at different switching frequencies are measured, as shown in Figure 2-21. From experimental results, it can be observed that all the common mode noises have flat envelope, and the amplitude is proportional to the switching frequency.

Figure 2-21. Measured common mode noise.

## 2.3.3 Filter size evaluation for different switching frequencies

Based on the described EMI filter design procedure, together with the predicted EMI noise for different switching frequencies, EMI filters for PFC with different switching frequencies can be designed accordingly.

CM and DM filters are designed separately. By comparing the predicted EMI noise with EMI standard, attenuation requirement for the EMI filter can be derived. According to the required attenuation and its corresponding frequency, the EMI filter can be designed. CM filter corner frequency is the intersection of 0dB and 80dB/dec-slope line tangent with attenuation requirement. DM filter corner frequency is the intersection of 0dB and 100dB/dec-slope line tangent with attenuation requirement. Because of the sharp slope of CM and DM filter attenuations, the tangent point is always the first switching frequency harmonic that has frequency higher than 150 kHz. Therefore, the EMI filter can be designed based on the noise of this harmonic.

We define the frequency that used to design the EMI filter as the **Worst Frequency**, which is the first noise frequency that is higher than 150 kHz. Because the EMI noise is the harmonics of switching frequency noise, the worst frequency should be the N<sup>th</sup> switching frequency harmonic. Here N is an integer and should fulfill the equation.

$$(N-1)f_{\scriptscriptstyle S}<150kHz\leq Nf_{\scriptscriptstyle S}$$

Here,  $f_S$  is the switching frequency. The worst frequency can be calculated as

$$f_{worst}(f_S) = Nf_S$$

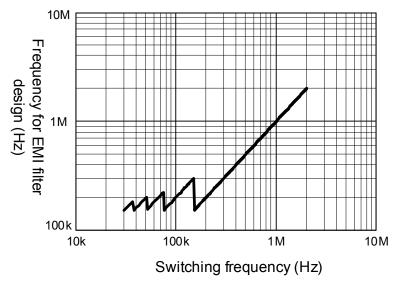

From this equation, when switching frequency is 70 kHz, the worst frequency should be the 3<sup>rd</sup> harmonic, which is 210 kHz. While for switching frequency is 80 kHz, the worst frequency should be the 2<sup>nd</sup> harmonic, which is 160 kHz. Therefore a slightly change on the switching frequency could cause big difference on EMI filter design. Relationship between switching frequency and worst frequency is shown in Figure 2-22. From this curve, it can be observed that the worse case frequency has dramatically changes around the frequencies that are fractures of 150 kHz, for the switching frequencies lower than 150 kHz. But when switching frequency is higher than 150 kHz, the worst frequency is always the switching frequency, and there will be no dramatically change.

Figure 2-22. Worst frequency vs. switching frequency.

#### A) Differential mode filter

According to DM noise analysis, DM noise at switching frequency harmonics can be represented as

$$V_{DM}(nf_s) = 200 - 20\log(2\pi f_s L_{boost}) - 40\log(n)$$

Because the PFC inductor is designed based on the percentage current ripple, it is more convenient to calculate DM noise based on the ripple current.

To simplify the analysis, a 1kW PFC with universal input is considered as a design example. Because the PFC circuit derates at 150V AC input, the maximum current happens at 150V AC input. The maximum current is

$$I_{\text{max}} = \sqrt{2} \frac{P_o}{V_{in}} = 9.43 A$$

The maximum ripple current is set to be certain percentage of  $I_{\rm max}$ . If defining  $ripple \ {\rm as \ the \ percentage \ number, \ the \ maximum \ ripple \ current \ can \ be \ calculated,}$

$$I_{\mathit{ripple}} = ripple \times I_{\max}$$

According to the ripple current and switching frequency, DM noise can be represented by the ripple current as

$$V_{DM}(nf_s) = 164 + 20\log(ripple) - 40\log(n)$$

Therefore, DM filter attenuation requirement at worst frequency for different switching frequencies should be the difference between the DM noise and the EMI standard, as shown in the following equation.

$$Att_{DM}(f_{worst}) = V_{DM}(f_{worst}) - V_{lim}(f_{worst}) + 6$$

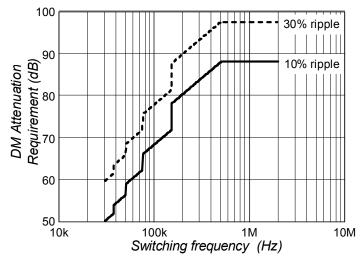

To leave design margin 6dB attenuation is added. By using the derived equation, DM filter attenuation requirement for different switching frequency can be calculated, as shown in Figure 2-23.

Figure 2-23. DM filter attenuation requirement.

Similar to the worst frequency, the attenuation requirement has dramatically change around switching frequency is equal to 50 kHz, 75 kHz and 150 kHz, etc. For instance, when the switching frequency is 70 kHz, filter design is based on the 3<sup>rd</sup> harmonic, which is 19dB lower than the switching frequency noise. However, when the switching frequency is 80 kHz, EMI filter design is based on the 2<sup>nd</sup> harmonic, which is only 12dB lower than the switching frequency noise. Because for different switching frequencies, once keeping the same current ripple, the switching frequency noise keeps the same amplitude. Therefore, attenuation required for 80 kHz switching frequency is much smaller than that for 70 kHz switching frequency.

According to the worst frequency and attenuation requirement, the equivalent corner frequency of DM filter can be calculated. The relationship between the required attenuation and the equivalent corner frequency can be demonstrated by

$$Att_{DM}(f_{worst}) = 100 \log \left( \frac{f_{worst}}{f_{C_{-}DM}} \right)$$

Therefore, the equivalent corner frequency can be calculated as

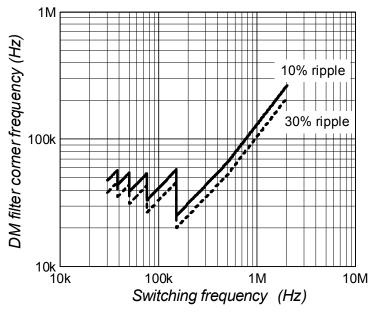

$$f_{C\_DM} = f_{worst} \times 10^{-\frac{Att_{DM}(f_{worst})}{100}}$$

Based on this equation, the relationship between the required equivalent corner frequency and the switching frequency is shown in Figure 2-24. The curve is a zigzag shape. When the switching frequency is slightly lower than certain frequencies, such as 50 kHz, 75 kHz, and 150 kHz, the equivalent corner frequency of the EMI filter is much higher. This is caused by the combination of worst frequency change and attenuation requirement change. Therefore, a slightly change of the switching frequency could result in largely increase of EMI filter size. Thus, the PFC circuit switching frequency should keep slightly on the left side of those frequencies. Furthermore, when the switching frequency is higher than 450 kHz, the DM filter equivalent corner frequency will keep increasing and higher than those for other switching frequencies.

Figure 2-24. Corner frequency of DM filter vs. switching frequency.

#### B) Common mode filter

Following the same evaluation process, the common mode filter size can also be evaluated. According to previous analysis, CM noise amplitude for PFC circuit should be

$$V_{CM}(nf_S) = 193.4 + 20\log(2\pi f_S C_p)$$

From this equation, it can be observed that CM noise is proportional to the switching frequency and parasitic capacitor. For different switching frequencies, if keeping the similar layout, the parasitic capacitor keeps the same. Although it is difficult to get a specific capacitor value, several  $C_p$  values can be used to estimate its effects. Therefore, in the calculation,  $C_p$  is chosen as 100pF, 300pF and 500pF. Based on the common mode noise and EMI standard, together with CM noise amplitude, the required attenuation can be calculated as

$$Att_{CM}(f_{worst}) = V_{CM}(f_{worst}) - V_{lim}(f_{worst}) + 6$$

Same as DM filter, 6dB design margin is added. As shown in Figure 2-25, the attenuation requirement for different switching frequency has the similar shape as DM filter. Moreover, larger the parasitic capacitor, higher the attenuation is required for CM noise.

Figure 2-25. CM attenuation requirement.

According to the worst frequency and attenuation requirement, the equivalent corner frequency of CM filter can be calculated. The relationship between required attenuation and the equivalent corner frequency can be demonstrated by

$$Att_{CM}(f_{worst}) = 80 \log \left(\frac{f_{worst}}{f_{C\_CM}}\right)$$

Therefore, the equivalent corner frequency can be calculated as

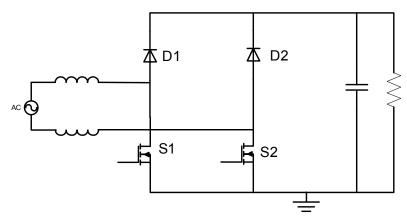

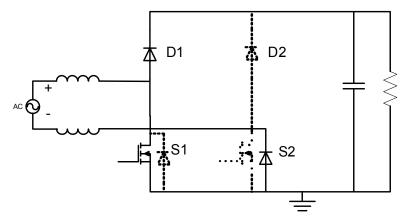

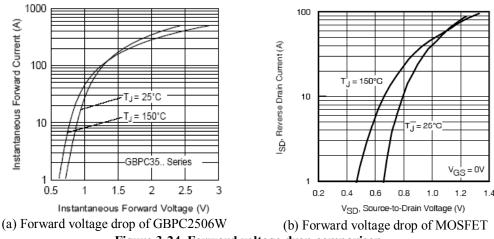

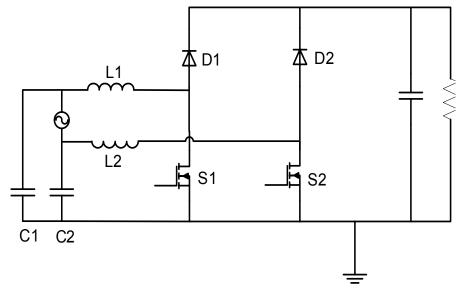

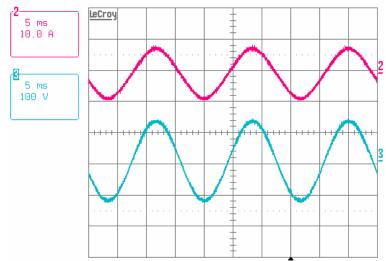

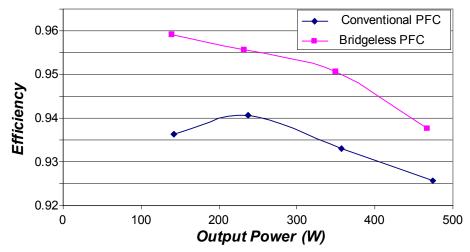

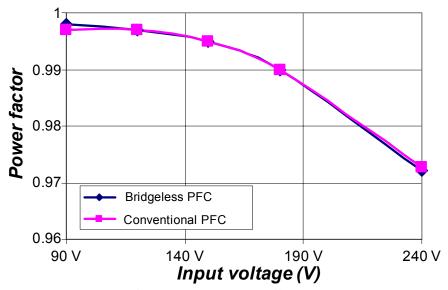

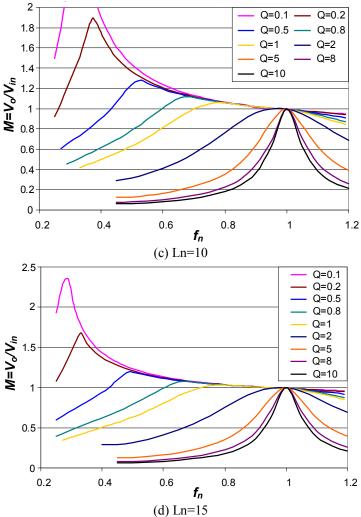

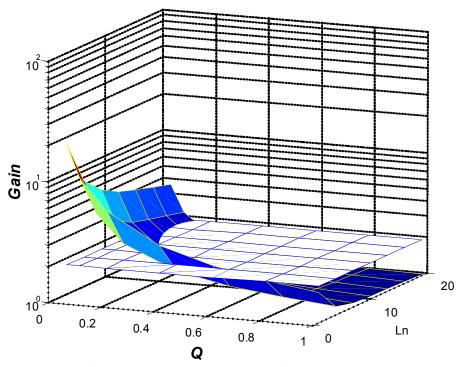

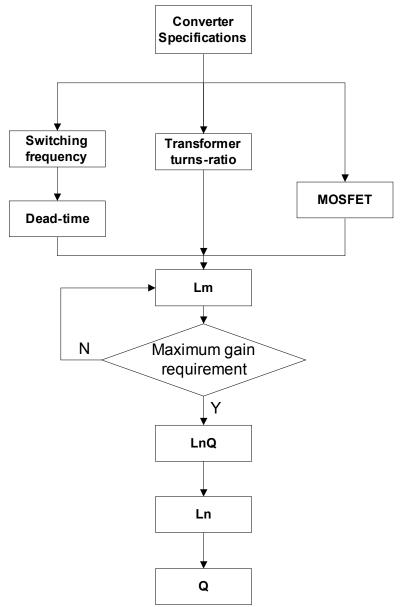

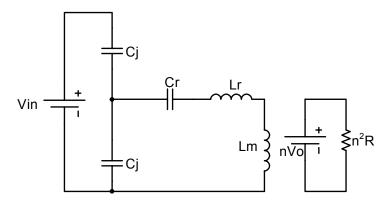

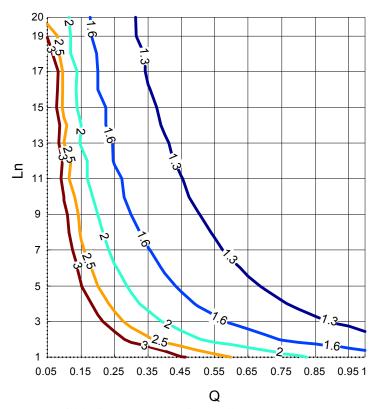

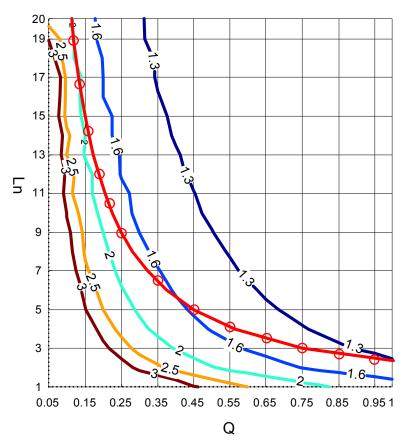

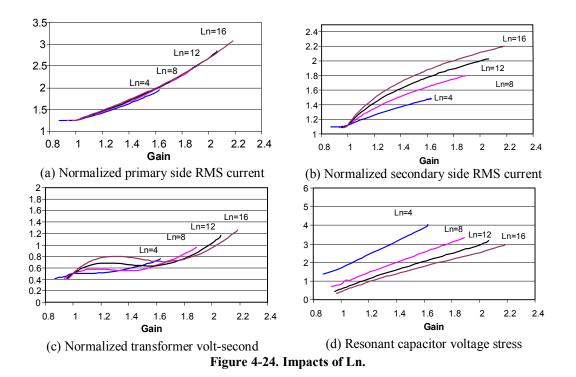

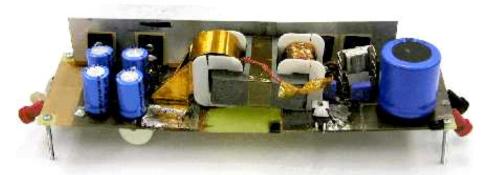

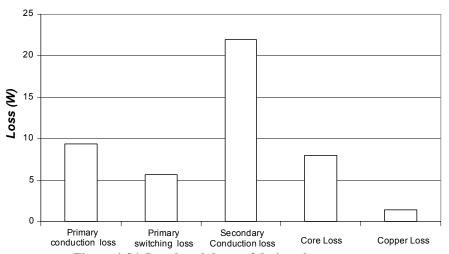

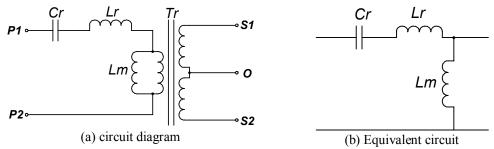

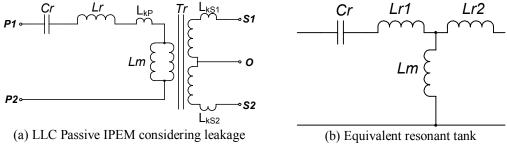

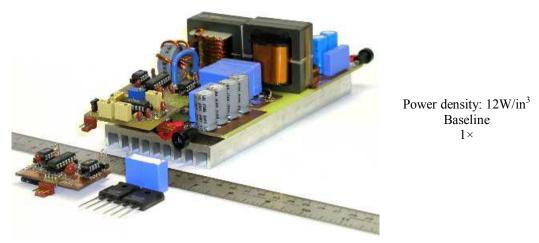

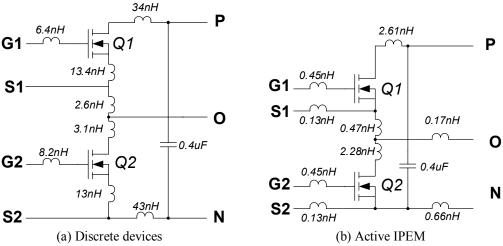

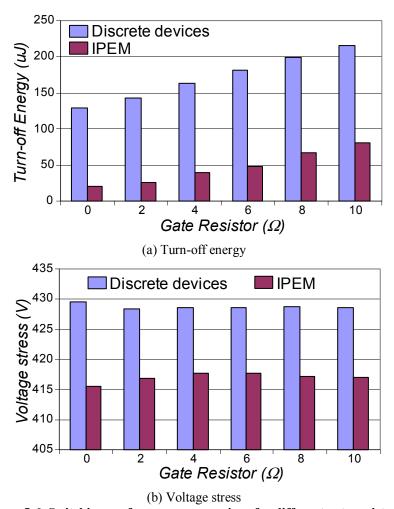

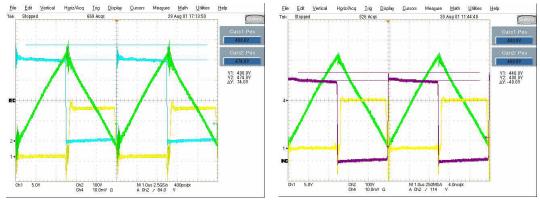

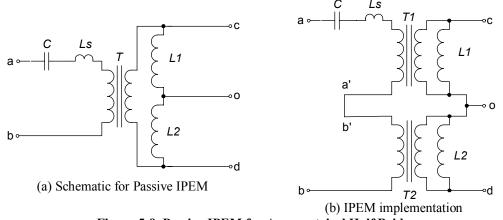

$$f_{C\_CM} = f_{worst} \times 10^{-\frac{Att_{CM}(f_{worst})}{80}}$$