# A Wide Input Voltage and Load Output Variations Fixed-Frequency ZVS DC/DC LLC Resonant Converter for High-Power Applications

Francisco Canales, Peter Barbosa and Fred C. Lee Center for Power Electronics Systems - CPES The Bradley Department of Electrical and Computer Engineering Virginia Polytechnic Institute & State University Blacksburg VA 24060-0179, U.S.A. fcanales@vt.edu

*Abstract*—This paper presents a fixed-frequency zerovoltage-switching three-level DC/DC resonant converter. By applying phase-shift control between the primary and secondary sides of the transformer, the converter can operate at a fixed switching frequency. The converter can achieve ZVS operation in the entire load range by using the magnetizing inductance of the transformer. In addition, the converter can operate with wide input-voltage variations without penalizing the efficiency. Therefore, the converter is suitable for applications in which high efficiency and high power density are required. The principle of operation for the converter is analyzed and verified on a 2.75 KW, 775 kHz experimental prototype.

### Keywords—Converter circuit; multilevel converters; highfrequency power conversion; soft switching

#### I. INTRODUCTION

The next generation of power supplies not only has to meet the characteristics demanded by the load, but also has to process energy with high efficiency, high reliability, high power density and low cost. In order to achieve converters with high power densities, it is usually required that they operate at higher switching frequencies.

As switching frequencies increase, the switching losses associated with the turn-on and turn-off of the devices also increase. In switch-mode PWM power supplies, the switching losses can be high enough that they prohibit the operation of the power supply at very high frequencies, even when softswitching techniques are used. In resonant-mode power supplies, however, the switching losses can be lower, allowing the resonant converter to operate at higher frequencies [1] [2]. Therefore, the use of resonant converters remains an interesting option for some applications requiring the previous specifications.

In resonant converters, MOSFET devices are appropriate for high switching frequencies, while zero-voltage switching (ZVS) is especially recommended. The conventional series resonant converter operates with ZVS for the active devices when the switching frequency is above the resonant frequency. However, for wide input voltage and output load variations, the converter must operate with wide switching frequency variations, which complicates optimization of the converter.

Some fixed-frequency control strategies have been proposed for resonant converters [3]-[7], which permit the optimization of the converter's magnetics, as well as its input and output filters. However, in order to achieve ZVS for a wide load variation, the converter must operate with a switching frequency much higher than the resonant frequency of the tank [5]; this results in large levels of circulating energy, which reduces the efficiency, and requires highpower-rating devices.

In addition, for high-input-voltage applications, the necessity of high-voltage-rating devices makes the problem even worse. It has been shown that three-level structures can alleviate this problem by reducing the voltage stress across the power switches to half of the input voltage [8]. Therefore, MOSFET devices with better characteristics can be used.

This work proposes a novel fixed-frequency ZVS threelevel DC/DC converter for high-input applications with wide input voltage and output load variations. The converter can operate with a wide ZVS range by using the magnetizing inductance of the transformer. In addition, the control is performed in the secondary side of the transformer, which helps to increase the ZVS range and reduce the circulating energy in the converter as well.

This paper first addresses the operation and analysis of the proposed converter. Later, a possible solution is given for reducing the effect of the wide input-voltage variation in the performance of the converter; in order to validate this solution, experimental results are provided.

# II. CIRCUIT DESCRIPTION

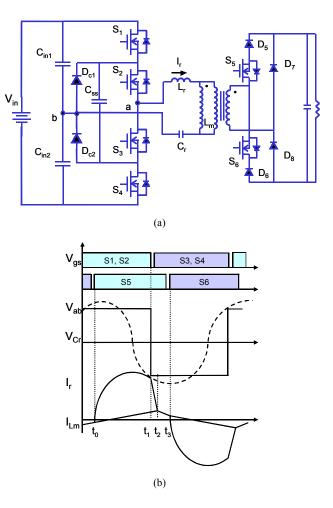

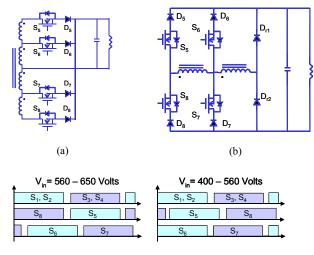

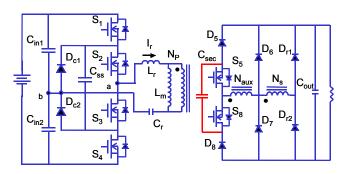

In this section, the operating principle of the fixedfrequency ZVS three-level DC/DC resonant converter is presented. The proposed converter and its timing diagram are shown in Fig. 1. It can be seen that the converter uses a threelevel structure in the primary side in order to reduce the voltage stress across the primary switches, which also allows the use of devices with better characteristics. In addition, an LLC series resonant tank is placed in the primary side to

This work was supported by Raytheon Electronic Systems, Conacyt (The Mexican Council for Science and Technology), Cenidet (Mexican Center for Research and Technological Development), CNPq (The Brazilian Council for Scientific Development), and the ERC Program of the National Science Foundation under award number EFC-9731677.

provide ZVS for the primary switches. One of the advantages the proposed converter offers over the traditional series resonant converter is that it can work above or below the resonant frequency determined by the series resonant tank formed by resonant inductance  $L_r$  and resonant capacitor  $C_r$ , and still achieve ZVS operation for the primary switches. The ZVS operation is achieved by using the energy stored in the magnetizing inductance of the transformer. This energy also allows the converter to operate with soft switching under a wide load range without necessitating an increase in the quality factor Q of the resonant tank and the ratio between switching and resonant frequencies. Consequently, the circulating energy in the converter is also reduced.

In order to achieve fixed-frequency operation and wide ZVS range, switches  $S_5$  and  $S_6$  are placed in the secondary side of the converter. This allows operation with phase-shift control in which all switches operate with duty cycles of nearly 50%. In the primary side, switches  $S_1$  and  $S_2$  are turned on and off simultaneously. Similarly, switches  $S_3$  and  $S_4$  are also operated simultaneously but with a 180° phase shift from  $S_1$  and  $S_2$ . The phase shift of  $S_5$  with respect to  $S_1$  and  $S_2$  or  $S_6$  with respect to  $S_3$  and  $S_4$  determines the operating duty cycle of the converter.

For simplification in the explanation of the converter operation, switches  $S_1$  and  $S_2$  or  $S_3$  and  $S_4$  are considered to be turned on and off simultaneously. However, a small delay must be introduced into the operation between them. In this way, auxiliary diodes  $D_{c1}$  and  $D_{c2}$  conduct, clamping the voltage across the primary switches to half the input voltage. In this case, flying capacitor  $C_{ss}$  is required for ZVS operation of switches  $S_1$  and  $S_4$ .

As explained in the next sections, the converter is designed in such a way that the current in the secondary side reaches zero before the turn-off of  $S_5$  or  $S_6$ . This allows zero-currentswitching (ZCS) operation for these switches. In addition, the reverse recovery problem for the diodes in the secondary side is minimized.

#### III. MODELING AND ANALYSIS OF THE CONVERTER

This section of the paper details the analysis of the proposed converter. Depending on the operating conditions, this converter presents two modes of operation. Each operating mode has three stages during each half of a switching cycle.

### A. Operating Mode I

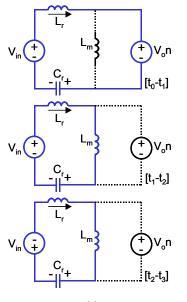

The first mode of operation occurs when the time for half the resonant period is smaller than the duty cycle applied to the converter. The equivalent circuit for each stage of this operating mode and waveforms are shown in Figs. 2(a) and 2(b), respectively. These stages are described below.

$[t_0-t_1]$ : Before this stage begins, switches  $S_1$  and  $S_2$  are on. At  $t_0$  the secondary switch  $S_5$  is turned on and the difference between half the input voltage and the reflected output voltage is applied across the resonant tank. Therefore, a resonance starts between series resonant capacitor  $C_r$  and series resonant inductor  $L_r$ . During this stage, the input power is delivered to the output.

Figure 1. (a) The proposed converter and (b) its main waveforms.

[t<sub>1</sub>-t<sub>2</sub>]: At t<sub>1</sub>, the resonant inductor current reaches the magnetizing current, causing the secondary side of the transformer to be disconnected from the primary side. During this time, a new resonance is carried out between magnetizing inductance  $L_m$ , resonant inductance  $L_r$  and resonant capacitor  $C_r$ .

[t<sub>2</sub>-t<sub>3</sub>]: At t<sub>2</sub>, primary switches S<sub>1</sub> and S<sub>2</sub> are turned off and S<sub>3</sub> and S<sub>4</sub> are turned on, applying a negative voltage across the transformer. During this stage, the secondary side remains disconnected from the primary side of the converter. In addition, the resonance continues between L<sub>r</sub>, L<sub>m</sub> and C<sub>r</sub>. At the end of this stage, the secondary switch S<sub>5</sub> is turned off under a zero-current condition and S<sub>6</sub> is turned on starting a new half of a switching cycle.

#### B. Operating Mode II

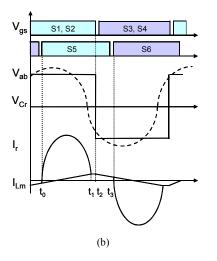

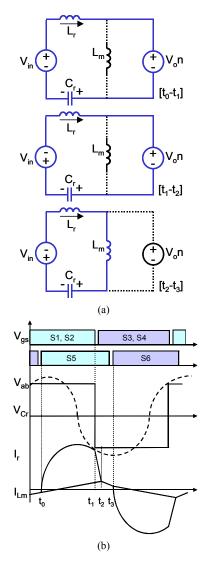

The second mode of operation occurs when the natural resonant period of the tank is interrupted, that is, when the duty cycle is smaller than half the resonant period. The equivalent circuits for this mode and the main waveforms are shown in Figs. 3(a) and 3(b), respectively. A brief description of this mode is given below.

$[t_0\hbox{-}t_1]\hbox{:}$  At  $t_0,$  the secondary switch  $S_5$  is turned on. In the primary side, switches  $S_1$  and  $S_2$  are already on, so the

difference between half the input voltage and the reflected output voltage is applied across the resonant tank. Therefore, a resonance starts between series resonant capacitor  $C_r$  and series resonant inductor  $L_r$ . During this stage, the input power is delivered to the output. This stage ends when switches  $S_1$ and  $S_2$  are turned off.

$[t_1-t_2]$ : At  $t_1$ , switches  $S_3$  and  $S_4$  are turned on, changing the polarity of the input voltage. The resonance between  $L_r$  and  $C_r$  continues. This stage ends at  $t_2$ , when the primary current reaches the magnetizing current.

$[t_2-t_3]$ : During this stage, the secondary side of the transformer is disconnected from the primary side. In this way, a resonance is carried out between L<sub>r</sub>, L<sub>m</sub> and C<sub>r</sub>.

At the end of this stage, the secondary switch  $S_5$  is turned off with zero current, and  $S_6$  is turned on, which starts a new half of a switching cycle.

Figure 2. Operating Mode I: (a) equivalent circuits for each stage, and (b) the main waveforms

Figure 3. Operating Mode II: (a) equivalent circuits for each stage, and (b) the main waveforms.

# C. Analysis of the Proposed Converter

From the operating modes of the converter, one can see that the solution of the system depends on the initial conditions of the resonant inductor current and resonant capacitor voltage. As a result, it is difficult to obtain a closed form solution for analyzing the converter. To obtain the steady-state operation, numerical methods can be used. A program implemented in Matlab was used to determine the main characteristics of the converter.

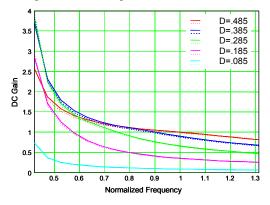

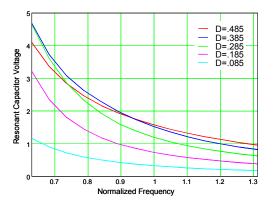

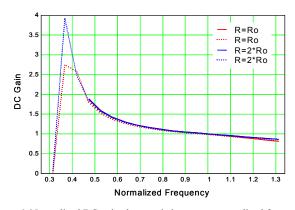

Figs. 4, 5 and 6 present some steady-state characteristics of the converter. Fig. 4 shows the normalized DC gain of the converter at different normalized switching frequencies, using the duty cycle as a running parameter. It is important to mention that the solid line represents the DC gain obtained by using the program implemented in Matlab, and the dotted lines represent the normalized DC gain obtained by simulation. It can be seen that there is close agreement between the calculated and simulated data. Fig. 5 shows the normalized voltage across resonant capacitor  $C_r$  for different normalized switching frequencies and using the duty cycle as a running parameter. Fig. 6 shows again the DC gain characteristic of the converter for different normalized switching frequencies, but now using the normalized load as a running parameter. Again, it can be seen that the simulated normalized gain (dotted line) is in accordance with the gain obtained with the Matlab program (solid line). It can be seen that with appropriate selection of the resonant elements, the converter presents a no-load-dependence voltage gain

As first guidelines, it can be seen that the converter has the capability to boost the input voltage when it operates below the normalized resonant frequency. In this case, ZVS operation is achieved using the energy in the magnetizing inductance. However, it is important to mention that the ZVS characteristic can be lost if the converter operates near the second resonant frequency, which is determined by  $L_r$ ,  $L_m$  and C<sub>r</sub>. In this case, the magnetizing current reverses its polarity before the turn-off of the switch. As a result, the converter will operate with ZCS instead of ZVS. In addition, the resonant capacitor is submitted to high voltage stress. Therefore, it is recommended that the converter be operated around the resonant frequency, which is given by the series resonant elements L<sub>r</sub> and C<sub>r</sub>. It is important to mention that the relationship between the magnetizing and resonant inductances gives the ZVS operation limit.

Figure 4. Normalized DC gain characteristics versus normalized frequency, using the duty cycle as a running parameter.

Figure 5. Normalized resonant capacitor voltage versus normalized frequency, using the duty cycle as a running parameter

Figure 6. Normalized DC gain characteristics versus normalized frequency using normalized load as a running parameter.

# IV. SOLUTION FOR WIDE INPUT VOLTAGE VARIATIONS

One of the problems associated with the resonant converters is their poor performance when they are submitted to wide input voltage variations. In this kind of application, the input voltage variation imposes both a reduction in the turns ratio of the transformer and wide variations in the duty cycle. Therefore, optimization of the converter is difficult to achieve, resulting not only in an incremental increases of the stresses in the power semiconductors and circulating energy in the converter, but also in a reduction in efficiency.

A solution for reducing the output filter requirements for a PWM converter has been proposed [9]. A similar approach can be followed to reduce the duty-cycle variations for a wide input-voltage application.

Figs. 7 and 8 present alternatives that can reduce the effect of the wide input voltage variations in the performance of the converter. The basic idea with this approach is to add an additional winding in the secondary side of the transformer. In this way, the operation of the converter can be optimized by changing the turns ratio of the transformer according to the input voltage.

Fig. 7 shows this approach using full control in the secondary side. This idea can be implemented in a centertapped or full-bridge structure, as shown in Figs. 7(a) and 7(b), respectively. As can be seen in Fig. 7(c), during a highline condition, the converter regulates the output voltage by phase-shifting  $S_6$  and  $S_7$  with respect to the primary switches. At the low-line condition, the regulation is carried out by switches  $S_5$  and  $S_8$ . By using this strategy, the secondary windings are connected in series to reduce the turns ratio of the transformer at low line. Therefore, a better optimization in the design of the converter can be achieved by reducing the variation in duty cycle.

Fig. 8 shows a simplified version of this approach also using a center-tapped or full-bridge structure. In this approach, partial control of the output voltage is achieved by removing two of the secondary switches. Both secondary windings are always connected in series for any input-voltage condition. The output voltage is controlled by adding more or less voltage to the main secondary. Therefore, the turns ratio of the transformer must be designed in such a way that for high–line input voltage and no load, the converter is still able to regulate the output voltage. As can be seen, due to this condition the optimization of the converter is a little more difficult to achieve than for the solution presented in Fig. 7.

As can be seen in Figs. 7(b) and 8(b), by using a fullbridge configuration in the secondary side, it is possible to reduce the complexity in the construction of the transformer. However, this solution increases the conduction losses in the secondary side due to the addition of extra diodes  $D_{r1}$  and  $D_{r2}$ . In order to have a better idea of which kind of secondary side provides a better solution, it is necessary to perform an analysis using simulation tools such as Maxwell to predict the current distribution in the windings of the transformer.

Although improvements in the performance of the converter can be obtained by using the previous approaches, there is a trade-off between simplification and optimization of the converter.

(c)

Figure 7. Solutions for wide input variation - full control of the output voltage: (a) center-tapped configuration, (b) full-bridge configuration, and (c) control signals.

Figure 8. Simplified solutions for wide input variation: (a) center-tapped configuration, (b) full-bridge configuration, and (c) control signals.

# V. EVALUATION AND COMPARISON

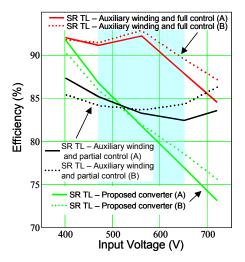

This section of the paper presents a theoretical comparison between the proposed converter that uses a single winding in the secondary side, as shown in Fig. 1(a), and the solutions proposed for wide input voltage variations. Among the solutions for wide input voltage variations, the center-tapped approaches with full and partial control in the secondary side are considered. This comparison takes into account the conduction and switching losses of all power semiconductors (active switches and diodes). The specifications for this comparison are as follows. V<sub>out</sub> = 60 Volts, I<sub>out</sub>=44.5 Amperes, V<sub>in</sub> = 400 – 650 Volts, and f<sub>s</sub> = 750 kHz.

It is important to mention that the efficiency was calculated for each converter using two different MOSFET devices for the primary switches. The MOSFET (A) is a 500 V, 58 A device. The MOSFET (B) is a 500 V, 32 A device that presents higher  $R_{dson}$  resistance but better switching characteristics. All converters were designed to work at 1.05 times the resonant frequency. In addition, this design allows the converter to achieve ZVS operation from full load to 10% of full load.

As can be seen in Fig. 9, the proposed converter presents a low efficiency at high-line input voltage. At this operating condition, the switching losses of the converter are dominant since the primary switches are turned off almost at the peak of the resonant current. At low-line input, the primary current is allowed to almost complete the entire resonant period, reducing the turn-off losses. As previously mentioned, the switching losses can be almost eliminated if the converter operates in operating mode I. That means that during the turn-off instant, only the magnetizing current circulates through the primary switches. However, this could be penalized with higher conduction loss and voltage stress in resonant capacitor  $C_{\rm r}$ .

An improvement in the efficiency at high-line conditions can be achieved by placing an auxiliary winding in the secondary side of the transformer. With the auxiliary winding and full-control approach, better optimization of the converter can be achieved. Therefore, the efficiency improvement is more significant. The converter was designed in such a way that at nominal input voltage (560 V), the primary current is allowed to almost complete the resonant period; in this way, the turn-off losses are reduced, which improvs the efficiency at this operating condition.

Although an improvement in the efficiency of the proposed converter at high-line conditions is achieved using the auxiliary winding and partial-control approach, it is penalized with an incremental increase in the conduction losses at low line. It is important to mention that the proposed converter, which uses this approach must be designed in such a way that the converter still regulates the output voltage at high-line and no-load conditions. Therefore, optimization of the converter is more difficult to obtain.

Figure 9. Theoretical efficiency comparison between the proposed converter and the solutions for wide input variations.

#### VI. DESIGN AND EXPERIMENTAL RESULTS

This section presents the design and the experimental results for the proposed converter. In order to see the benefits in the converter, it was designed to meet wide input voltage (400 V -650 V) and load range variations (4.4 A - 44.5 A at 60 V output voltage).

# A. Design of the Converter

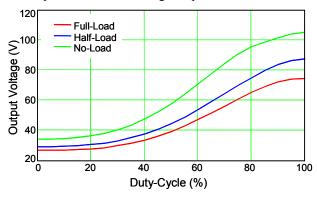

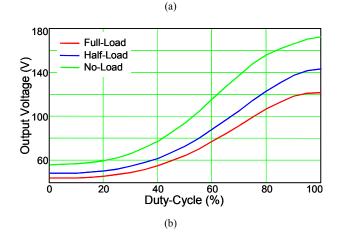

With the idea to design a converter with high power density, and considering the results of a study that determined the optimum switching frequency for the LCT component [10] (integration of the passive components; i.e., inductor, capacitor and transformer), it was decided to operate the converter with a fixed switching frequency of between 750 and 800 KHz. In addition, in an attempt to improve the efficiency shown in Fig. 9, the converter was designed with a resonant frequency higher than the switching frequency. In this way, the primary resonant current has more time to resonate, which reduces the turn-off losses for the primaryside switches. In addition, the turns ratio of the transformer was selected in order to provide output voltage regulation at critical operating conditions. These conditions occur at both full load and 400V input voltage and at no load and 650V input voltage. Fig. 10(a) shows the output voltage variation at 400V input voltage and different load conditions using the duty cycle as a running parameter. As can be seen, for the critical operating condition, the duty cycle is approximately 75%, which means that more than 20% of the duty cycle is available to compensate a loss in the DC-gain characteristic of the converter.

On the other hand, Fig. 10(b) shows the output voltage variation for 650V input voltage and different load conditions. This graph shows that at a no-load condition, the duty cycle can still be reduced such that it compensates for any over-gain characteristic not considered during the design.

Table I shows the principal parameters obtained from the design of the converter.

TABLE I.

PRINCIPAL PARAMETERS OBTAINED FROM THE DESIGN OF THE CONVERTER.

| Q    | Fn    | F <sub>s</sub><br>KHz | Np | N <sub>aux</sub> | Ns | Qt  | L <sub>r</sub><br>(µH) | Cr<br>(nF) | L <sub>m</sub><br>(µH) |

|------|-------|-----------------------|----|------------------|----|-----|------------------------|------------|------------------------|

| .533 | 0.893 | 775                   | 6  | 2                | 1  | 4.8 | 3.976                  | 9.03       | 60                     |

#### B. Implementation of the Converter

An experimental prototype was built to verify the operation of the proposed converter. In order to reduce the effect of the wide input variation, the solution with partial control in the secondary side and full rectification was implemented in the converter. The power stage shown in Fig. 11 is comprised of the following components.

Figure 10. Output voltage characteristics for different load conditions for (a) 400V and (b) 650V input voltage.

Figure 11. Experimental prototype.

| S <sub>1</sub> - S <sub>4</sub> : APT5015BLC   | C <sub>ss</sub> : 470nF/400V- MKP  |

|------------------------------------------------|------------------------------------|

| S <sub>5</sub> - S <sub>8</sub> : APT20M22LLCX | C <sub>r</sub> : 9nf-4x2.2nf/600V  |

| D <sub>r1</sub> - D <sub>r2</sub> : 30CPQ150   | T <sub>r</sub> : E55-3F3 6/2/1     |

| D <sub>6</sub> - D <sub>7</sub> : 30CPQ150     | L <sub>m</sub> : 60uH              |

| D <sub>5</sub> - D <sub>8</sub> : DSEI60 05A   | L <sub>r</sub> : 3.974uH           |

| D <sub>c1</sub> - D <sub>c2</sub> : DSEI8 06A  | L <sub>lk</sub> - 1.693uH          |

| Cin1-Cin2: 2x330nf/400V MKP                    | L <sub>r</sub> - 2.3uH 6T 783E-3F3 |

For a design at 775 KHz, and taking into account the eventual integration of the passive elements in the converter (transformer, resonant capacitor and resonant inductor) into an LCT structure, it was decided to built a simple transformer with an E55 core. In this case, Litz wire was used for the primary and secondary windings, and they were placed one beside the other in order to reduce the interwinding capacitance of the transformer. It is important to mention that this structure causes the leakage inductance of the transformer to increase to 1.693  $\mu$ H. However, this leakage inductance is absorbed by the resonant inductance. In addition, a small gap was introduced in order to adjust the magnetizing inductance of the transformer to the calculated value (60  $\mu$ H).

In addition, the flying capacitor  $C_{sec}$  is placed across secondary switches  $S_5$  and  $S_8$  to eliminate a possible voltage spike across the secondary switches due to resonance among the reflected leakage inductance to the secondary side, the stray inductance in the secondary side, and the parasitic capacitance of the secondary switches. This capacitor should clamp the voltage across the switches during the instant of turn-on and turn-off. In this case, the ringing across the switches depends on both the parasitic capacitance of the secondary switch and the parasitic stray inductance that occurs due to the layout. Therefore, the stray inductance of the layout should be minimized.

# C. Experimental Results

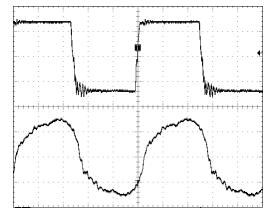

Fig. 12 shows the voltage across the resonant tank  $(V_{ab})$  and the primary resonant current. These waveforms were taken at full-load condition and nominal input voltage; that is, 560V input voltage, 60V output voltage and 42.55A output current. The primary-side layout of the converter was modified in order to measure the current through one of the primary switches. This modification resulted in a resonance across the primary-side voltage.

Figure 12. Experimental results: (a) voltage across the resonant tank (V<sub>ab</sub>) and primary resonant current (200 V/div, 10 A/div, 250 ns/div).

Fig. 13 shows the drain-to-source voltages,  $V_{DS}$ , and the drain current through  $S_3$ , also obtained at nominal input voltage and full-load condition. It can be seen that the maximum voltage for  $S_3$  is 280 V, just half of the input voltage. Also, it can be observed that the voltage falls to zero prior to the turn-on of the switch. Therefore, a ZVS transition is achieved.

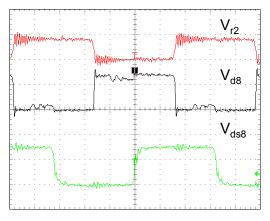

The voltage across the secondary devices at full-load condition can be seen in Fig. 14. This figure shows the voltage across diode rectifiers  $D_{r2}$  and  $D_8$ , and the drain-to-source voltage across switch  $S_8$ . The new layout for the secondary side and the flying capacitor  $C_{sec}$  both help to reduce the voltage spike across the devices. It is important to mention that no snubber circuit is used for the secondary devices.

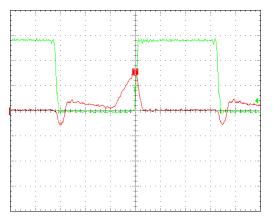

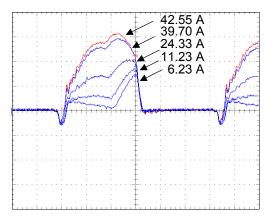

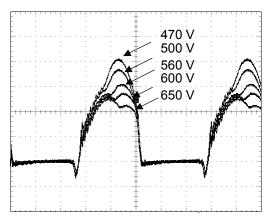

Fig. 15 shows again the drain-to-source voltage,  $V_{DS}$ , and the drain current through  $S_3$ , but at nominal input voltage and low-load condition. It can be observed that ZVS operation is still achieved despite the low-load condition. As explained before, placing the control in the secondary side allows ZVS operation for a wide load range without penalizing the circulating energy, as shown in Fig. 16. This figure shows the drain current through switch  $S_3$  for different load conditions. Fig. 17 shows again the drain current through  $S_3$  at full-load condition and at several input voltages. The circulating energy is almost fixed for any load and input voltage conditions.

Figure 13. Experimental results: drain-to-source voltage and drain current through S<sub>3</sub> (100 V/div, 5 A/div, 250 ns/div).

Figure 14. Experimental results: voltage across  $D_{r2}$ , voltage across  $D_8$ , and drain-to-source voltage across  $S_3$  (75 V/div, 150 V/div, 100 V/div 200 ns/div).

Figure 15. Drain-to-source voltage and drain current through S<sub>3</sub> at low-load condition (100 V/div, 5 A/div, 200 ns/div).

Figure 16. Drain current through S<sub>3</sub> for different load conditions and nominal input voltage (5 A/div, 200 ns/div).

Figure 17. Drain current through S<sub>3</sub> at full load and different input voltage conditions (5 A/div, 250 ns/div).

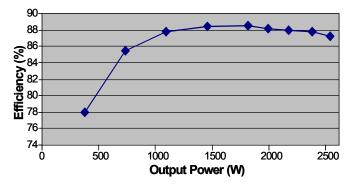

The experimental measured efficiency as a function of the output power at nominal input voltage 560 V is shown in Fig. 17. The efficiency at the full-load condition is 87.23%, and the maximum efficiency of the converter, which occurs around 1820 W, is 88.51%.

Figure 18. Efficiency curve for the proposed converter at nominal input voltage.

#### VII. CONCLUSION

A novel fixed-frequency ZVS three-level LLC resonant DC/DC converter was presented in this paper. The operating stages and characteristics of the proposed converter were presented. Experimental results of a 2.75 KW prototype were shown in order to verify the operation of the converter

It was shown that by using the energy in the magnetizing inductance of the transformer and placing the control in the secondary side of the converter, it can be achieved ZVS for a wide load range without increasing the circulating energy in the converter. In addition, this paper presented some solutions for reducing the impact of the wide input voltage variations on the performance of the converter. These characteristics make the proposed converter an interesting option for high-voltage, high-power applications that require high power density and high efficiency.

#### References

- R. Steigerwald, "A Comparison of Half-Bridge Resonant Converter Topologies," *in IEEE Trans. on Power Electronics*, Vol. 3, No. 2, pp. 174-182, April 1988.

- [2] R. Severns, "Topologies for Three Elements Resonant Converters," in IEEE APEC Rec., 1990, pp. 712-722.

- [3] B. Jacobson and R. DiPerna, "Series Resonant Converter with Clamped Tank Capacitor Voltage," in IEEE APEC Rec., 1990, pp. 137-146.

- [4] R. Steigerwald W. Roshen, and C. Saj, "A High-Density 1 kW Resonant Power Converter with Transient Boost Function," *in IEEE Trans. on Power Electronics*, Vol. 8, No. 4, pp. 431-438, October 1993.

- [5] J. Sabate, and F. Lee, "Off-Line Applications of the Fixed-Frequency Clamped-Mode Series Resonant Converter," in *IEEE Trans. on Power Electronics*, Vol 6, pp. 39-47, January 1991.

- [6] A. K. S Bhat "Analysis and Design of LCL-Type Series Resonant Converter," in IEEE Trans. on Industrial Electronics, Vol. 41, No. 1, pp. 118 – 124, February 1994.

- [7] G. Raju and S. Doradla, "An LCL Resonant Converter with PWM Control – Analysis, Simulation, and Implementation," *in IEEE Trans. on Power Electronics*, Vol. 10, No. 2, pp. 164-174, March 1995.

- [8] J. Renes Pinheiro and Ivo Barbi, "The Three-Level ZVS PWM Converter A New Concept in High-Voltage DC-To-DC Conversion," in IEEE IECON Rec., 1992, pp. 173-178.

- [9] R. Ayyanar and N. Mohan, "A Novel Full-Bridge DC-DC Converter for Battery Charging Using Secondary-Side Control Combines Soft Switching Over the Full Load Range and Low Magnetics Requirement," *in IEEE Trans. on Industry Applications*, Vol. 37, No. 2, pp. 559-565, March/April 2001.

- [10] M. A. de Rooij and J.D. van Wyk, "Design Procedure for a Minimum Volume Low-Loss Integrated LCT Structure for a 2.7 kW Series Load Resonant DC to DC Converter," CPES, Internal Report, July 2001.